处理器总线时序和系统总线.ppt

YY****。。

亲,该文档总共42页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

处理器总线时序和系统总线.pptx

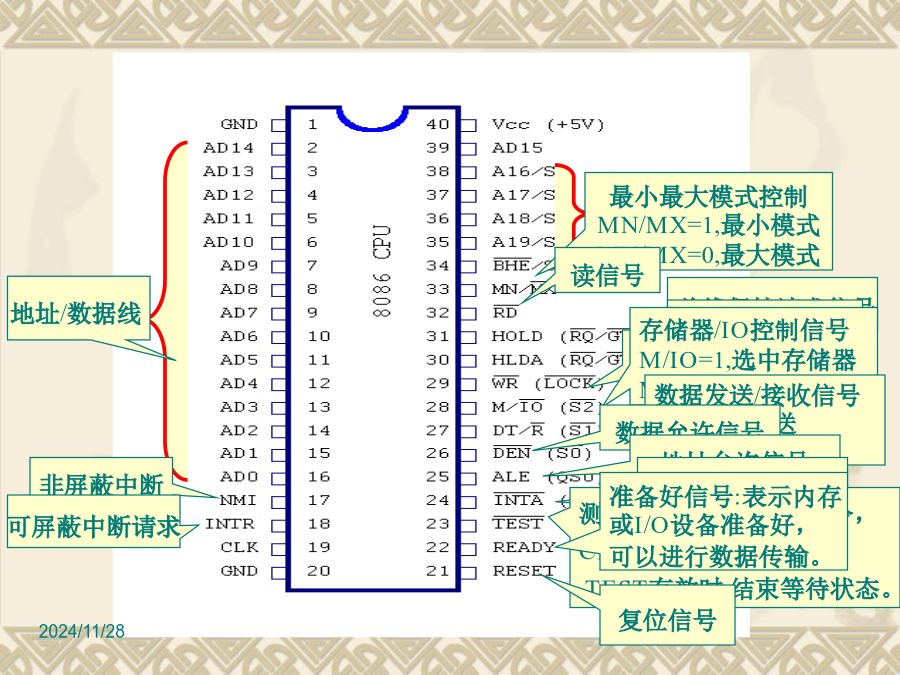

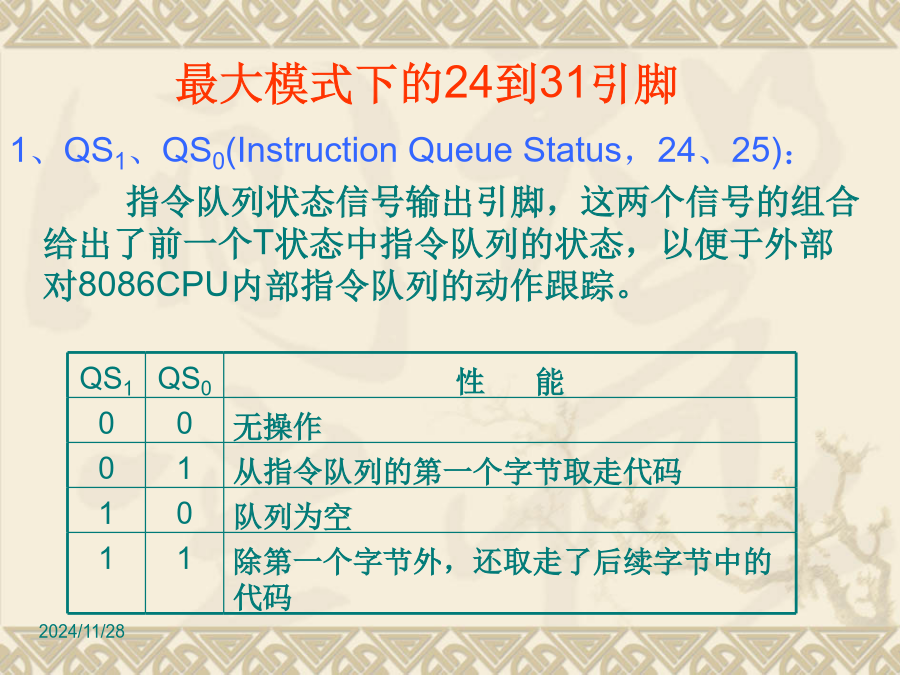

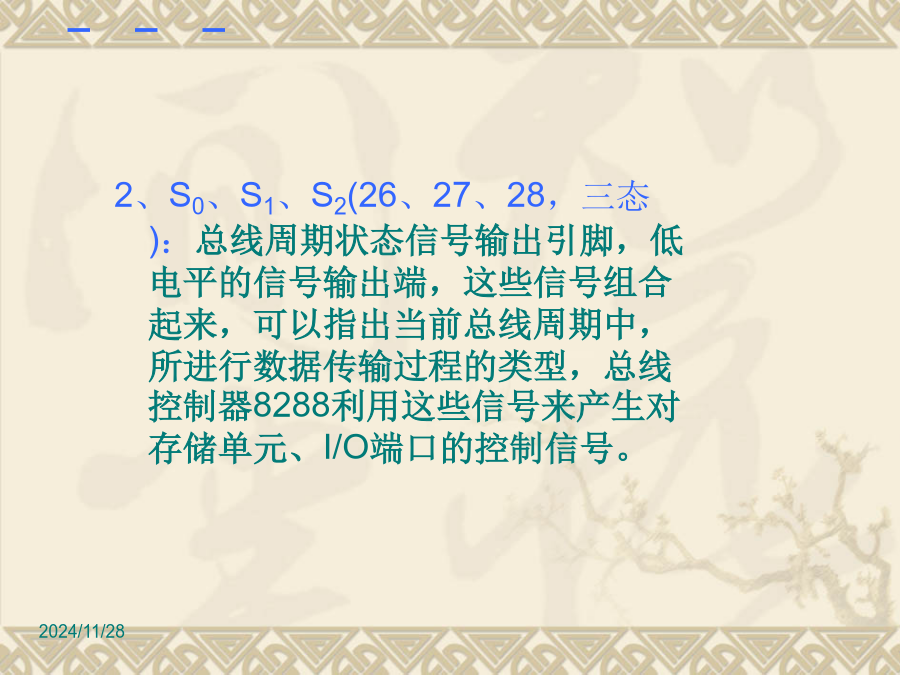

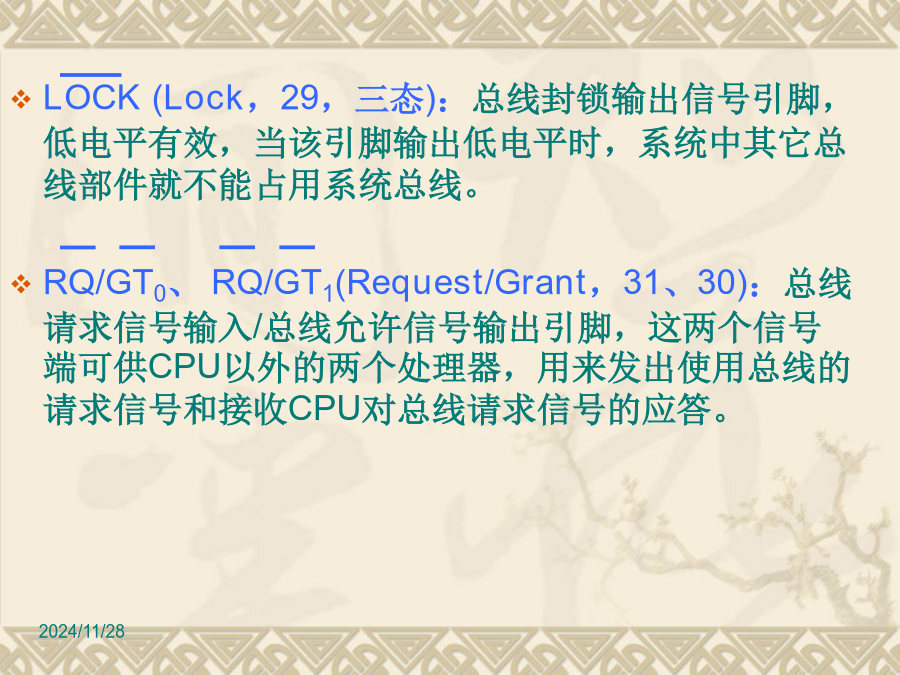

本章讲述:5.18086的引脚功能5.28086处理器时序5.3系统总线5.18086的引脚功能1.最小模式目前常用的是最大组态。要求有较强的驱动能力。此时8086要通过一组总线控制器8288来形成各种总线周期,控制信号由8288供给,如图5-1所示。/最小模模式的引脚信号(2)地址/状态信号线A19/S6~A16/S3S4、S3的组合指出当前使用的段码寄存器情况(3)BHE/S7高8位数据总线允许/状态线BHE和A0结合控制CPU与存储器之间数据传送的格式。(4)MN/MX最大/最小模式控制信号。(6)

处理器总线时序和系统总线.ppt

第五章处理器总线时序和系统总线最大模式此模式是相对最小模式而言的;此时系统中有两个或多个微处理器,其中一个是主处理器8086,其它的处理器称为协处理器,它们协助主处理器工作。2、8086的引脚功能8086CPU采用双列直插式的封装形式,具有40条引脚。8086地址线20位,数据线16位,采用分时复用的地址/数据总线,有一部分引脚具有双重功能。AD0~AD15(三态双向):地址数据公用线,内部采用多路开关切换。A16~A19(三态输出):在访问存储器操作时,作为地址的高四位;在访问外设操作时,这些地址不用。

处理器总线时序和系统总线.ppt

第五章处理器总线时序和系统总线学习目的重点5.18086的引脚功能8086引脚特性:8086有16位数据线,与地址线A0-A15兼用;20位地址线,寻址空间达到1MB;引脚分类地址总线、数据总线、控制总线地址/数据线8086CPU的两种组态最小组态(模式)MN/MX接+5V构成小规模的应用系统,只有8086一个微处理器,所有的总线控制信号均为8086产生,系统中的总线控制逻辑电路,减少到最少。最大组态(模式)MN/MX接地。用于大型(中型)8086/8088系统中,系统总是包含有两个或多个微处理器,其中一

第--章--处理器总线时序和系统总线优秀文档.ppt

第5章处理器总线时序和系统总线5.1处理器总线5.3处理器时序5.4系统总线5.1处理器总线5.1.1微处理器的引脚功能5.1处理器总线5.1.1微处理器的引脚功能最小组态最大组态2.8086CPU的引线8086微处理器的引线如图。8086最小组态的24-31引脚8086CPU的引线地址锁存允许信号,高电平有效⑦HOLD(输入)/HLDA(输出)不同指令其指令周期不等长,最短执行时间是两个时钟周期。(2)输入输出端口的读或写总线周期;总线请求/总线响应信号控制总线是传送控制信号的总线。(2)片总线把各种不

第五章微处理器总线时序和系统总线介绍.ppt

第五章处理器总线时序和系统总线本章讲纲第一节基本概念第一节基本概念第一节基本概念第一节基本概念第一节基本概念第一节基本概念第一节基本概念第一节基本概念第一节基本概念第一节基本概念第一节基本概念第一节基本概念第二节8086的引脚功能及操作时序第二节8086的引脚功能及操作时序VCCA15A16/S3A17/S4A18/S5A19/S6SSOMN/MXRDHOLDHLDAWRIO/MDT/RDENALEINTATESTREADYRESETVCCA15A16/S3A17/S4A18/S5A19/S6SSOMN/