接合垫结构以及集成电路芯片.pdf

论文****轩吖

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

接合垫结构以及集成电路芯片.pdf

本发明提供一种接合垫结构以及一种集成电路芯片。所述接合垫结构包括第一金属层、位于所述第一金属层上方的第二金属层、位于所述第一金属层以及所述第二金属层之间的介电层以及介层孔图案。所述介层孔图案设置于所述介电层中且电性连接于所述第一金属层以及所述第二金属层。所述介层孔图案包括至少一第一介层孔组以及与其相邻的至少一第二介层孔组。所述第一介层孔组具有H型的轮廓,且所述第二介层孔组也具有H型的轮廓,其方向异于所述第一介层孔组的所述H型的轮廓。

集成电路装置、整合系统以及测试接合垫的方法.pdf

本发明公开了一种集成电路装置、整合系统以及测试集成电路装置上的接合垫的方法。其中,该集成电路装置包含集成电路、多个第一类型接合垫以及多个第二类型接合垫。多个第一类型接合垫中的每一者电连接至集成电路且被配置为电连接至对应外部集成电路装置。多个第二类型接合垫中的每一者被配置为不与对应外部集成电路装置电连接。多个第一类型接合垫中的每一者被配置为电连接至多个第二类型接合垫中的对应一者。多个第一类型接合垫的数目可大于多个第二类型接合垫的数目。多个第二类型接合垫中的每一者可比多个第一类型接合垫中的每一者具有用于探测的

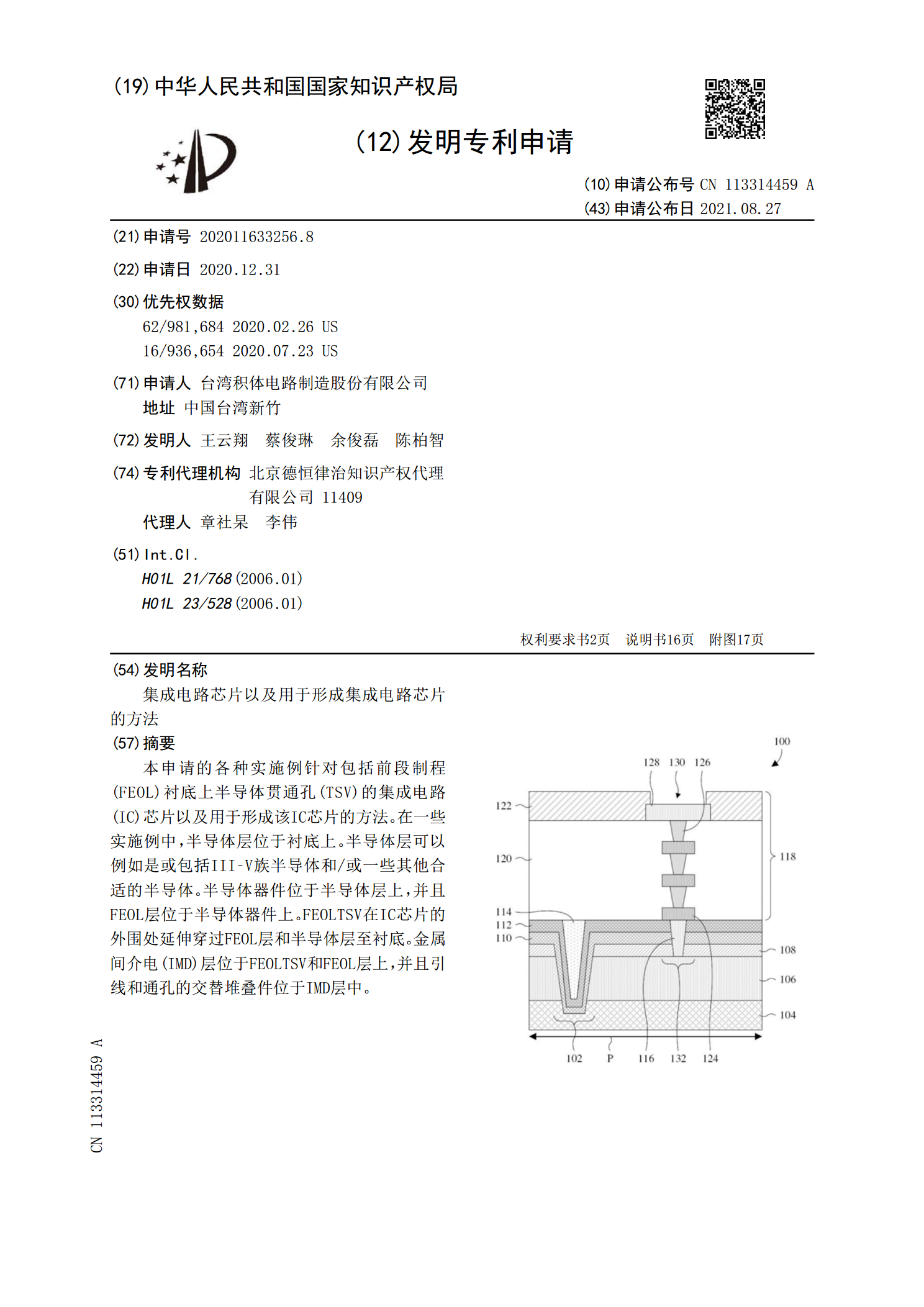

集成电路芯片以及用于形成集成电路芯片的方法.pdf

本申请的各种实施例针对包括前段制程(FEOL)衬底上半导体贯通孔(TSV)的集成电路(IC)芯片以及用于形成该IC芯片的方法。在一些实施例中,半导体层位于衬底上。半导体层可以例如是或包括III‑V族半导体和/或一些其他合适的半导体。半导体器件位于半导体层上,并且FEOL层位于半导体器件上。FEOLTSV在IC芯片的外围处延伸穿过FEOL层和半导体层至衬底。金属间介电(IMD)层位于FEOLTSV和FEOL层上,并且引线和通孔的交替堆叠件位于IMD层中。

芯片接合装置及芯片接合方法.pdf

本发明提供芯片接合装置及芯片接合方法,能够减少焊锡接合部中的空隙、界面的接合不良。在通过焊锡将半导体芯片接合在引线框架或衬底上的芯片接合机中,具有:输送部,其输送上述引线框架或衬底;焊锡供给部,其向上述引线框架或衬底上供给焊锡;搭载部,其将半导体芯片搭载、接合在上述引线框架或衬底上的焊锡上。所述芯片接合机还具有表面清洁化单元。将上述焊锡供给到上述引线框架或衬底上之后,所述表面清洁化单元除去在炉内熔融的焊锡表面的氧化膜。通过上述芯片接合设备,能够提高芯片接合品质。

集成电路芯片封装结构.pdf

集成电路芯片封装结构全文共四篇示例,供读者参考第一篇示例:集成电路芯片封装结构是指将制造好的芯片封装在外部保护壳体中,以保护芯片免受外界环境的影响。封装是集成电路芯片制造过程中的最后一道工序,它直接影响到芯片的稳定性、可靠性和性能。不同的封装结构具有不同的特点和适用场景,下面将对常见的集成电路芯片封装结构进行详细介绍。一、单晶片封装单晶片封装是一种最简单的封装结构,它将芯片直接封装在一个封装体中。这种封装结构在芯片面积较小、功耗较低的集成电路中常见。由于单晶片封装没有额外的引脚和连接线路,因此具有较小的封