多芯片封装(MCP)芯片悬空的受力分析及优化设计的开题报告.docx

快乐****蜜蜂

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

多芯片封装(MCP)芯片悬空的受力分析及优化设计的开题报告.docx

多芯片封装(MCP)芯片悬空的受力分析及优化设计的开题报告一、选题背景多芯片封装(MCP)技术是一种集成度高、体积小、功耗低、性能优越的芯片封装技术。MCP技术在电子产品中的应用越来越广泛,如智能手机、平板电脑、数字相机、便携式娱乐设备等。MCP技术的应用在不断地扩展,对芯片封装的要求也越来越高。由于MCP技术的多芯片组装,芯片封装过程对各个芯片的位置精度、悬空距离、封装条件等都有很高的要求。这使得设计多芯片封装的成本变得非常高,同时在使用过程中,多芯片封装所涉及的受力问题也将成为芯片封装可靠性和稳定性的

基于多芯片封装SoC的可测试性设计的开题报告.docx

基于多芯片封装SoC的可测试性设计的开题报告一、课题背景随着电子产品制造技术的不断发展,工业界对于芯片封装技术的要求越来越高。多芯片封装方案因为具有体积小、高集成度、低功耗等优势,也受到越来越多的关注。与传统的单芯片封装不同,多芯片封装方案将多个芯片封装在同一个封装中,有效缩小封装体积同时增加了芯片的集成度。因此,多芯片封装SoC正在普及并越来越受到欢迎。在多芯片封装SoC中,芯片之间的通信、数据流转和功耗管理等问题变得尤为重要。由于多个芯片之间的相互影响,如何保证芯片的可测试性设计,已经成为当前多芯片封

多芯片堆叠封装方法及多芯片堆叠封装体.pdf

本发明提供一种多芯片堆叠封装方法及多芯片堆叠封装体,本发明的优点在于采用重布线层与导电柱的联合的方式实现叠层芯片之间的互联,取代传统堆叠芯片封装常用的打线工艺和基板倒装的工艺,相比传统芯片叠层BGA封装,整体封装厚度更薄,相同芯片数量下封装尺寸小,具有良好的导电性、导热性和可靠性。

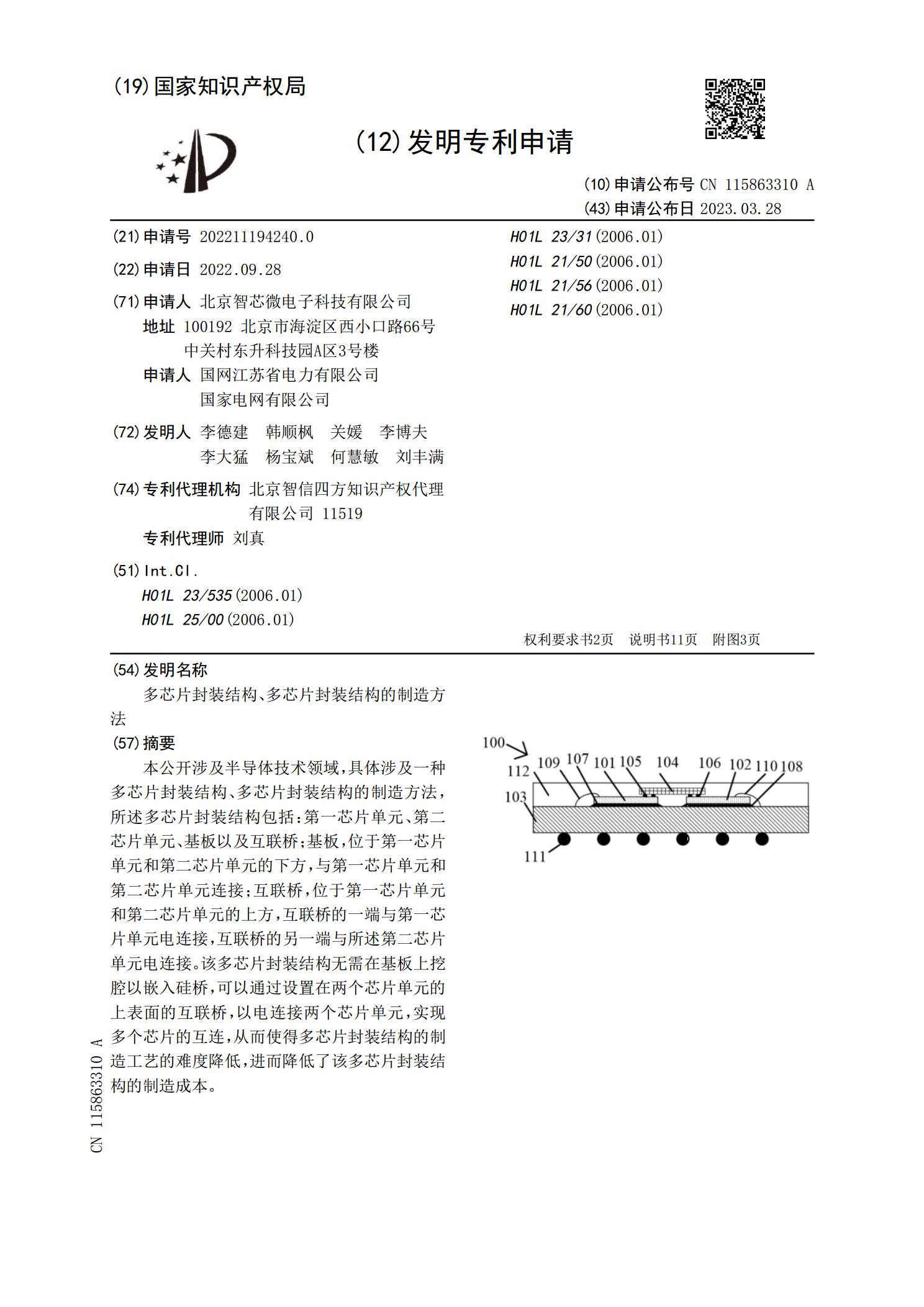

多芯片封装结构、多芯片封装结构的制造方法.pdf

本公开涉及半导体技术领域,具体涉及一种多芯片封装结构、多芯片封装结构的制造方法,所述多芯片封装结构包括:第一芯片单元、第二芯片单元、基板以及互联桥;基板,位于第一芯片单元和第二芯片单元的下方,与第一芯片单元和第二芯片单元连接;互联桥,位于第一芯片单元和第二芯片单元的上方,互联桥的一端与第一芯片单元电连接,互联桥的另一端与所述第二芯片单元电连接。该多芯片封装结构无需在基板上挖腔以嵌入硅桥,可以通过设置在两个芯片单元的上表面的互联桥,以电连接两个芯片单元,实现多个芯片的互连,从而使得多芯片封装结构的制造工艺的

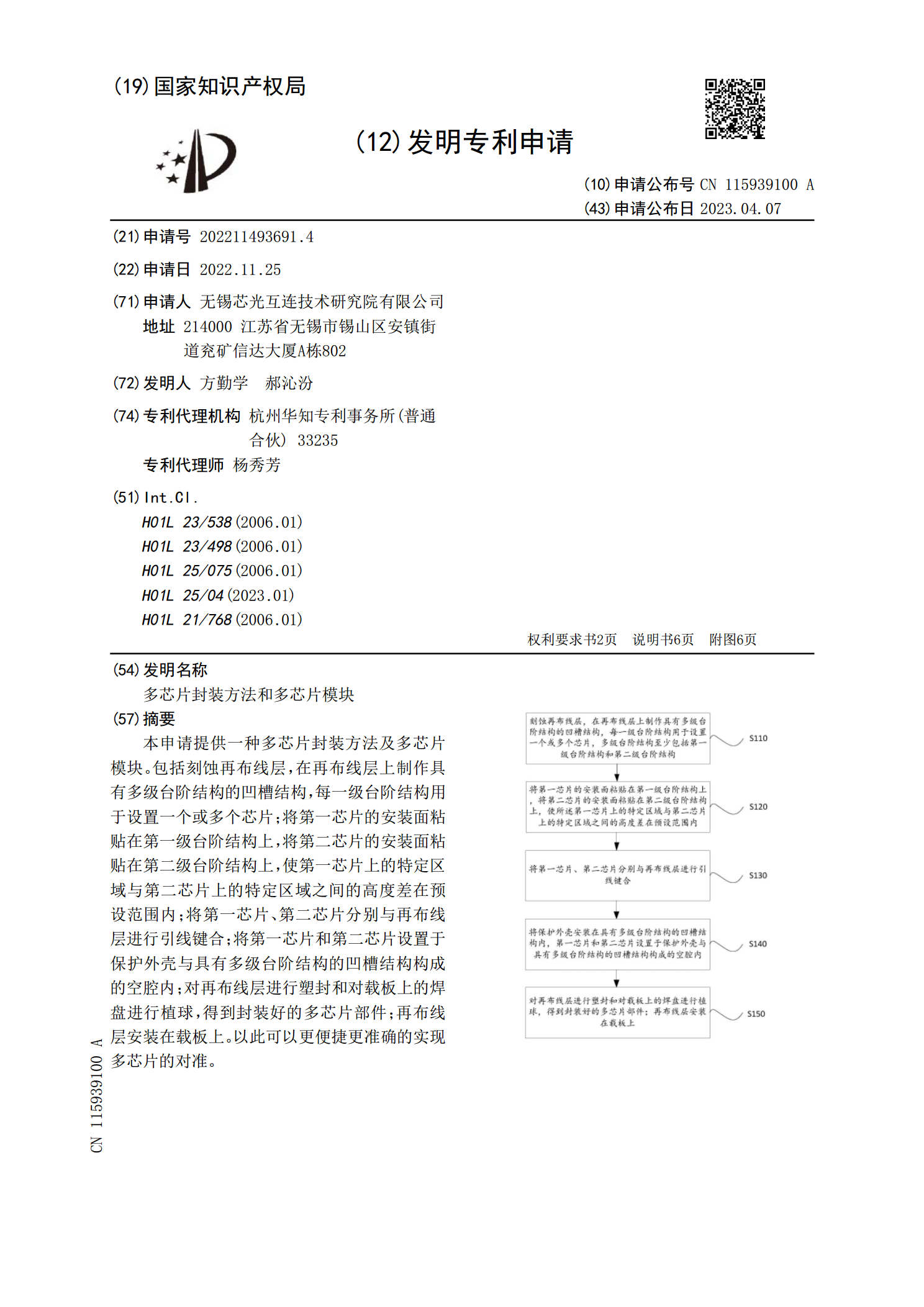

多芯片封装方法和多芯片模块.pdf

本申请提供一种多芯片封装方法及多芯片模块。包括刻蚀再布线层,在再布线层上制作具有多级台阶结构的凹槽结构,每一级台阶结构用于设置一个或多个芯片;将第一芯片的安装面粘贴在第一级台阶结构上,将第二芯片的安装面粘贴在第二级台阶结构上,使第一芯片上的特定区域与第二芯片上的特定区域之间的高度差在预设范围内;将第一芯片、第二芯片分别与再布线层进行引线键合;将第一芯片和第二芯片设置于保护外壳与具有多级台阶结构的凹槽结构构成的空腔内;对再布线层进行塑封和对载板上的焊盘进行植球,得到封装好的多芯片部件;再布线层安装在载板上。