曝光装置以及曝光装置的对准方法.pdf

是你****平呀

亲,该文档总共15页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

曝光装置以及曝光装置的对准方法.pdf

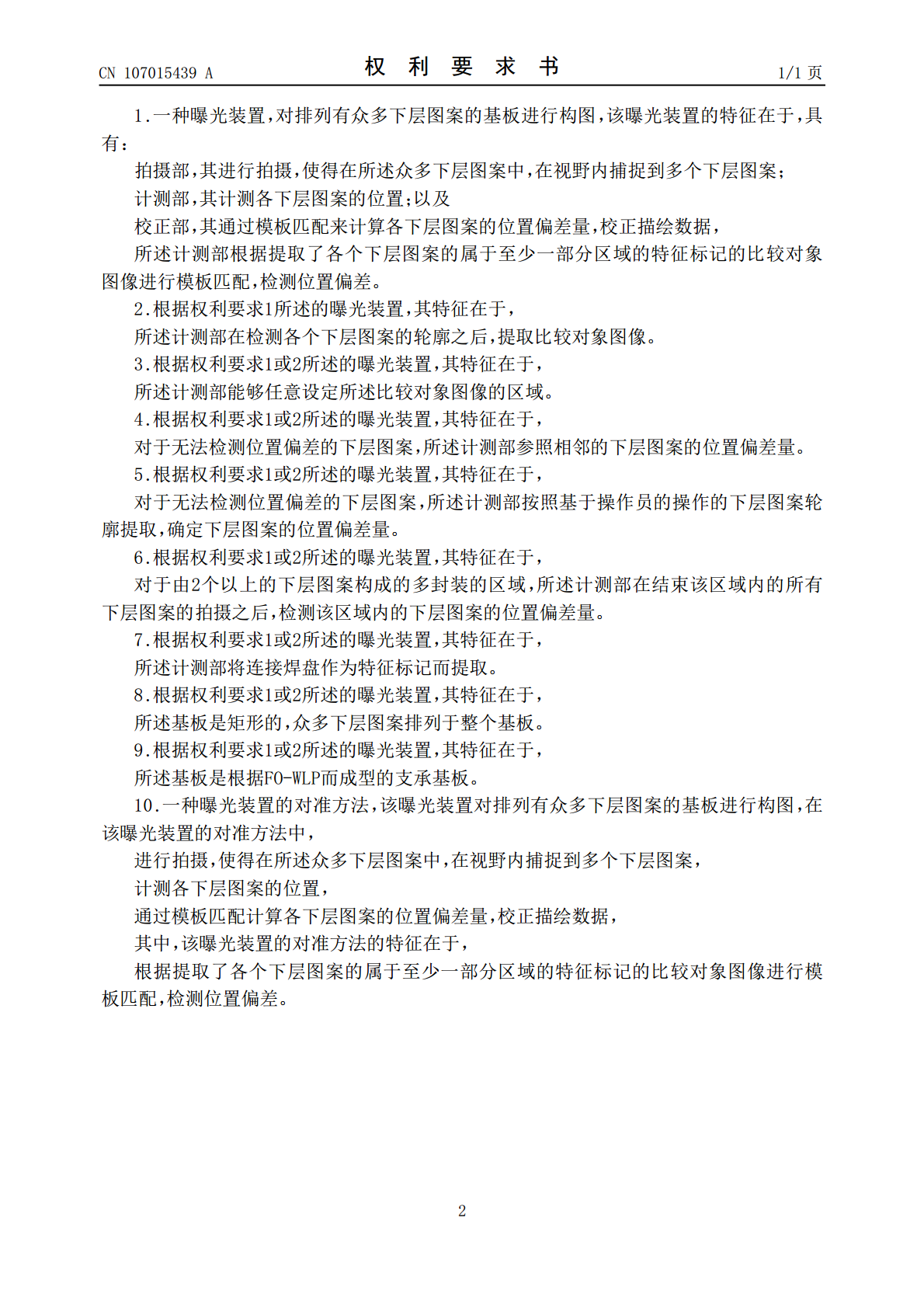

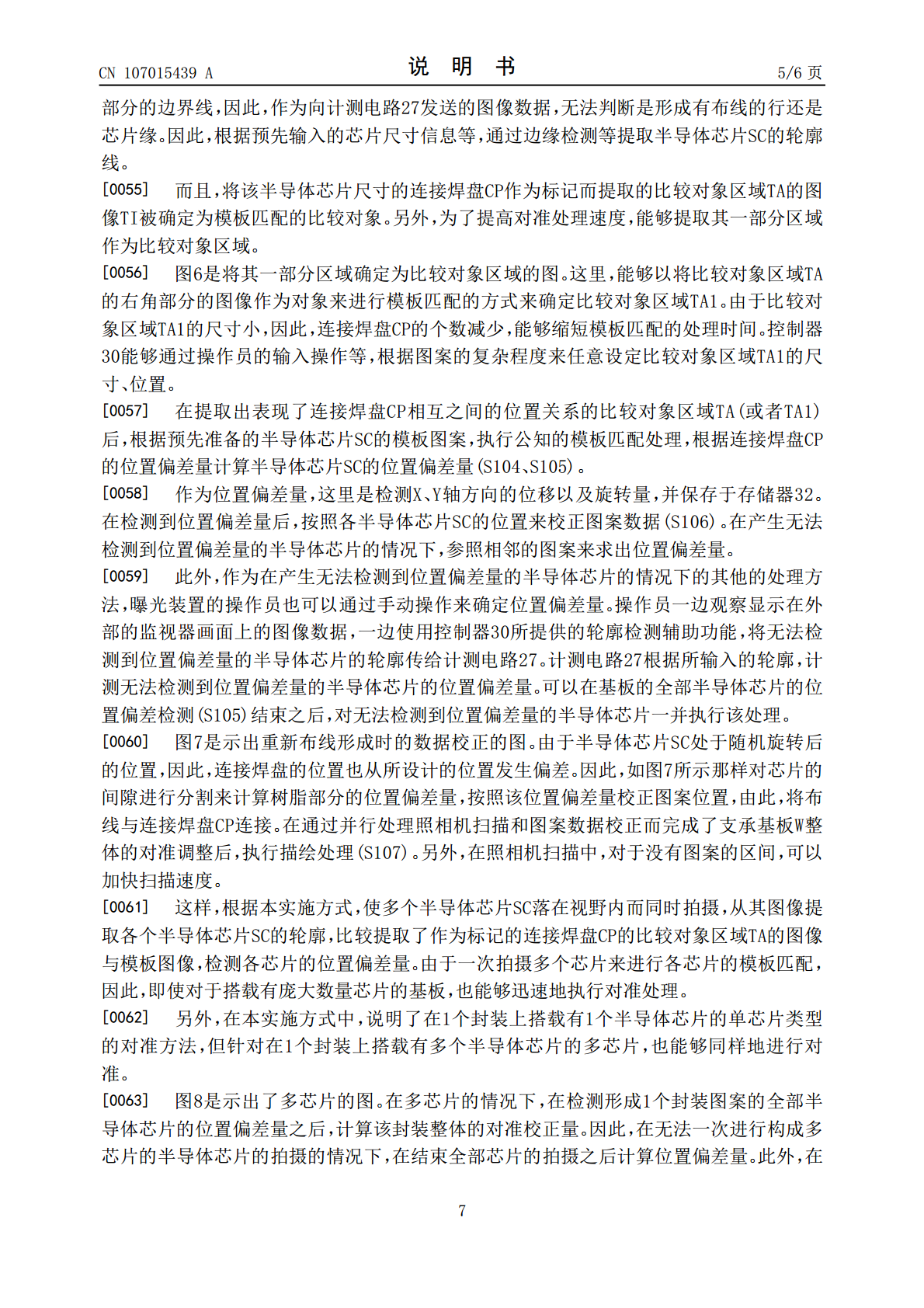

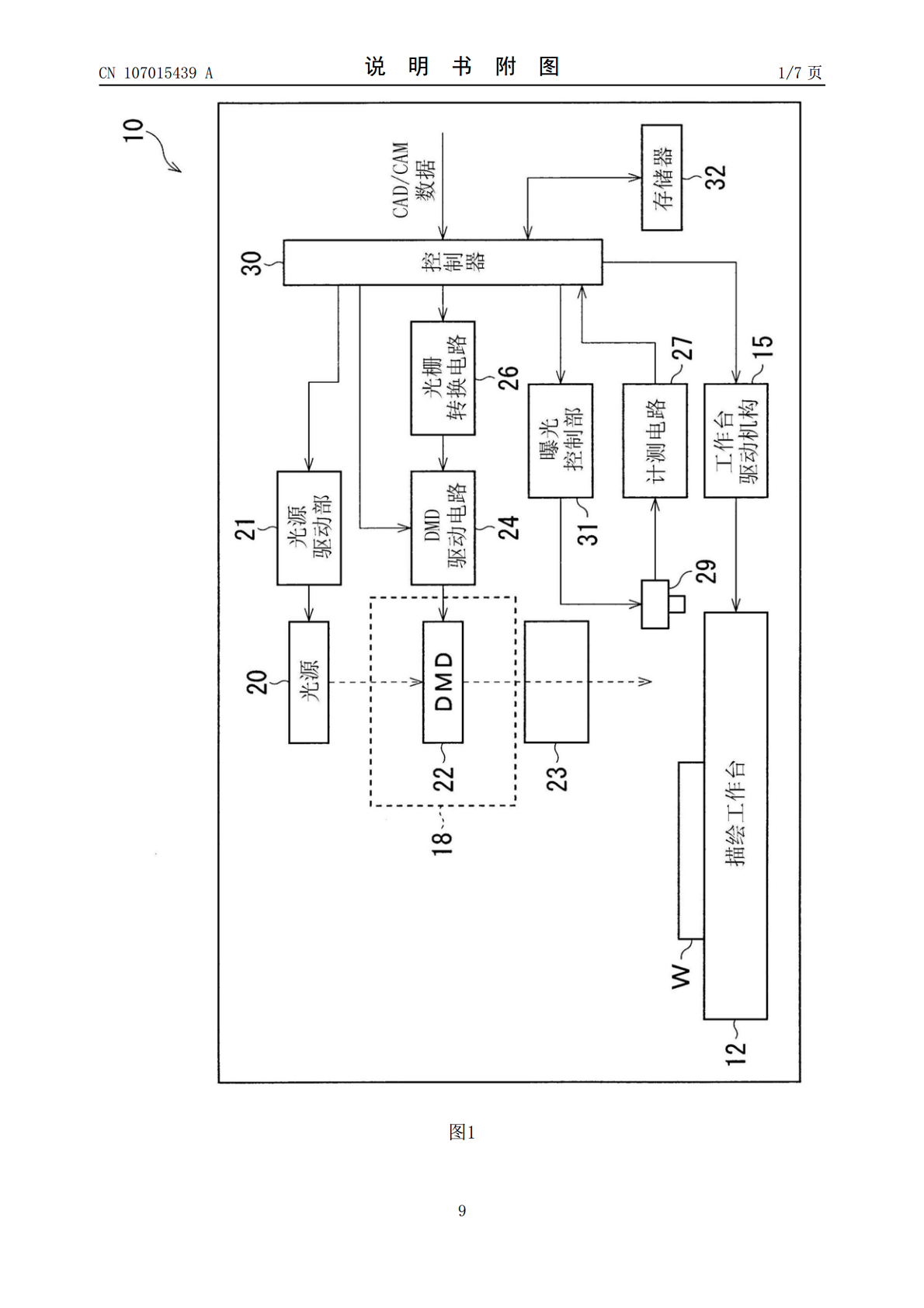

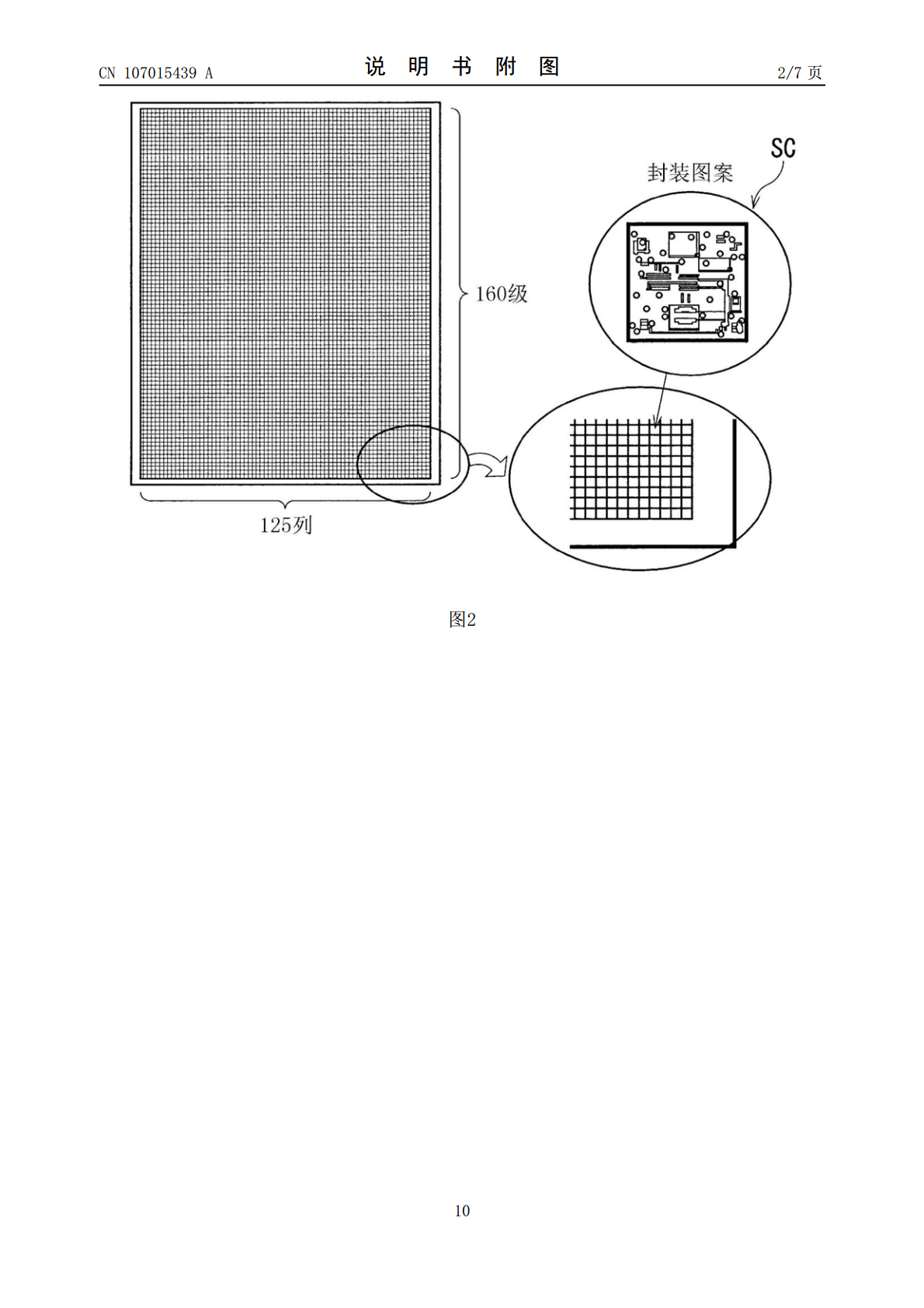

曝光装置以及曝光装置的对准方法,即使对配设有众多图案的基板,也迅速且准确地进行对准。曝光装置具有对准所使用的照相机(29)和DMD(22),能够按照FO‑WLP形成图案,在该曝光装置中,使多个半导体芯片(SC)落在视野内而同时拍摄,从其图像提取各个半导体芯片(SC)的轮廓,将提取了作为标记的连接焊盘(CP)的比较对象区域(TA)的图像与模板图像进行比较,检测各芯片的位置偏差量。

接近式曝光装置以及接近式曝光方法.pdf

接近式曝光装置包括:平面镜(68),具有能够校正曲率的镜变形单元(70);CCD摄像机(30),能够拍摄掩模M侧的对准标记(Ma)和工件(W)侧的对准标记(Wa);存储部(91),存储根据在对第一层的掩模(M)的图案进行曝光时照射到工件(W)的主光线(EL)的角度和掩模(M)及工件(W)间的间隙计算的对准标记(Wa)的初始偏移分量;以及控制装置(90),在对第二层以后的掩模(M)的图案进行曝光时,利用对于由CCD摄像机(30)观测的工件(W)侧的对准标记(Wa)补偿初始偏移分量而得到的工件(W)侧的校正对

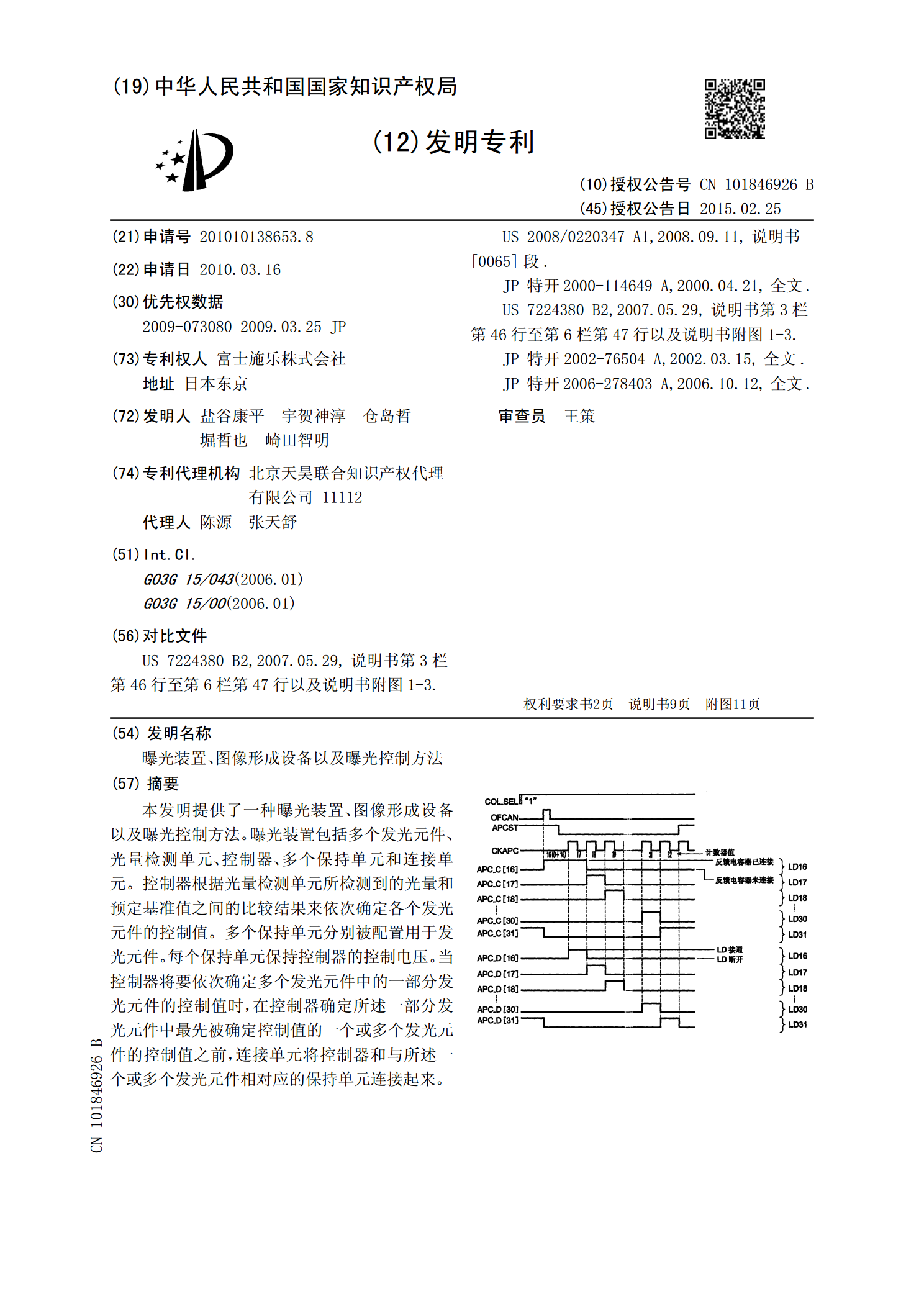

曝光装置、图像形成设备以及曝光控制方法.pdf

本发明提供了一种曝光装置、图像形成设备以及曝光控制方法。曝光装置包括多个发光元件、光量检测单元、控制器、多个保持单元和连接单元。控制器根据光量检测单元所检测到的光量和预定基准值之间的比较结果来依次确定各个发光元件的控制值。多个保持单元分别被配置用于发光元件。每个保持单元保持控制器的控制电压。当控制器将要依次确定多个发光元件中的一部分发光元件的控制值时,在控制器确定所述一部分发光元件中最先被确定控制值的一个或多个发光元件的控制值之前,连接单元将控制器和与所述一个或多个发光元件相对应的保持单元连接起来。

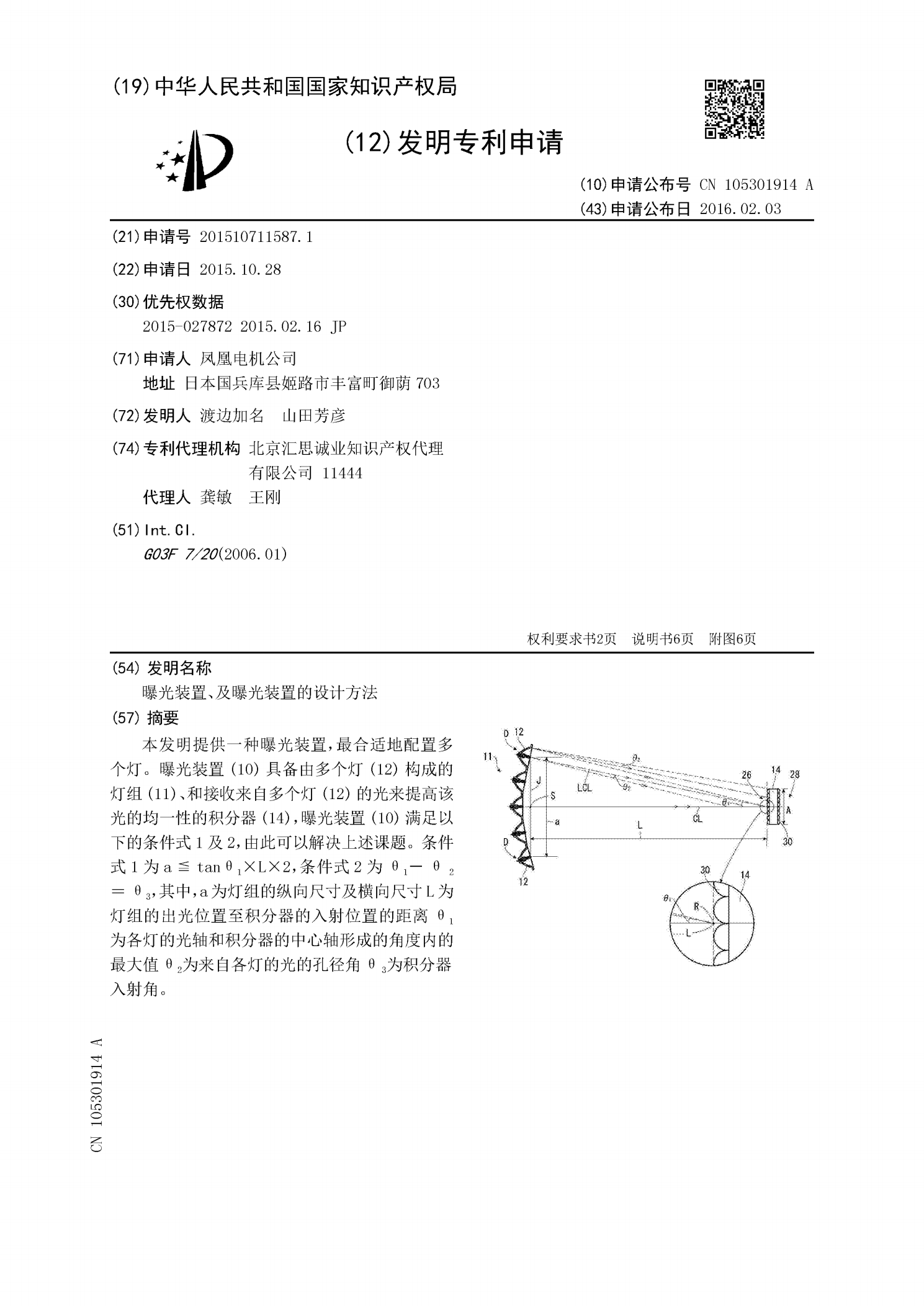

曝光装置、及曝光装置的设计方法.pdf

本发明提供一种曝光装置,最合适地配置多个灯。曝光装置(10)具备由多个灯(12)构成的灯组(11)、和接收来自多个灯(12)的光来提高该光的均一性的积分器(14),曝光装置(10)满足以下的条件式1及2,由此可以解决上述课题。条件式1为a≦tanθ1×L×2,条件式2为θ1-θ2=θ3,其中,a为灯组的纵×21尺寸及横×21尺寸L为灯组的出光位置至积分器的入射位置的距离θ1为×08灯的光轴和积分器的中心轴形成的角度内的最大值θ2为来自×08灯的光的孔径角θ3为积分器入射角。

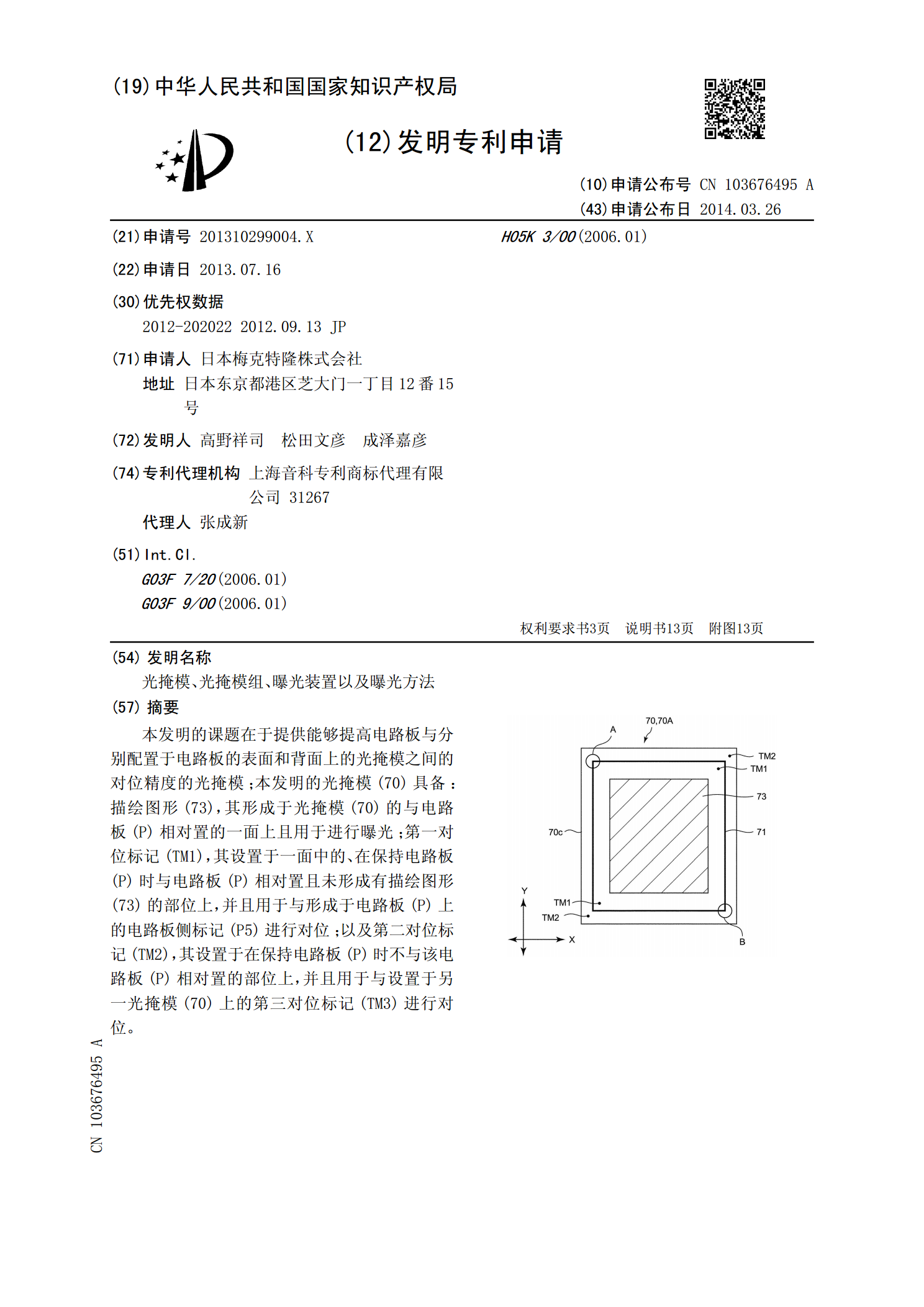

光掩模、光掩模组、曝光装置以及曝光方法.pdf

本发明的课题在于提供能够提高电路板与分别配置于电路板的表面和背面上的光掩模之间的对位精度的光掩模;本发明的光掩模(70)具备:描绘图形(73),其形成于光掩模(70)的与电路板(P)相对置的一面上且用于进行曝光;第一对位标记(TM1),其设置于一面中的、在保持电路板(P)时与电路板(P)相对置且未形成有描绘图形(73)的部位上,并且用于与形成于电路板(P)上的电路板侧标记(P5)进行对位;以及第二对位标记(TM2),其设置于在保持电路板(P)时不与该电路板(P)相对置的部位上,并且用于与设置于另一光掩模(