制作半导体装置的沟槽结构的干式蚀刻方法.pdf

书生****12

亲,该文档总共13页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

制作半导体装置的沟槽结构的干式蚀刻方法.pdf

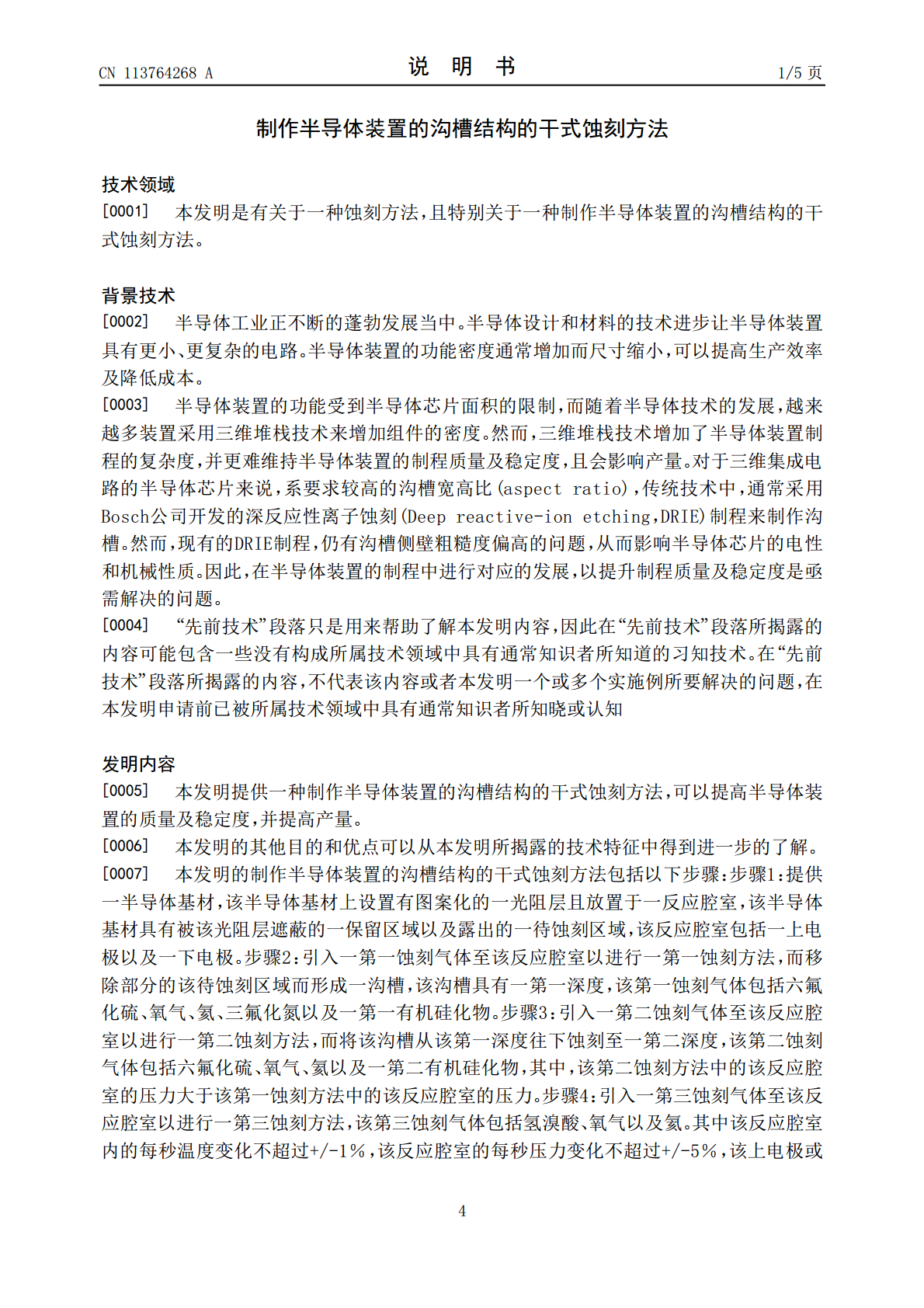

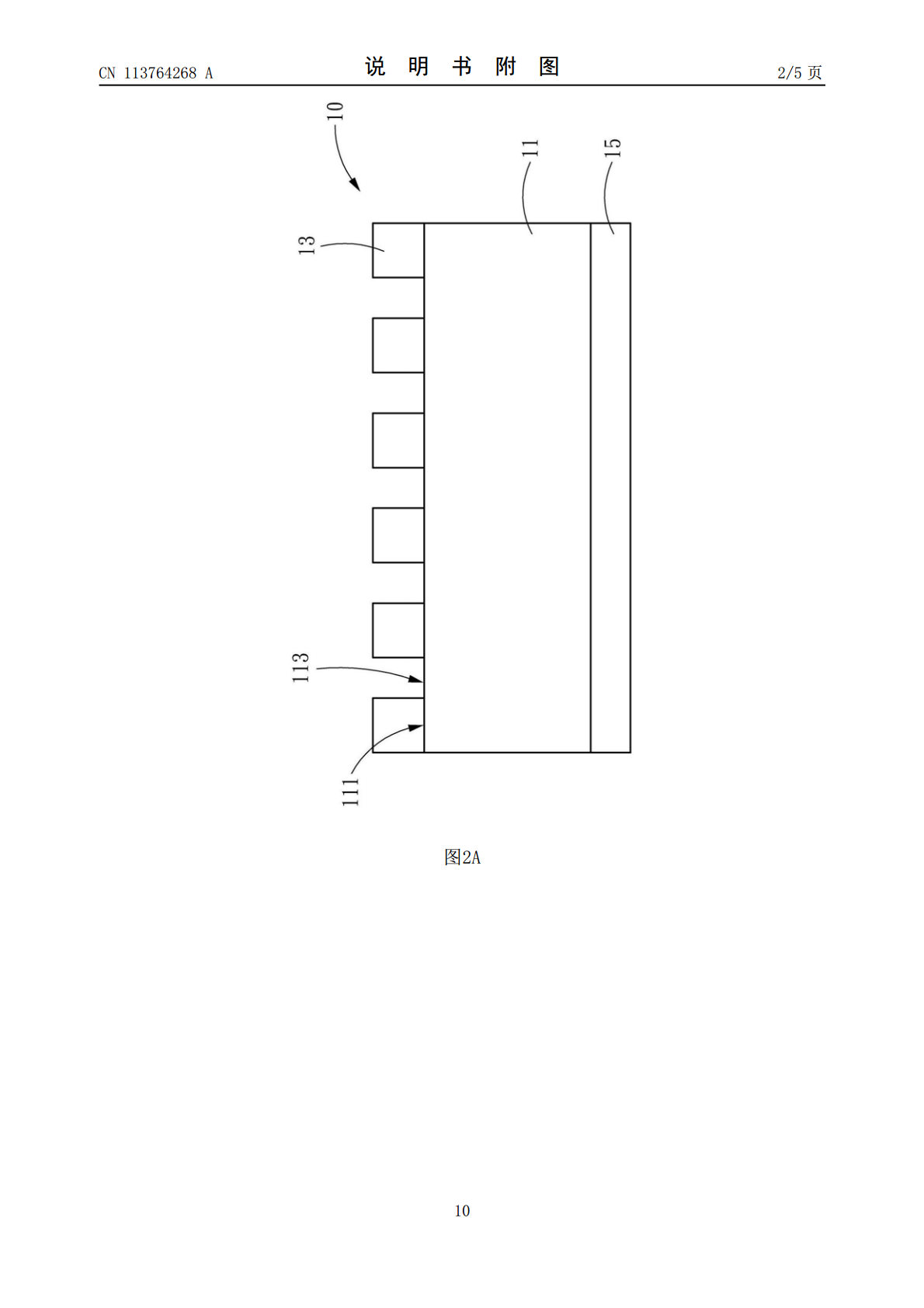

本发明涉及制作半导体装置的沟槽结构的干式蚀刻方法。所述干式蚀刻方法包括以下步骤:步骤1:提供半导体基材。半导体基材上设置有图案化的光阻层且放置于反应腔室。步骤2:引入第一蚀刻气体至反应腔室以进行第一蚀刻方法,而形成沟槽。第一蚀刻气体包括六氟化硫、氧气、氦、三氟化氮以及第一有机硅化物。步骤3:引入第二蚀刻气体至反应腔室以进行第二蚀刻方法,而将沟槽往下蚀刻。第二蚀刻气体包括六氟化硫、氧气、氦以及第二有机硅化物。步骤4:引入第三蚀刻气体至反应腔室以进行第三蚀刻方法。第三蚀刻气体包括氢溴酸、氧气以及氦。

沟槽隔离结构的制作方法、半导体器件.pdf

本发明提供一种沟槽隔离结构的制作方法以及一种半导体器件。所述制作方法对于基片上较窄的一类沟槽和较宽的二类沟槽,先用牺牲层覆盖在预处理基片的上表面以及一类沟槽上并露出二类沟槽,在形成第一填充介质并进行第一平坦化工艺时,利用牺牲层作为终止层去掉牺牲层上的第一填充介质,然后去除牺牲层,在形成第二填充介质时,由于保留在二类沟槽内的第一填充介质抬高了二类沟槽的底表面,所述第二填充介质位于二类沟槽区域的上表面高于其位于一类沟槽区域的上表面,在执行第二平坦化工艺时,二类沟槽区域的研磨量较一类沟槽区域大,可以改善现有沟槽

半导体元器件的干蚀刻方法.pdf

本发明中公开了一种半导体元器件的干蚀刻方法,该方法包括:在硅基底材料上依次形成SiO2层、低介电常数绝缘材料层、顶层、含Si的底部抗反射层和光阻层;对含Si的底部抗反射层和光阻层进行蚀刻后,对顶层和低介电常数绝缘材料层进行蚀刻,并去除蚀刻过程中产生的残留物;对由于进行所述蚀刻后而暴露出的顶层进行氟气处理,使得在对顶层进行蚀刻的同时不对顶层之下的低介电常数材料进行蚀刻;去除对顶层进行蚀刻时所产生的残留物。通过使用上述的半导体元器件的干蚀刻方法,解决了顶部收缩和弓形轮廓的问题,使得所形成的顶层具有较好的轮廓,

半导体结构及浅沟槽隔离结构制备方法.pdf

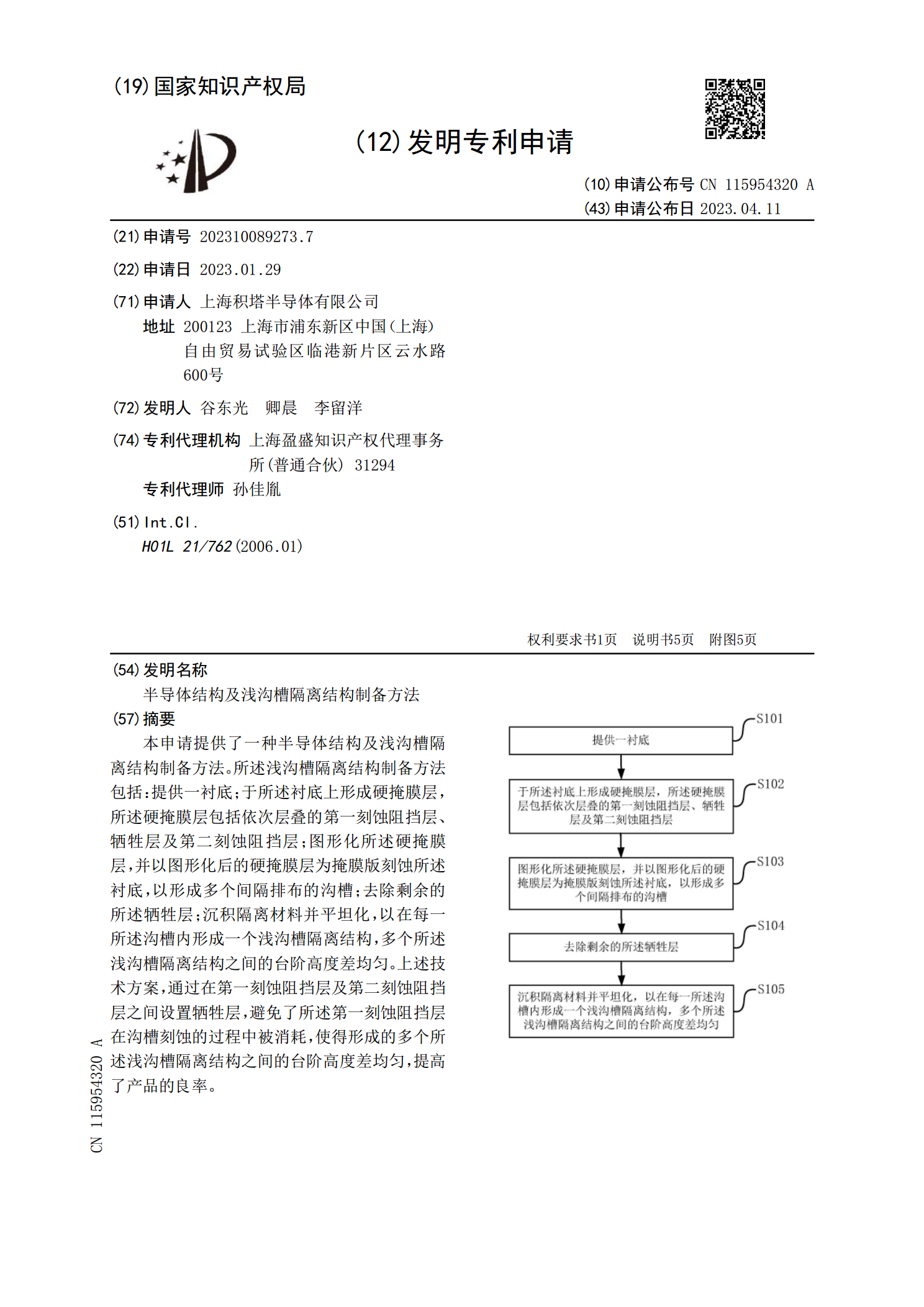

本申请提供了一种半导体结构及浅沟槽隔离结构制备方法。所述浅沟槽隔离结构制备方法包括:提供一衬底;于所述衬底上形成硬掩膜层,所述硬掩膜层包括依次层叠的第一刻蚀阻挡层、牺牲层及第二刻蚀阻挡层;图形化所述硬掩膜层,并以图形化后的硬掩膜层为掩膜版刻蚀所述衬底,以形成多个间隔排布的沟槽;去除剩余的所述牺牲层;沉积隔离材料并平坦化,以在每一所述沟槽内形成一个浅沟槽隔离结构,多个所述浅沟槽隔离结构之间的台阶高度差均匀。上述技术方案,通过在第一刻蚀阻挡层及第二刻蚀阻挡层之间设置牺牲层,避免了所述第一刻蚀阻挡层在沟槽刻蚀的

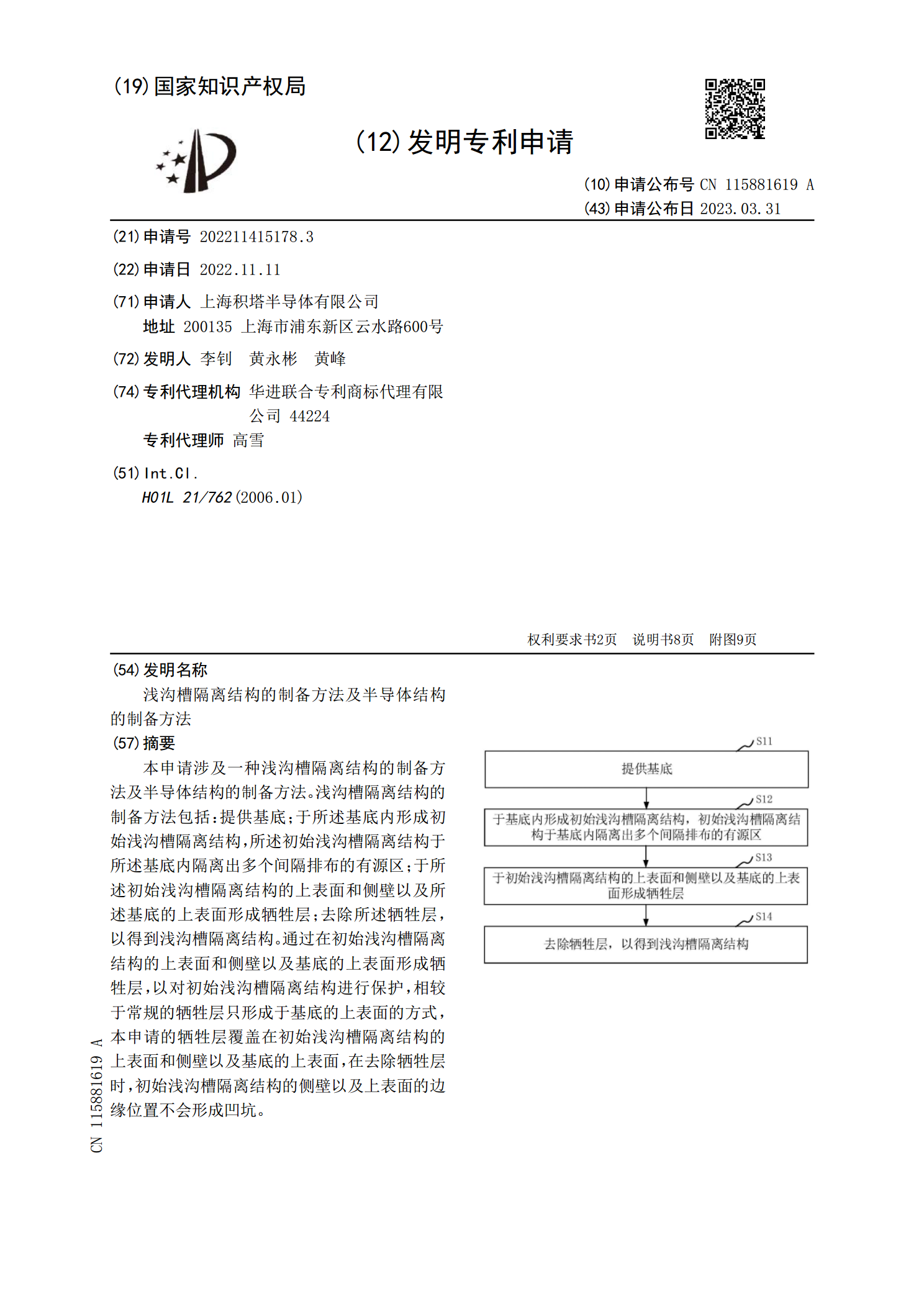

浅沟槽隔离结构的制备方法及半导体结构的制备方法.pdf

本申请涉及一种浅沟槽隔离结构的制备方法及半导体结构的制备方法。浅沟槽隔离结构的制备方法包括:提供基底;于所述基底内形成初始浅沟槽隔离结构,所述初始浅沟槽隔离结构于所述基底内隔离出多个间隔排布的有源区;于所述初始浅沟槽隔离结构的上表面和侧壁以及所述基底的上表面形成牺牲层;去除所述牺牲层,以得到浅沟槽隔离结构。通过在初始浅沟槽隔离结构的上表面和侧壁以及基底的上表面形成牺牲层,以对初始浅沟槽隔离结构进行保护,相较于常规的牺牲层只形成于基底的上表面的方式,本申请的牺牲层覆盖在初始浅沟槽隔离结构的上表面和侧壁以及基