芯片功耗调整、神经网络训练方法、装置以及芯片系统.pdf

是飞****文章

亲,该文档总共23页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

芯片功耗调整、神经网络训练方法、装置以及芯片系统.pdf

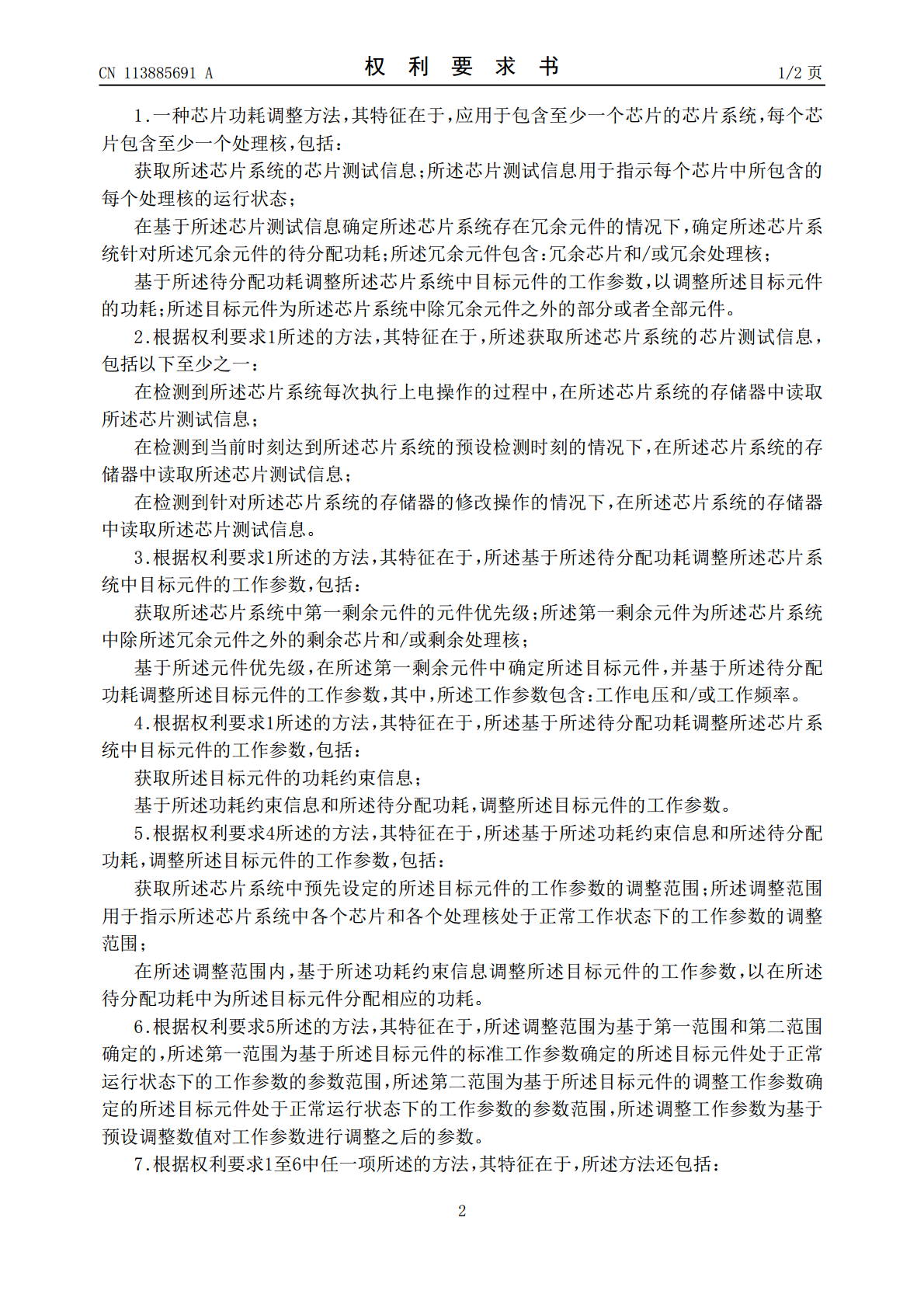

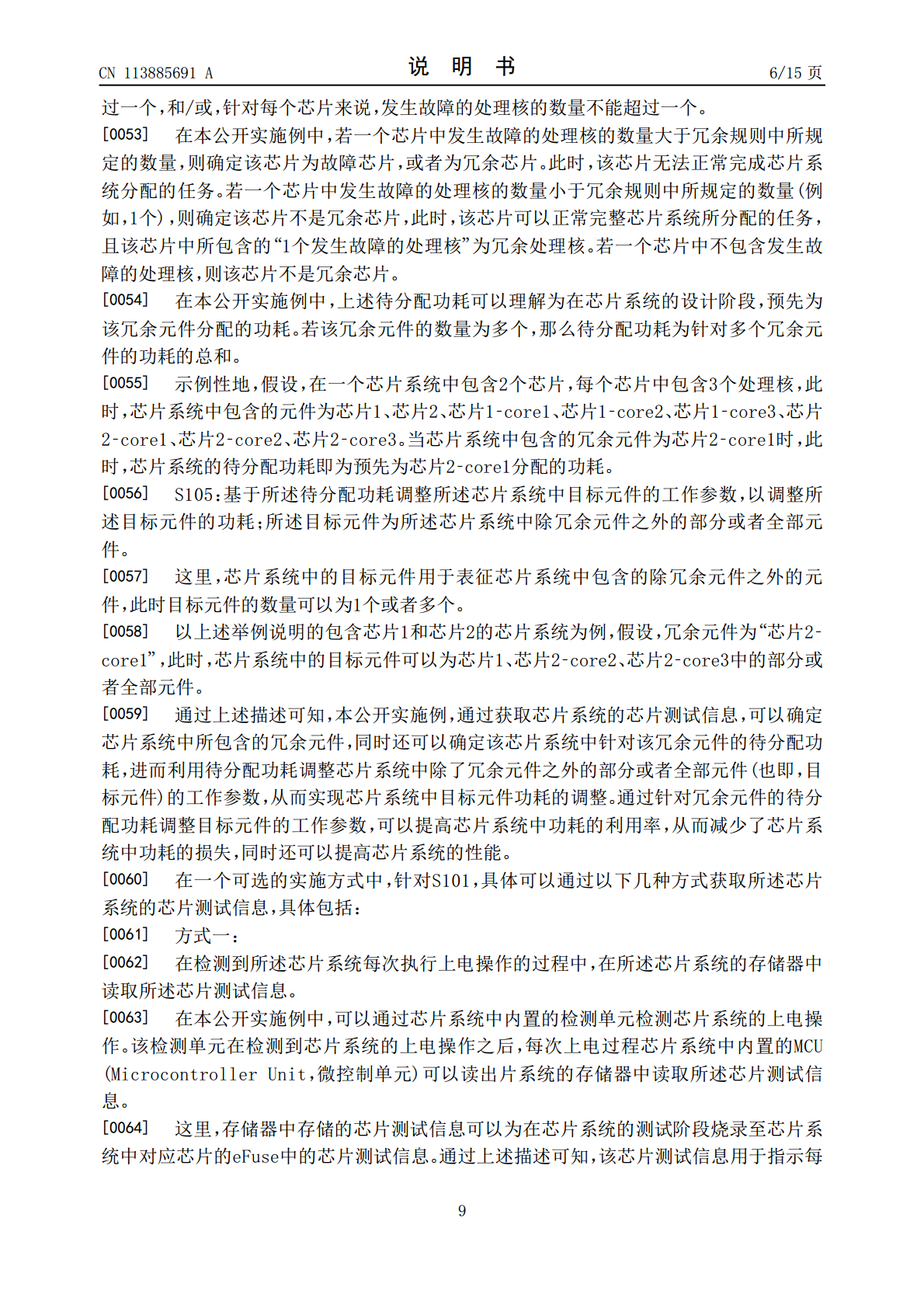

本公开提供了一种芯片功耗调整、神经网络训练方法、装置以及芯片系统,其中,该方法包括:获取所述芯片系统的芯片测试信息;所述芯片测试信息用于指示每个芯片中所包含的每个处理核的运行状态;在基于所述芯片测试信息确定所述芯片系统存在冗余元件的情况下,确定所述芯片系统针对所述冗余元件的待分配功耗;所述冗余元件包含:冗余芯片和/或冗余处理核;基于所述待分配功耗调整所述芯片系统中目标元件的工作参数,以调整所述目标元件的功耗;所述目标元件为所述芯片系统中除冗余元件之外的部分或者全部元件。

CPU功耗测试设备、方法、系统、控制芯片及测试芯片.pdf

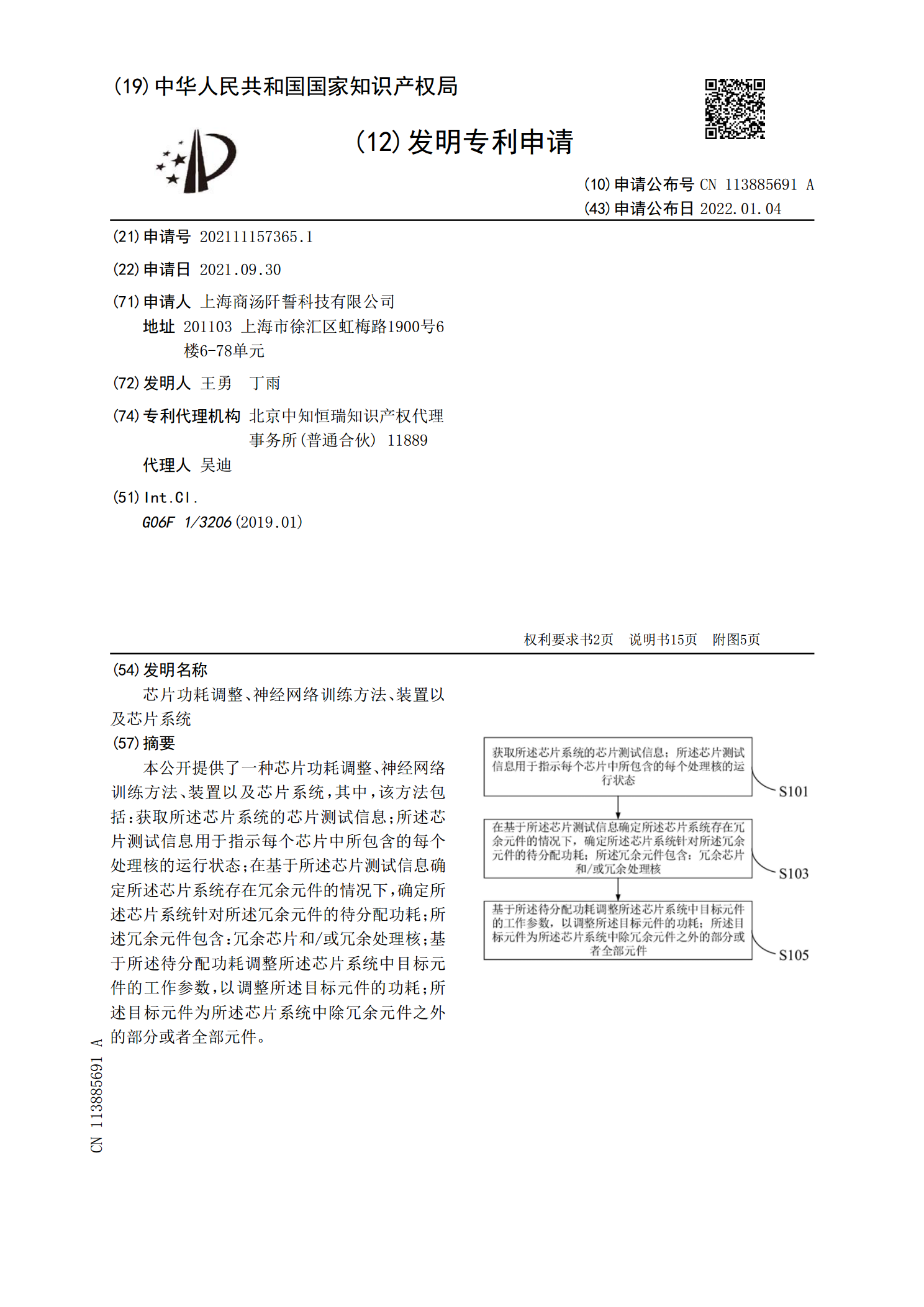

本说明书公开了一种CPU功耗测试设备、方法、系统、控制芯片及测试芯片。首先,通过利用控制芯片的第一片内总线、第一通用输入输出控制器、片间总线、测试芯片的第二片内总线建立控制用CPU和测试芯片的第二存储单元之间的连接,接着,利用控制用CPU从控制芯片的第一存储单元中读取测试程序,且控制用CPU可以通过第一通用输入输出控制器和所述片间总线将读取到的测试程序写入至测试芯片的第二存储单元,实现针对CPU的功耗测试所需的快速方便的测试平台的构建,提升了测试平台重复使用性和广泛适配性。

膜上芯片以及包括该膜上芯片的显示装置.pdf

公开了膜上芯片以及包括该膜上芯片的显示装置。该膜上芯片包括:第一基膜;第二基膜,所述第二基膜位于所述第一基膜上;膜焊盘部,所述膜焊盘部位于所述第二基膜的至少一侧并暴露于所述第一基膜的外侧;以及涂层,所述涂层位于所述第一基膜的一个表面上。

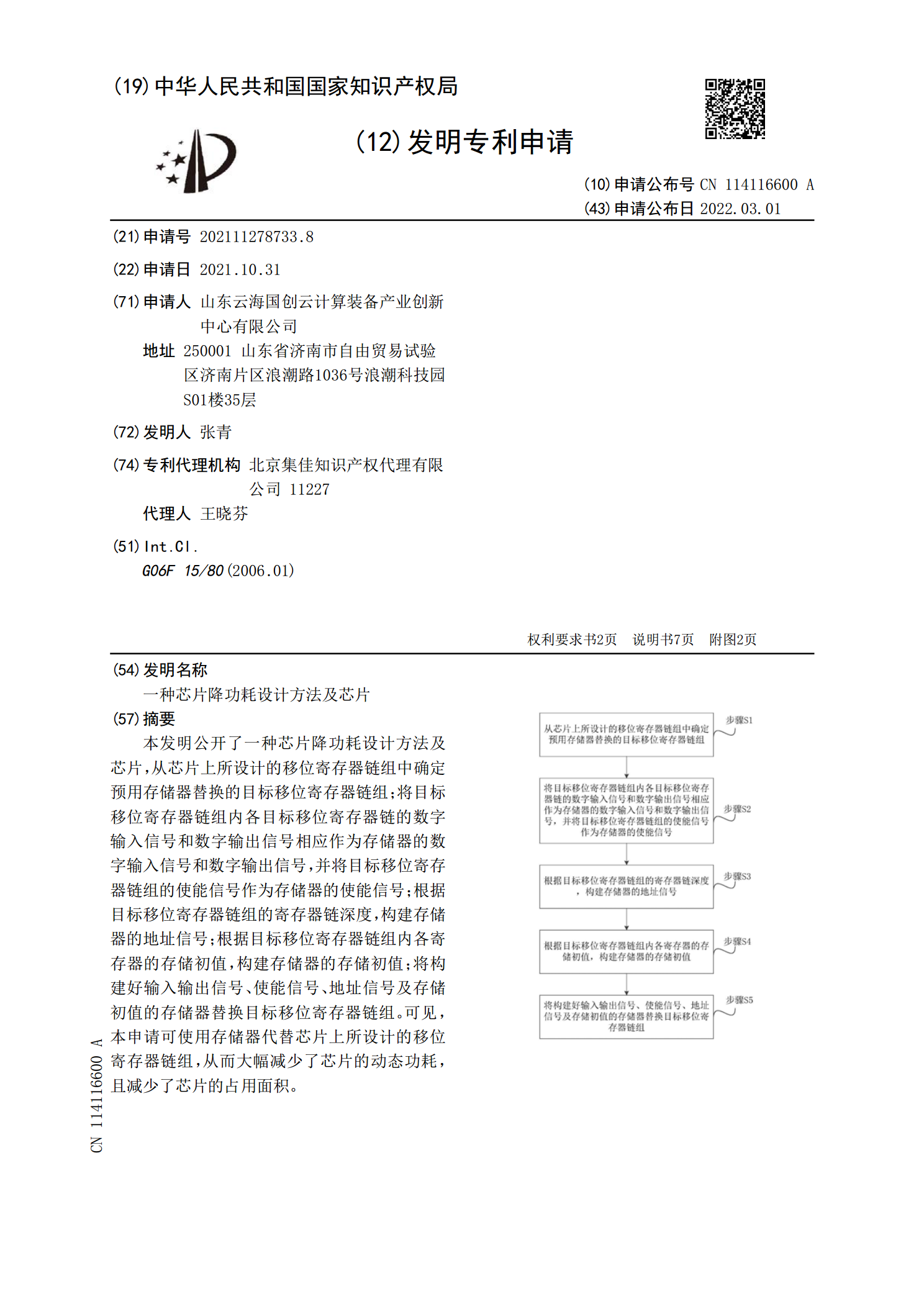

一种芯片降功耗设计方法及芯片.pdf

本发明公开了一种芯片降功耗设计方法及芯片,从芯片上所设计的移位寄存器链组中确定预用存储器替换的目标移位寄存器链组;将目标移位寄存器链组内各目标移位寄存器链的数字输入信号和数字输出信号相应作为存储器的数字输入信号和数字输出信号,并将目标移位寄存器链组的使能信号作为存储器的使能信号;根据目标移位寄存器链组的寄存器链深度,构建存储器的地址信号;根据目标移位寄存器链组内各寄存器的存储初值,构建存储器的存储初值;将构建好输入输出信号、使能信号、地址信号及存储初值的存储器替换目标移位寄存器链组。可见,本申请可使用存储

芯片的封装方法以及芯片封装体.pdf

本发明公开了一种芯片的封装方法以及芯片封装体。芯片的封装方法包括:获取到陶瓷基板,陶瓷基板的一表面形成有多个焊盘;将至少一个芯片的各引脚与对应的焊盘进行焊接;在陶瓷基板的一侧面固定且贴合设置导流件,导流件的一表面与陶瓷基板靠近芯片的一表面平齐;利用导流件将粘合剂导流至各芯片与陶瓷基板之间,以完成芯片的封装。上述方案,能够减少空洞以及填充不完全的现象发生,从而提高各芯片与陶瓷基板之间的结合力,提高各芯片与陶瓷基板之间的结构稳定性与可靠性。