一种芯片降功耗设计方法及芯片.pdf

Ch****49

亲,该文档总共12页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种芯片降功耗设计方法及芯片.pdf

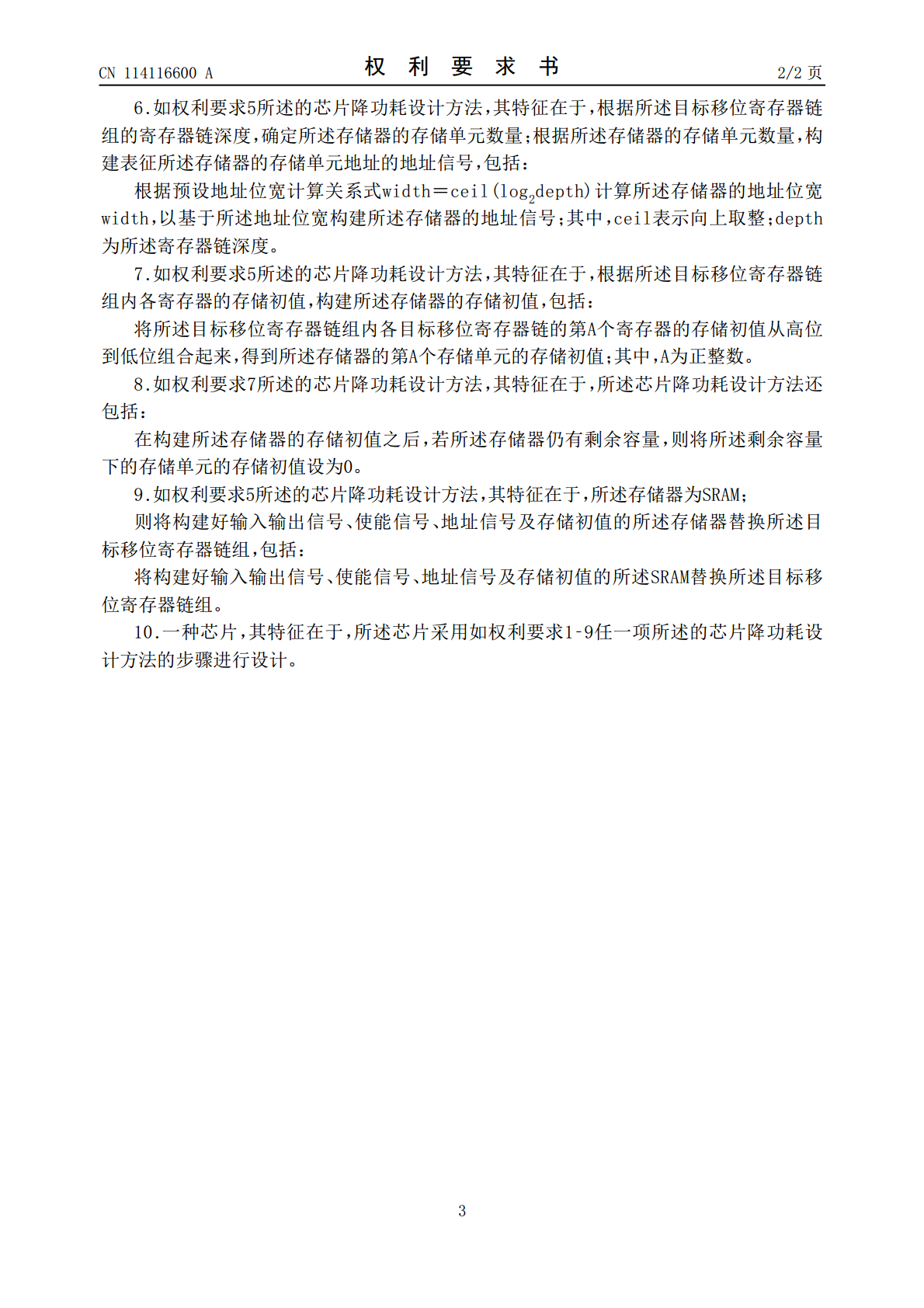

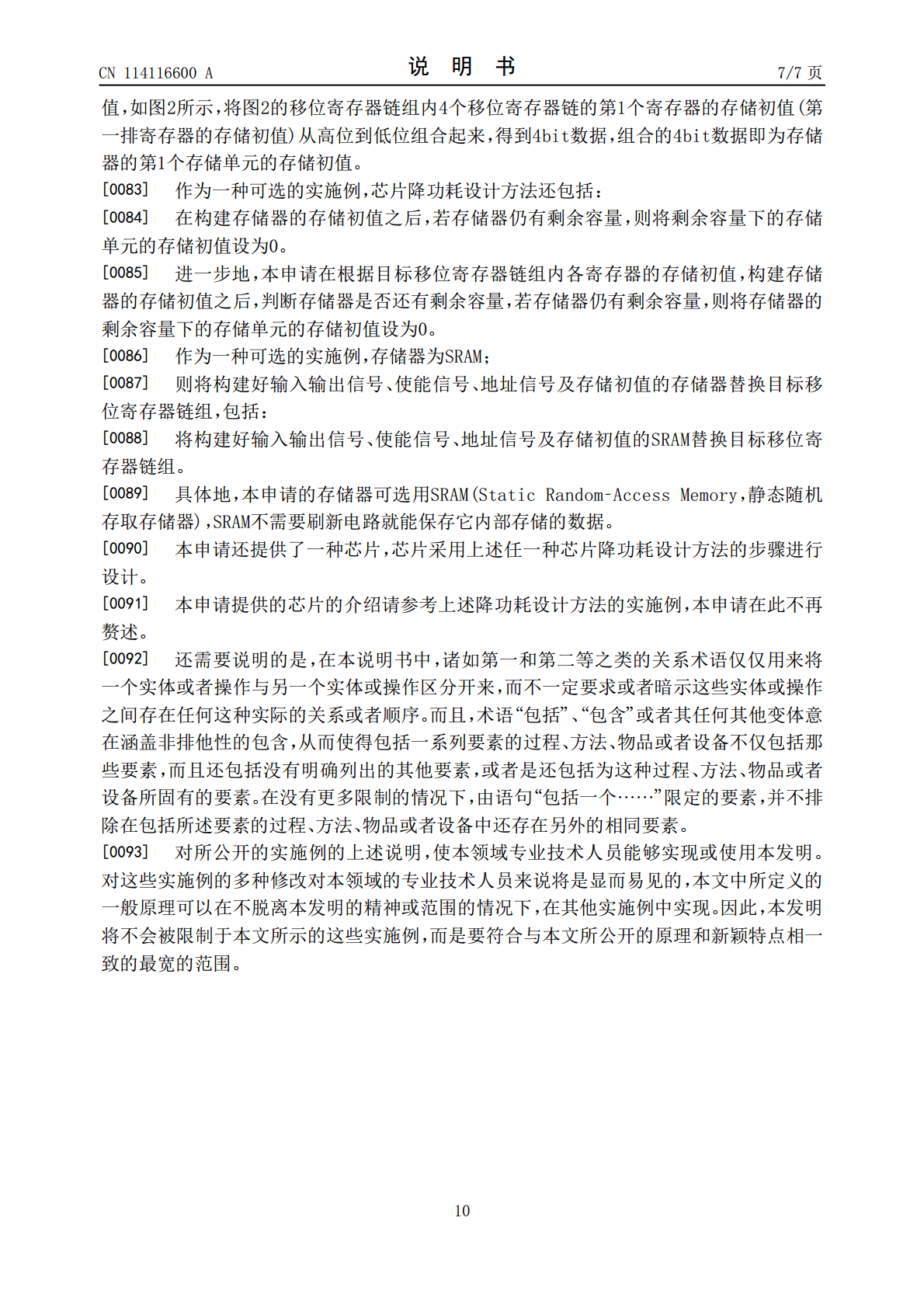

本发明公开了一种芯片降功耗设计方法及芯片,从芯片上所设计的移位寄存器链组中确定预用存储器替换的目标移位寄存器链组;将目标移位寄存器链组内各目标移位寄存器链的数字输入信号和数字输出信号相应作为存储器的数字输入信号和数字输出信号,并将目标移位寄存器链组的使能信号作为存储器的使能信号;根据目标移位寄存器链组的寄存器链深度,构建存储器的地址信号;根据目标移位寄存器链组内各寄存器的存储初值,构建存储器的存储初值;将构建好输入输出信号、使能信号、地址信号及存储初值的存储器替换目标移位寄存器链组。可见,本申请可使用存储

CPU功耗测试设备、方法、系统、控制芯片及测试芯片.pdf

本说明书公开了一种CPU功耗测试设备、方法、系统、控制芯片及测试芯片。首先,通过利用控制芯片的第一片内总线、第一通用输入输出控制器、片间总线、测试芯片的第二片内总线建立控制用CPU和测试芯片的第二存储单元之间的连接,接着,利用控制用CPU从控制芯片的第一存储单元中读取测试程序,且控制用CPU可以通过第一通用输入输出控制器和所述片间总线将读取到的测试程序写入至测试芯片的第二存储单元,实现针对CPU的功耗测试所需的快速方便的测试平台的构建,提升了测试平台重复使用性和广泛适配性。

MCU芯片的低功耗设计方法与实现的开题报告.docx

MCU芯片的低功耗设计方法与实现的开题报告摘要:随着物联网和移动应用的快速发展,对于能够提供低功耗的产品的需求越来越高。MCU芯片,作为其中颇具代表性的一个电子元器件,其功耗设计显得格外重要。本文主要探讨了MCU芯片的低功耗设计方法与实现,包括功耗管理单元(PMU)、特殊的时钟控制技术、GPIO外设控制等方面。关键词:MCU芯片,低功耗设计,功耗管理单元,时钟控制技术,GPIO外设控制。一、绪论随着信息技术的发展,人们对于电子产品的要求也相应地提升了。其中,能够以更低的功耗提供更好的体验的产品成为市场的热

一种低功耗隔离电路及其方法、芯片.pdf

本发明涉及芯片技术领域,特别是涉及一种低功耗隔离电路及其方法、芯片。其中,该低功耗隔离电路应用于芯片,芯片包括电源门控模块与下级逻辑模块,低功耗隔离电路包括:功耗管理单元;锁存单元,在电源门控模块处于待机模式时,功耗管理单元将锁存单元切换至锁存状态,使得锁存单元锁存下级逻辑模块进入待机模式之前的数据状态;隔离单元,在锁存单元锁存下级逻辑模块进入待机模式之前的数据状态后,功耗管理单元复位隔离单元,使得隔离单元向锁存单元输出逻辑值,逻辑值未改变锁存单元的锁存状态。因此,其能够在给下级逻辑模块输出确定状态后,还

一种面向多核DSP芯片的低功耗验证方法.docx

一种面向多核DSP芯片的低功耗验证方法随着通信技术和数字信号处理技术的不断发展,多核DSP芯片在数字信号处理及通信领域中被广泛应用。针对多核DSP芯片的特点,低功耗验证方法成为了一个重要的研究方向。本文将介绍一种面向多核DSP芯片的低功耗验证方法,该方法可以有效降低芯片功耗,提高芯片性能,为实际应用提供有力保障。一、多核DSP芯片的特点目前,市面上的多核DSP芯片大多都采用对称多处理器(SMP)架构,这种架构的优点是可以平衡不同处理器之间的负载,在处理具有大量并行性的任务时具有较高的效率。然而,SMP架构