一种应用于IO接收器的接收电路、IO接收器和芯片.pdf

和裕****az

亲,该文档总共20页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种应用于IO接收器的接收电路、IO接收器和芯片.pdf

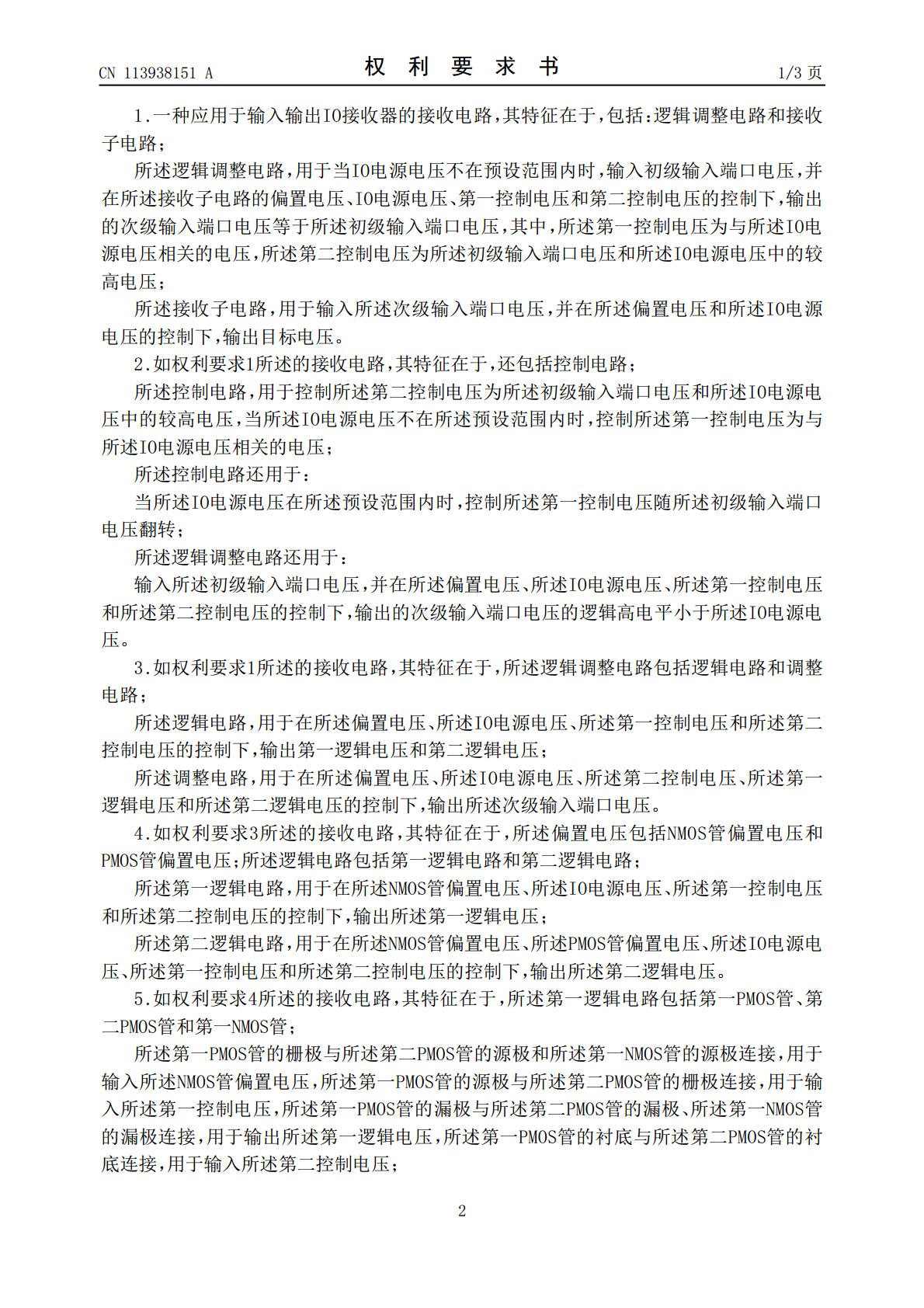

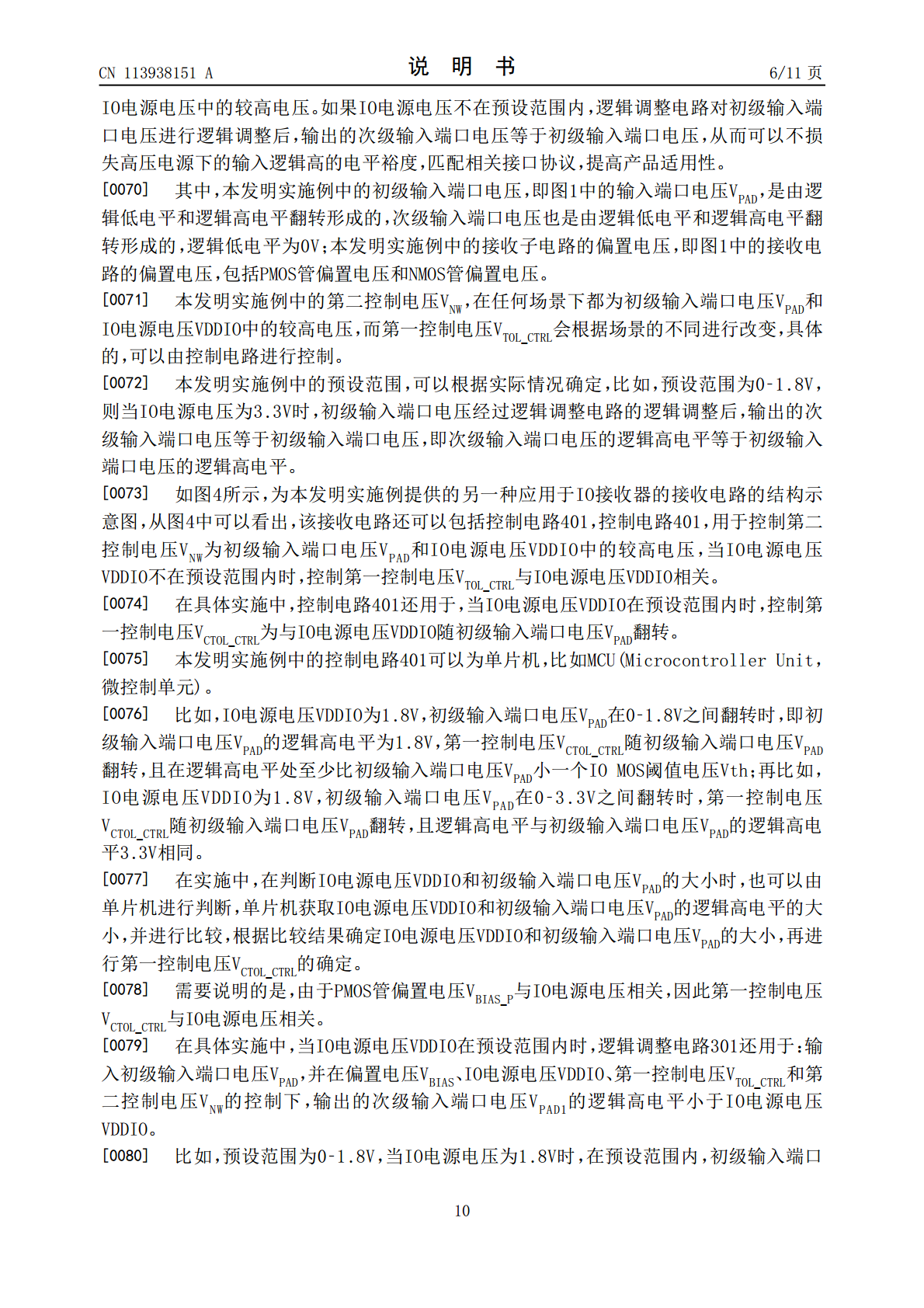

本发明公开了一种应用于IO接收器的接收电路、IO接收器和芯片,用以解决IO接收器对输入电压进行限高处理时,会造成相关接口协议不匹配,产品适用性差的问题。本发明当IO电源电压不在预设范围内时,逻辑调整电路在偏置电压、IO电源电压、第一控制电压和第二控制电压的控制下,输出等于初级输入端口电压的次级输入端口电压,接收子电路输入次级输入端口电压,并在偏置电压和IO电源电压的控制下,输出目标电压。由于IO电源电压不在预设范围内,逻辑调整电路对初级输入端口电压进行逻辑调整后,输出的次级输入端口电压等于初级输入端口电压

IO驱动电路及芯片.pdf

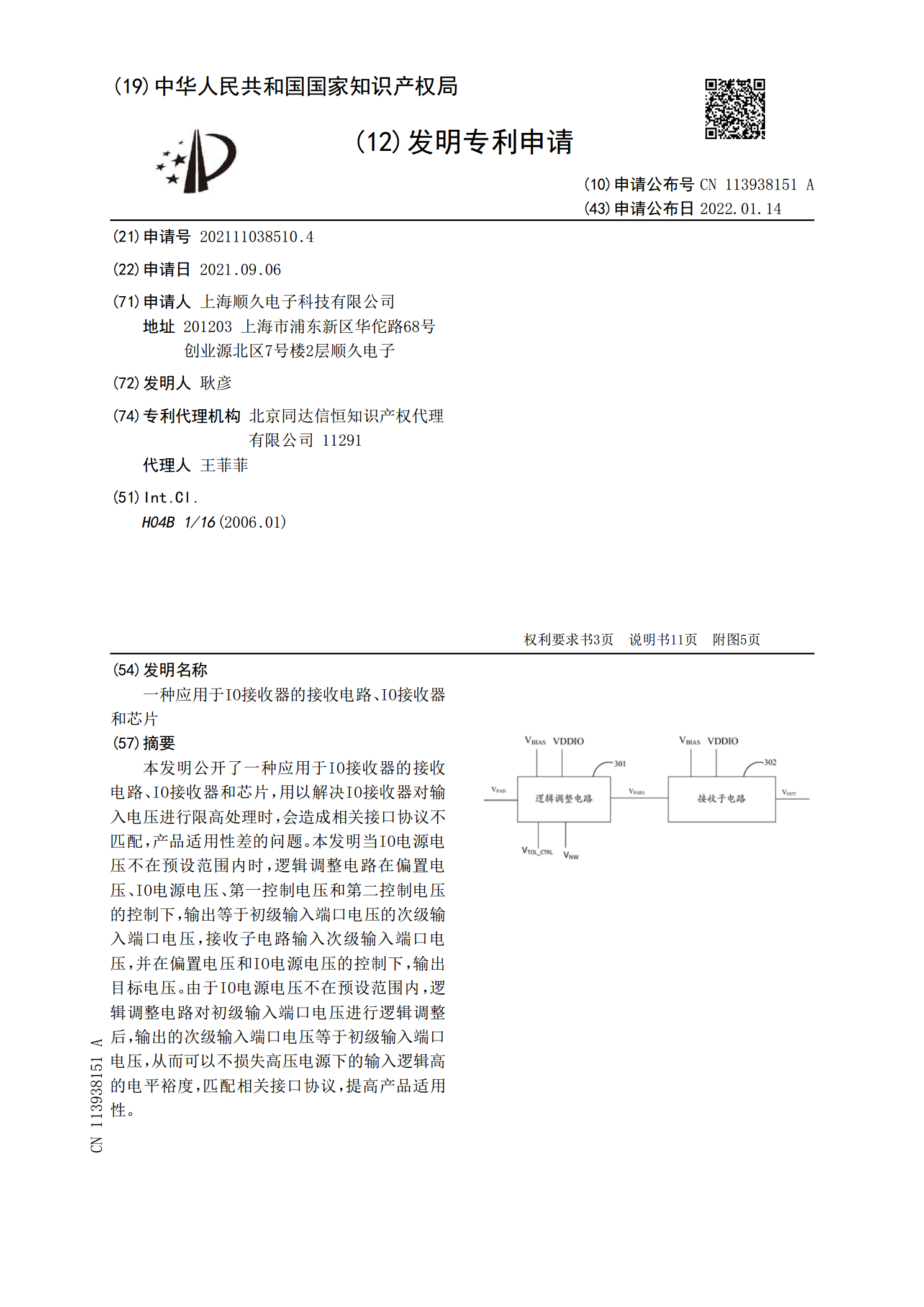

本发明提供了一种IO驱动电路及芯片,通过在第一驱动模块中增加第一至第二选择开关,控制输入输出单元的四个输入端的输入数据的来源,并通过在第一驱动模块中增加第三至第四选择开关,控制输入输出单元形成单端输出推挽结构或差分输出结构,进而达到单端输出和差分输出共用同一个输入输出单元的目的,节省了面积。进一步设置第二驱动模块,以实现单端模式和片内端接电阻模式的复用,进而可以将单端驱动电路、差分驱动电路及片内终端电阻三种电路进行合并,以进一步有效的节省芯片面积,降低芯片成本。

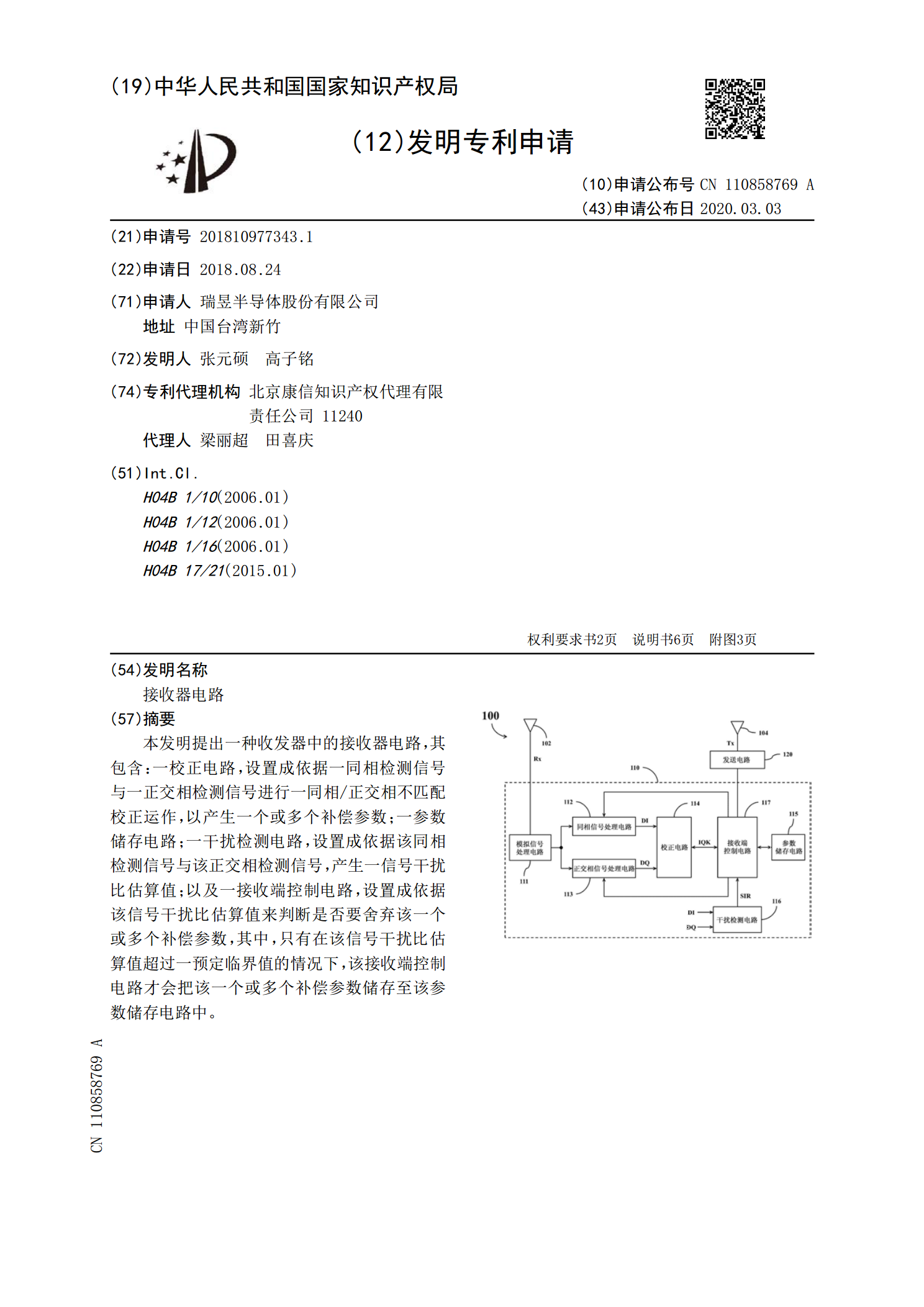

接收器电路.pdf

本发明提出一种收发器中的接收器电路,其包含:一校正电路,设置成依据一同相检测信号与一正交相检测信号进行一同相/正交相不匹配校正运作,以产生一个或多个补偿参数;一参数储存电路;一干扰检测电路,设置成依据该同相检测信号与该正交相检测信号,产生一信号干扰比估算值;以及一接收端控制电路,设置成依据该信号干扰比估算值来判断是否要舍弃该一个或多个补偿参数,其中,只有在该信号干扰比估算值超过一预定临界值的情况下,该接收端控制电路才会把该一个或多个补偿参数储存至该参数储存电路中。

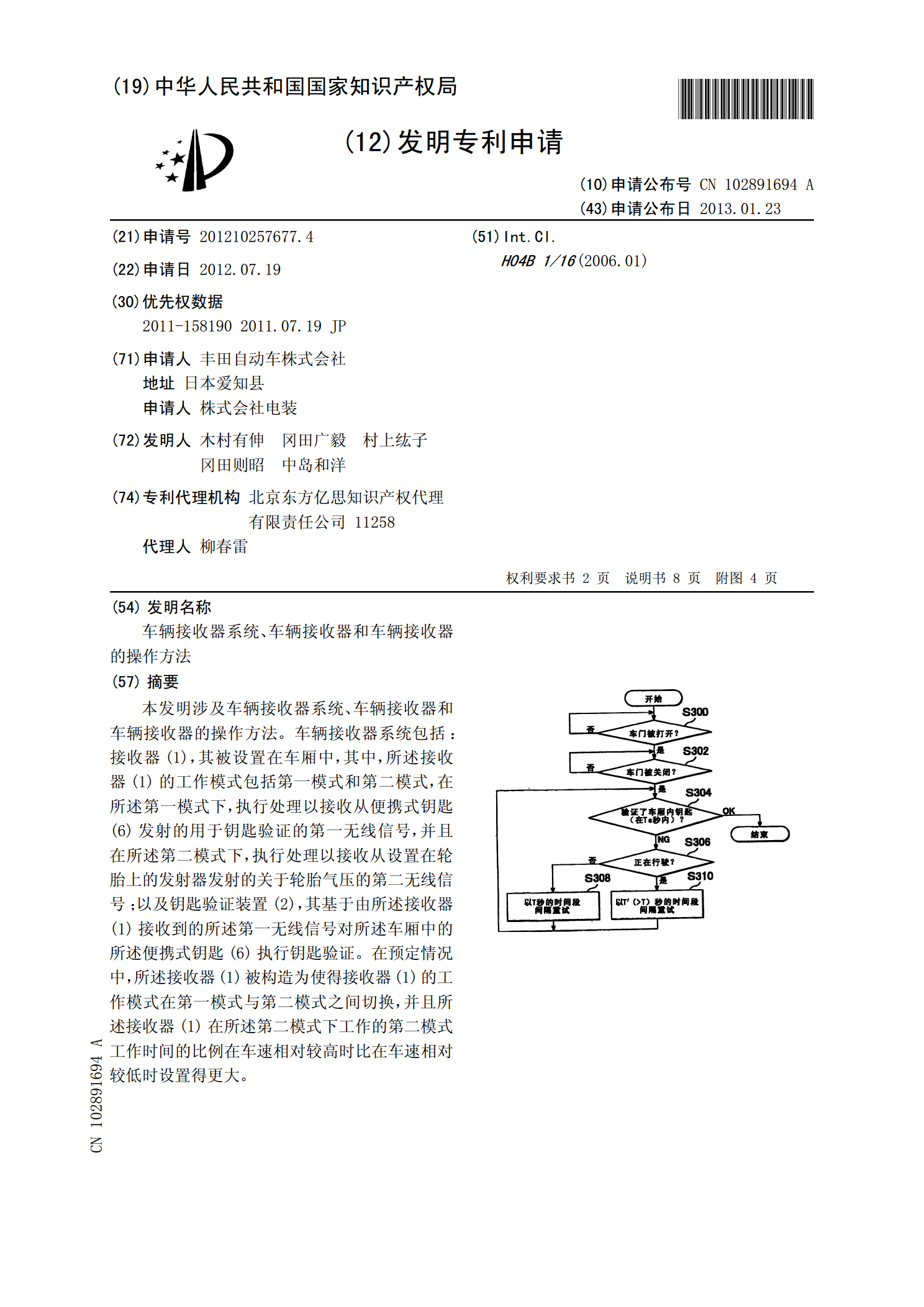

车辆接收器系统、车辆接收器和车辆接收器的操作方法.pdf

本发明涉及车辆接收器系统、车辆接收器和车辆接收器的操作方法。车辆接收器系统包括:接收器(1),其被设置在车厢中,其中,所述接收器(1)的工作模式包括第一模式和第二模式,在所述第一模式下,执行处理以接收从便携式钥匙(6)发射的用于钥匙验证的第一无线信号,并且在所述第二模式下,执行处理以接收从设置在轮胎上的发射器发射的关于轮胎气压的第二无线信号;以及钥匙验证装置(2),其基于由所述接收器(1)接收到的所述第一无线信号对所述车厢中的所述便携式钥匙(6)执行钥匙验证。在预定情况中,所述接收器(1)被构造为使得接收

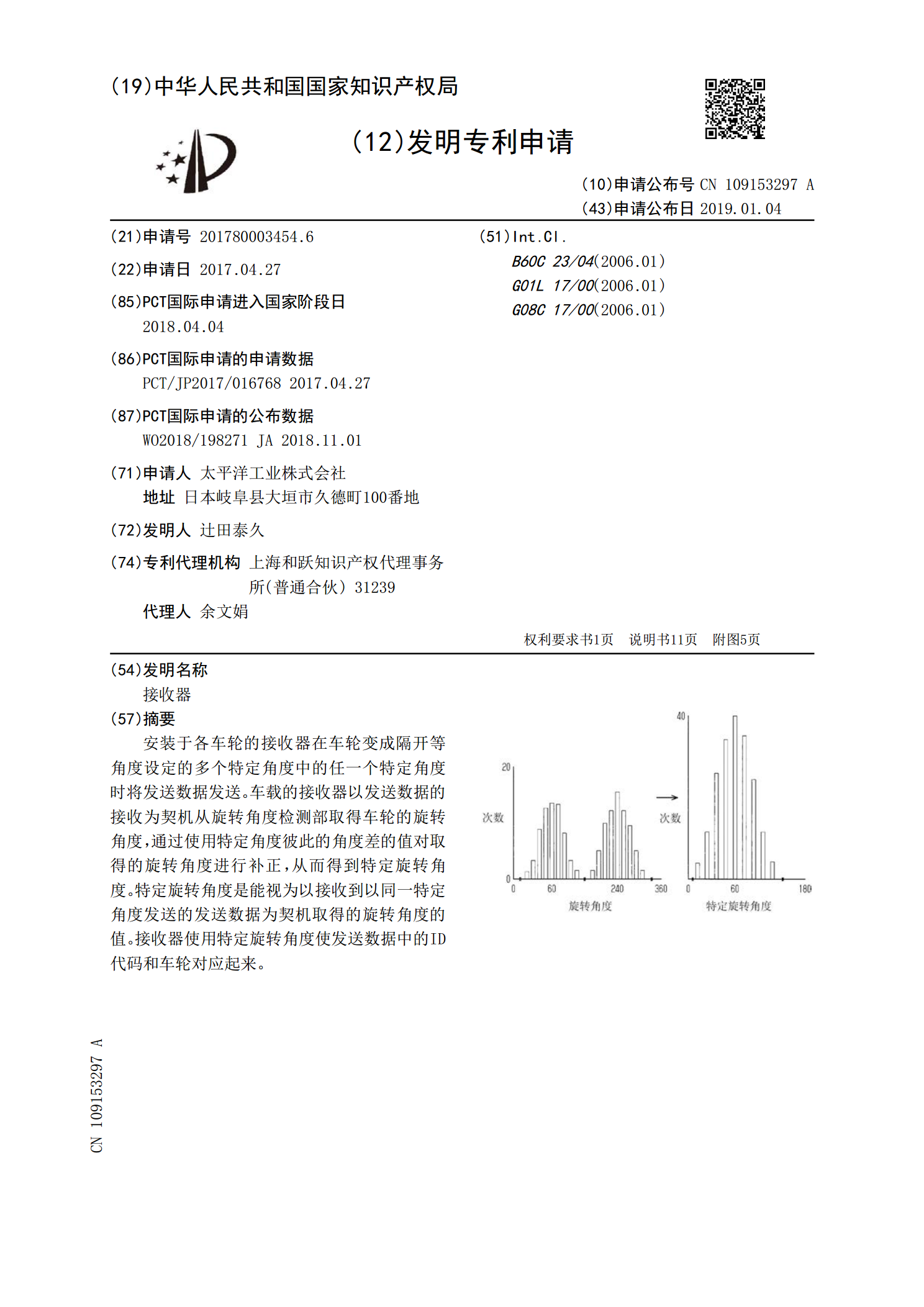

接收器.pdf

安装于各车轮的接收器在车轮变成隔开等角度设定的多个特定角度中的任一个特定角度时将发送数据发送。车载的接收器以发送数据的接收为契机从旋转角度检测部取得车轮的旋转角度,通过使用特定角度彼此的角度差的值对取得的旋转角度进行补正,从而得到特定旋转角度。特定旋转角度是能视为以接收到以同一特定角度发送的发送数据为契机取得的旋转角度的值。接收器使用特定旋转角度使发送数据中的ID代码和车轮对应起来。