集成电路结构及其制造方法.pdf

丹烟****魔王

亲,该文档总共84页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

集成电路结构及其制造方法.pdf

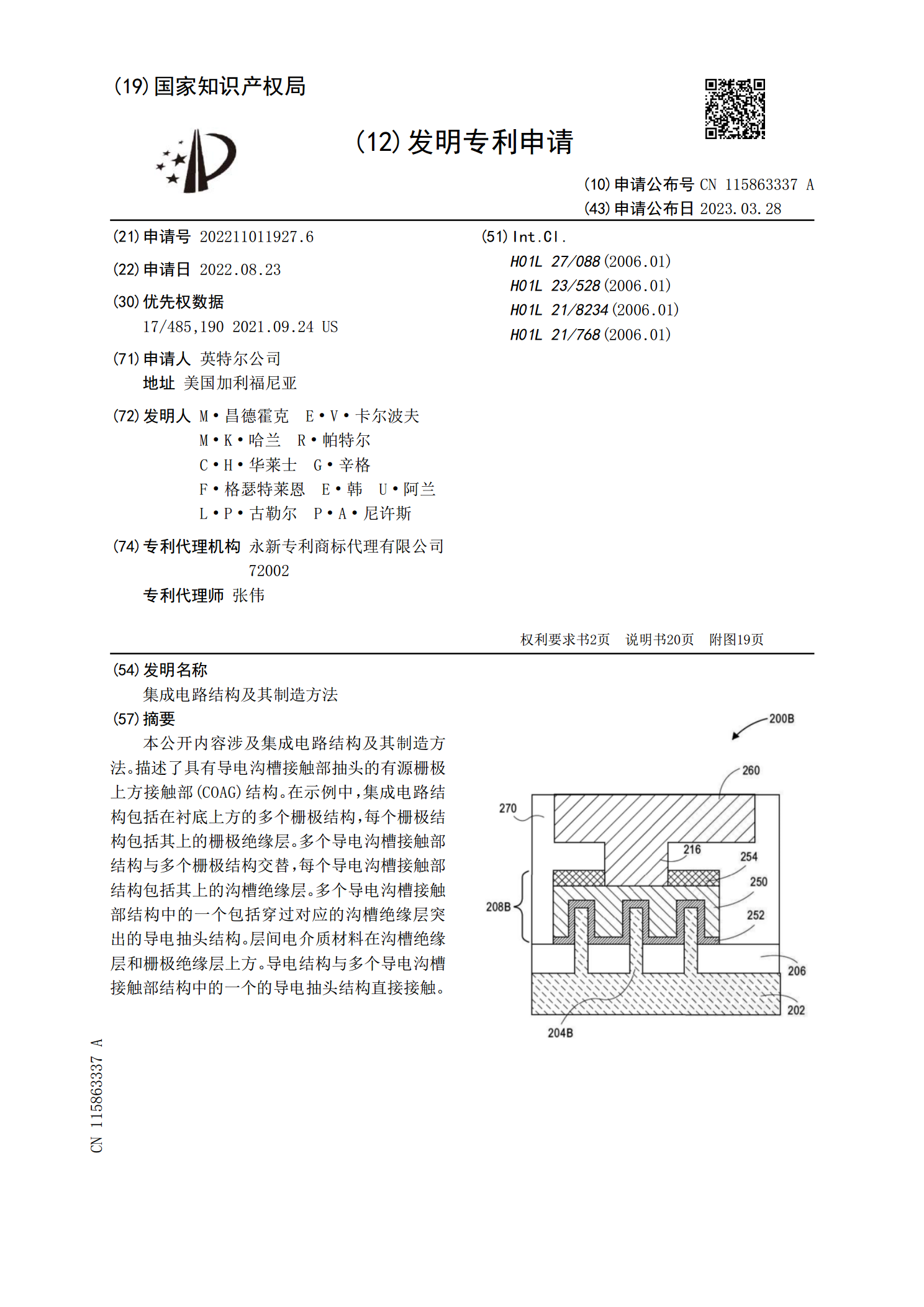

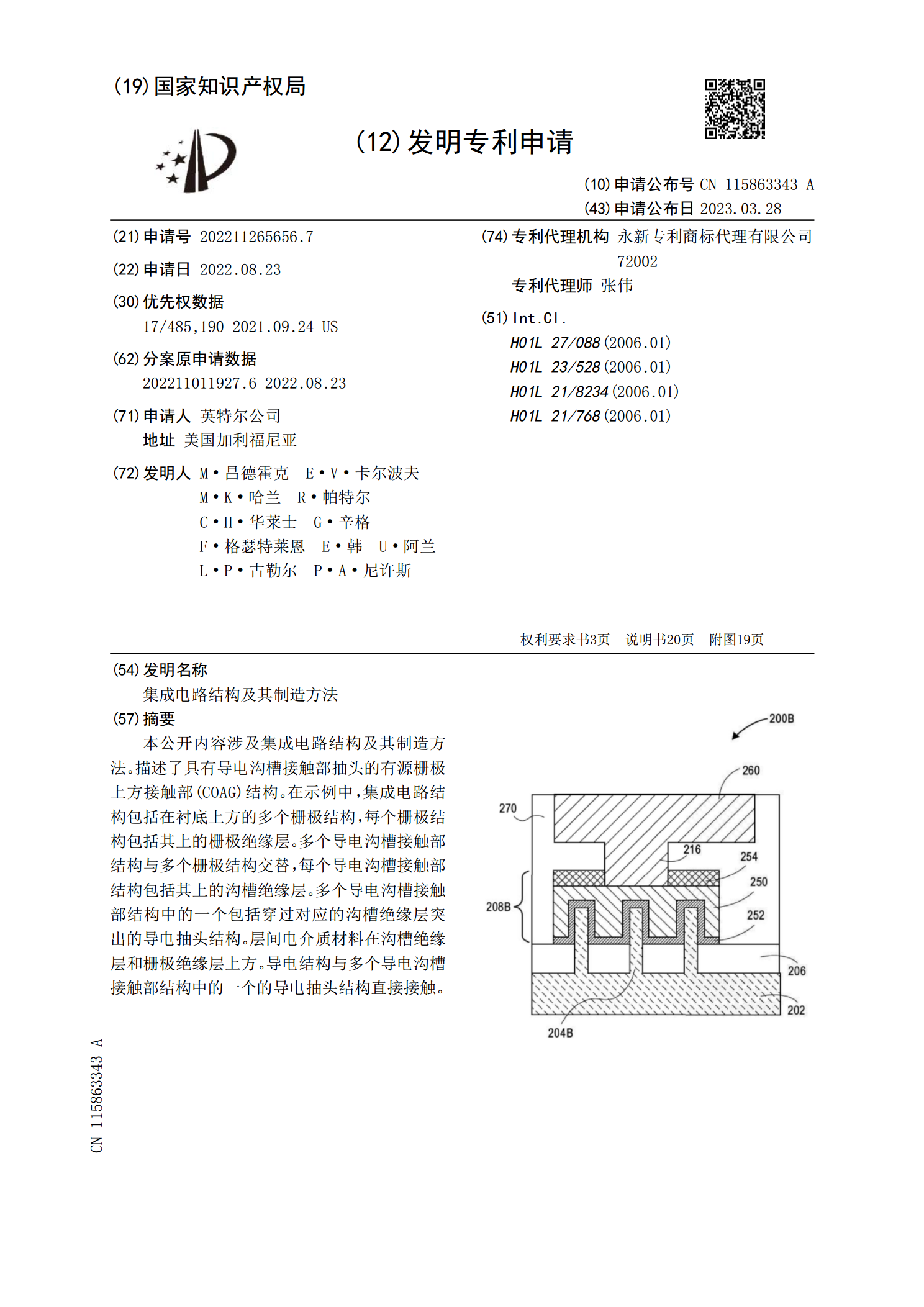

本公开内容涉及集成电路结构及其制造方法。描述了具有导电沟槽接触部抽头的有源栅极上方接触部(COAG)结构。在示例中,集成电路结构包括在衬底上方的多个栅极结构,每个栅极结构包括其上的栅极绝缘层。多个导电沟槽接触部结构与多个栅极结构交替,每个导电沟槽接触部结构包括其上的沟槽绝缘层。多个导电沟槽接触部结构中的一个包括穿过对应的沟槽绝缘层突出的导电抽头结构。层间电介质材料在沟槽绝缘层和栅极绝缘层上方。导电结构与多个导电沟槽接触部结构中的一个的导电抽头结构直接接触。

集成电路结构及其制造方法.pdf

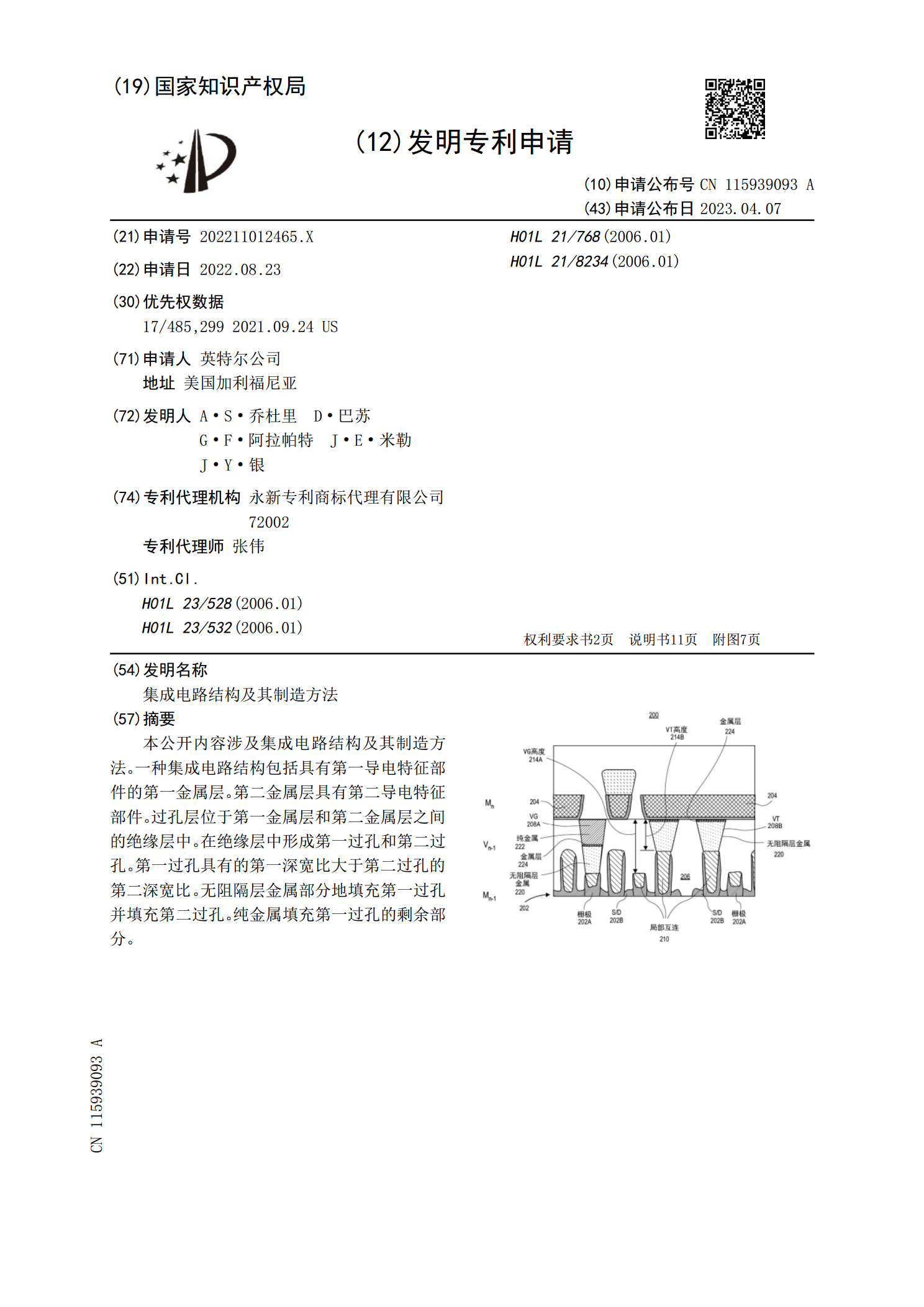

本公开内容涉及集成电路结构及其制造方法。一种集成电路结构包括具有第一导电特征部件的第一金属层。第二金属层具有第二导电特征部件。过孔层位于第一金属层和第二金属层之间的绝缘层中。在绝缘层中形成第一过孔和第二过孔。第一过孔具有的第一深宽比大于第二过孔的第二深宽比。无阻隔层金属部分地填充第一过孔并填充第二过孔。纯金属填充第一过孔的剩余部分。

集成电路结构及其制造方法.pdf

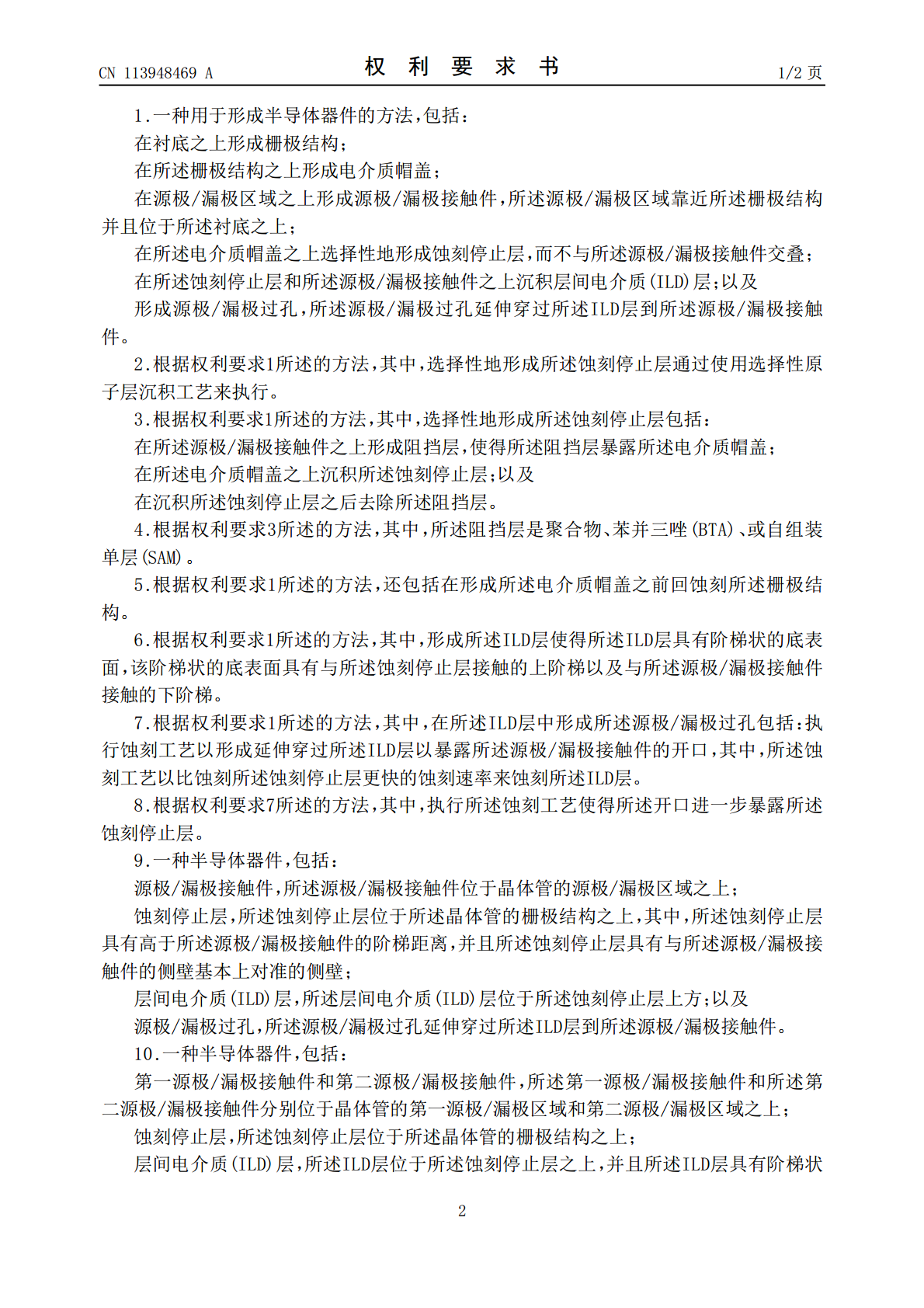

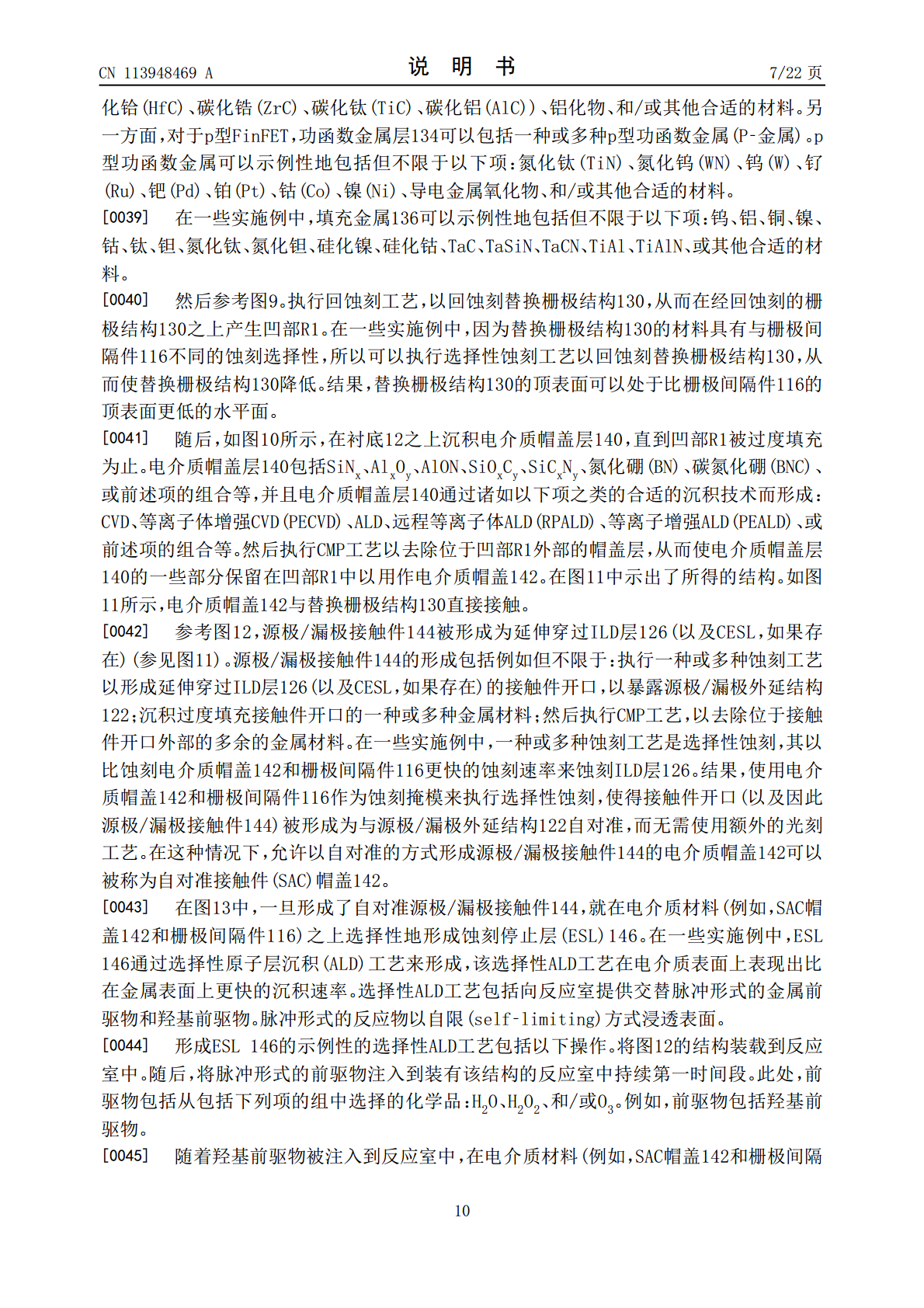

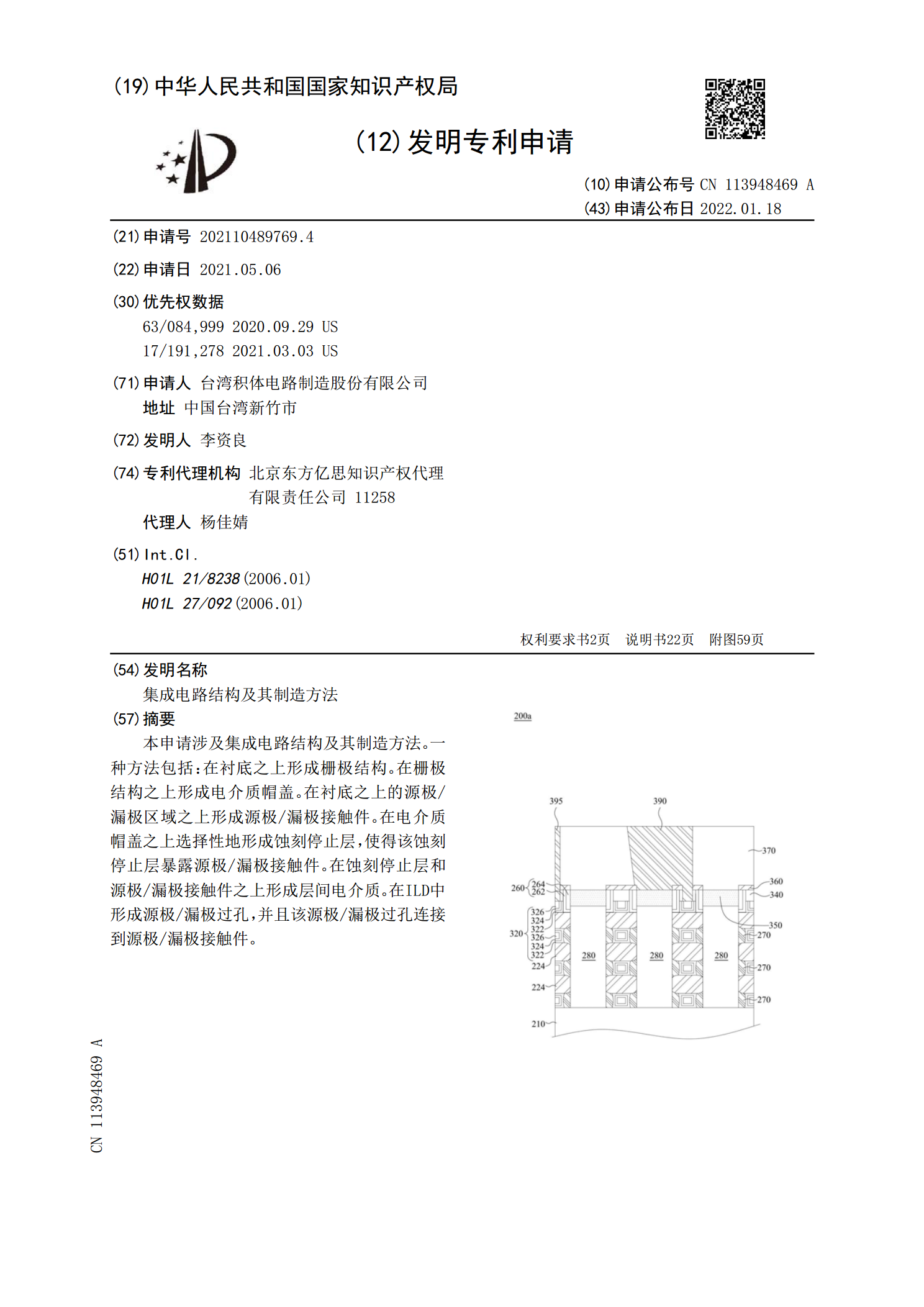

本申请涉及集成电路结构及其制造方法。一种方法包括:在衬底之上形成栅极结构。在栅极结构之上形成电介质帽盖。在衬底之上的源极/漏极区域之上形成源极/漏极接触件。在电介质帽盖之上选择性地形成蚀刻停止层,使得该蚀刻停止层暴露源极/漏极接触件。在蚀刻停止层和源极/漏极接触件之上形成层间电介质。在ILD中形成源极/漏极过孔,并且该源极/漏极过孔连接到源极/漏极接触件。

集成电路结构及其制造方法.pdf

本公开涉及集成电路结构及其制造方法。一种方法包括在栅极结构之上沉积电介质帽盖。在源极/漏极区域之上与栅极结构相邻地形成源极/漏极接触件。氧化电介质帽盖的顶部。在氧化电介质帽盖的顶部之后,在电介质帽盖之上沉积蚀刻停止层,并在蚀刻停止层之上沉积层间电介质(ILD)层。蚀刻ILD层和蚀刻停止层以形成过孔开口,该过孔开口延伸穿过ILD层和蚀刻停止层。在过孔开口中填充源极/漏极过孔。

集成电路结构及其制造方法.pdf

本公开内容涉及集成电路结构及其制造方法。描述了具有导电沟槽接触部抽头的有源栅极上方接触部(COAG)结构。在示例中,集成电路结构包括在衬底上方的多个栅极结构,每个栅极结构包括其上的栅极绝缘层。多个导电沟槽接触部结构与多个栅极结构交替,每个导电沟槽接触部结构包括其上的沟槽绝缘层。多个导电沟槽接触部结构中的一个包括穿过对应的沟槽绝缘层突出的导电抽头结构。层间电介质材料在沟槽绝缘层和栅极绝缘层上方。导电结构与多个导电沟槽接触部结构中的一个的导电抽头结构直接接触。