一种SPAD同轴型TO器件及其制作方法.pdf

萌运****魔王

亲,该文档总共14页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种SPAD同轴型TO器件及其制作方法.pdf

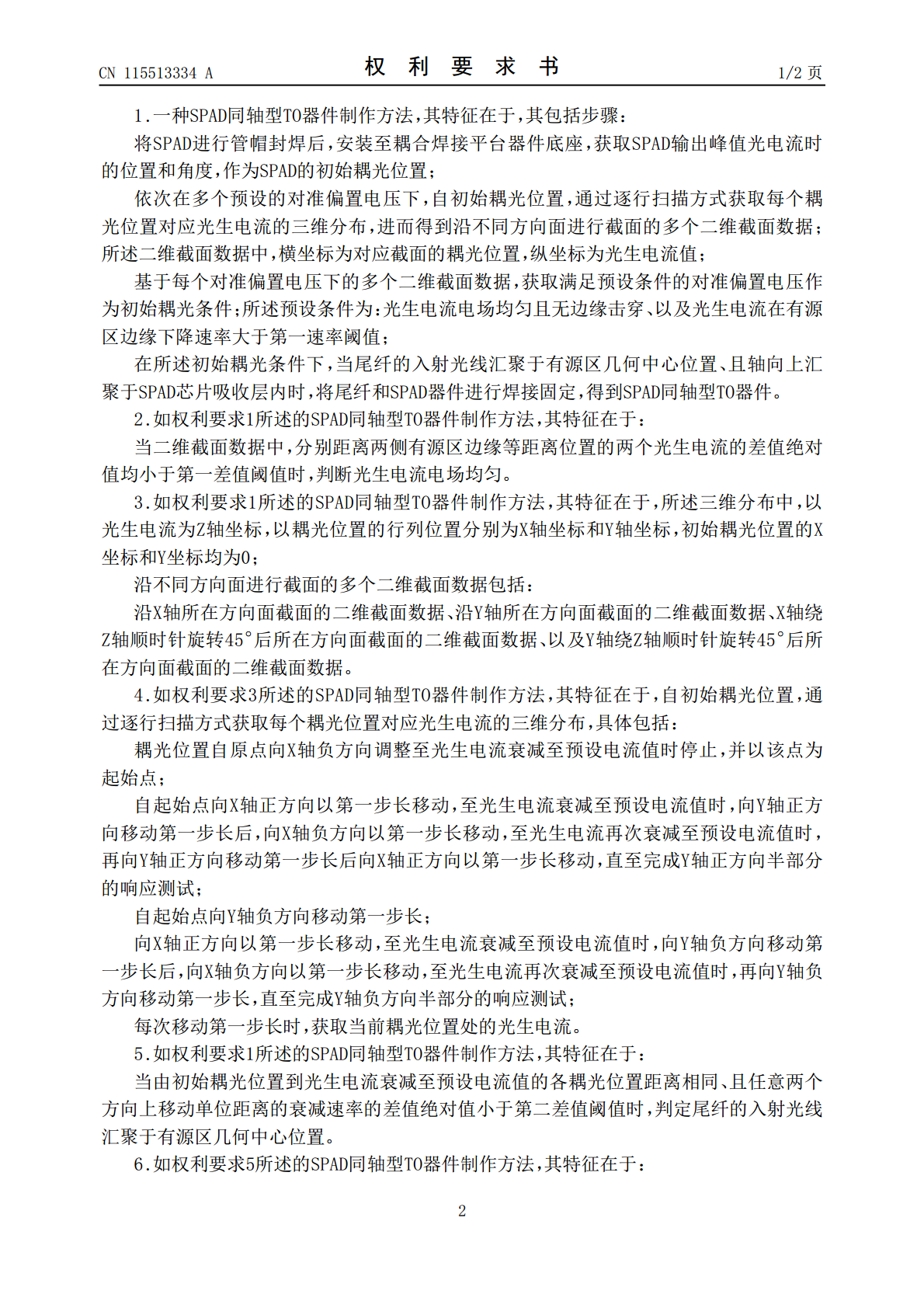

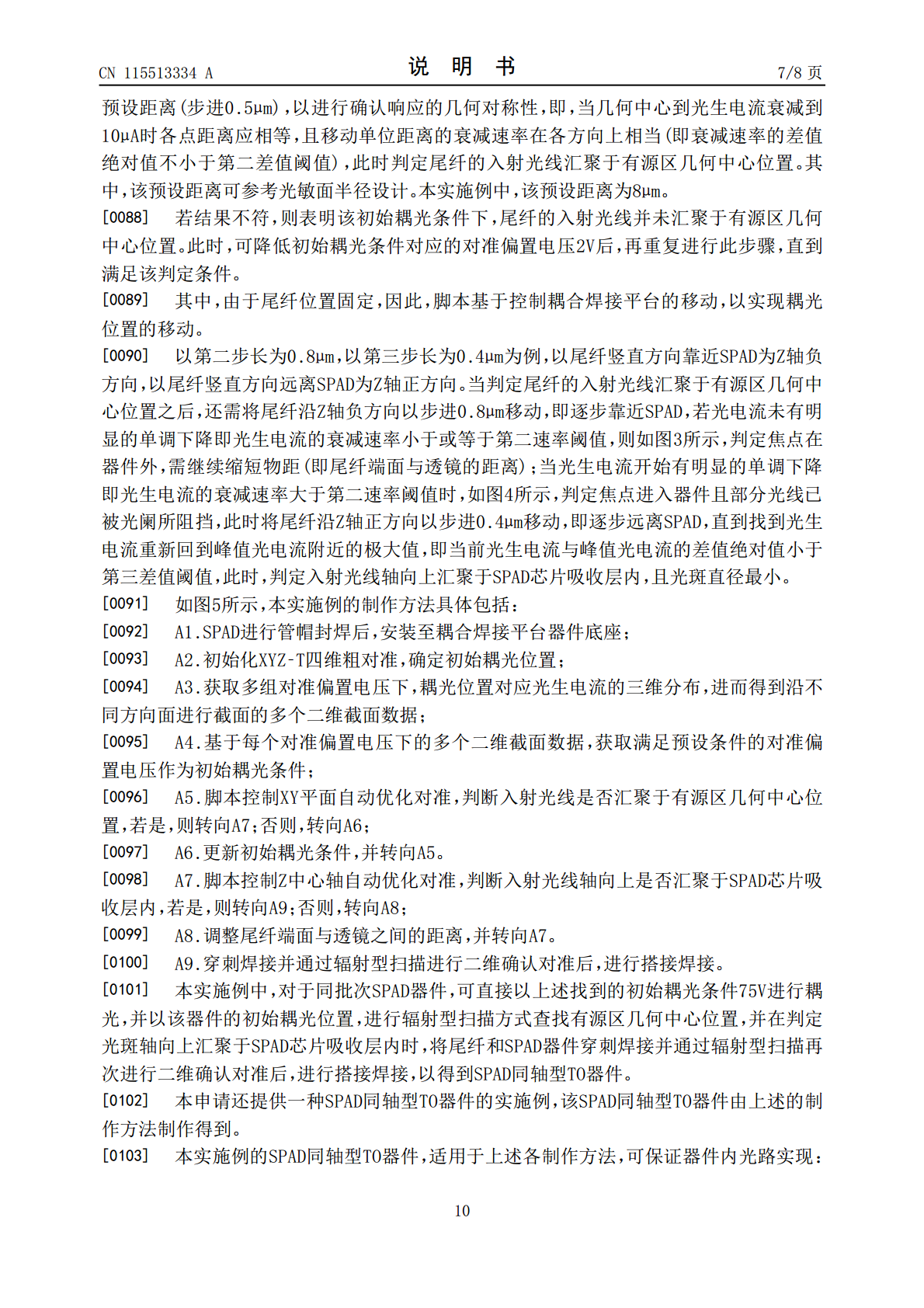

本申请公开了一种SPAD同轴型TO器件及其制作方法,涉及同轴型光电器件技术领域,该制作方法包括:将SPAD进行管帽封焊后,安装至耦合焊接平台器件底座,获取SPAD的初始耦光位置;依次在多个预设的对准偏置电压下,通过逐行扫描方式获取每个耦光位置对应光生电流的三维分布,进而得到多个二维截面数据;基于每个对准偏置电压下的多个二维截面数据,获取满足预设条件的对准偏置电压作为初始耦光条件;在初始耦光条件下,当尾纤的入射光线汇聚于有源区几何中心位置、且轴向上汇聚于SPAD芯片吸收层内时,将尾纤和SPAD器件进行焊接,

一种沟槽型功率器件结构及其制作方法.pdf

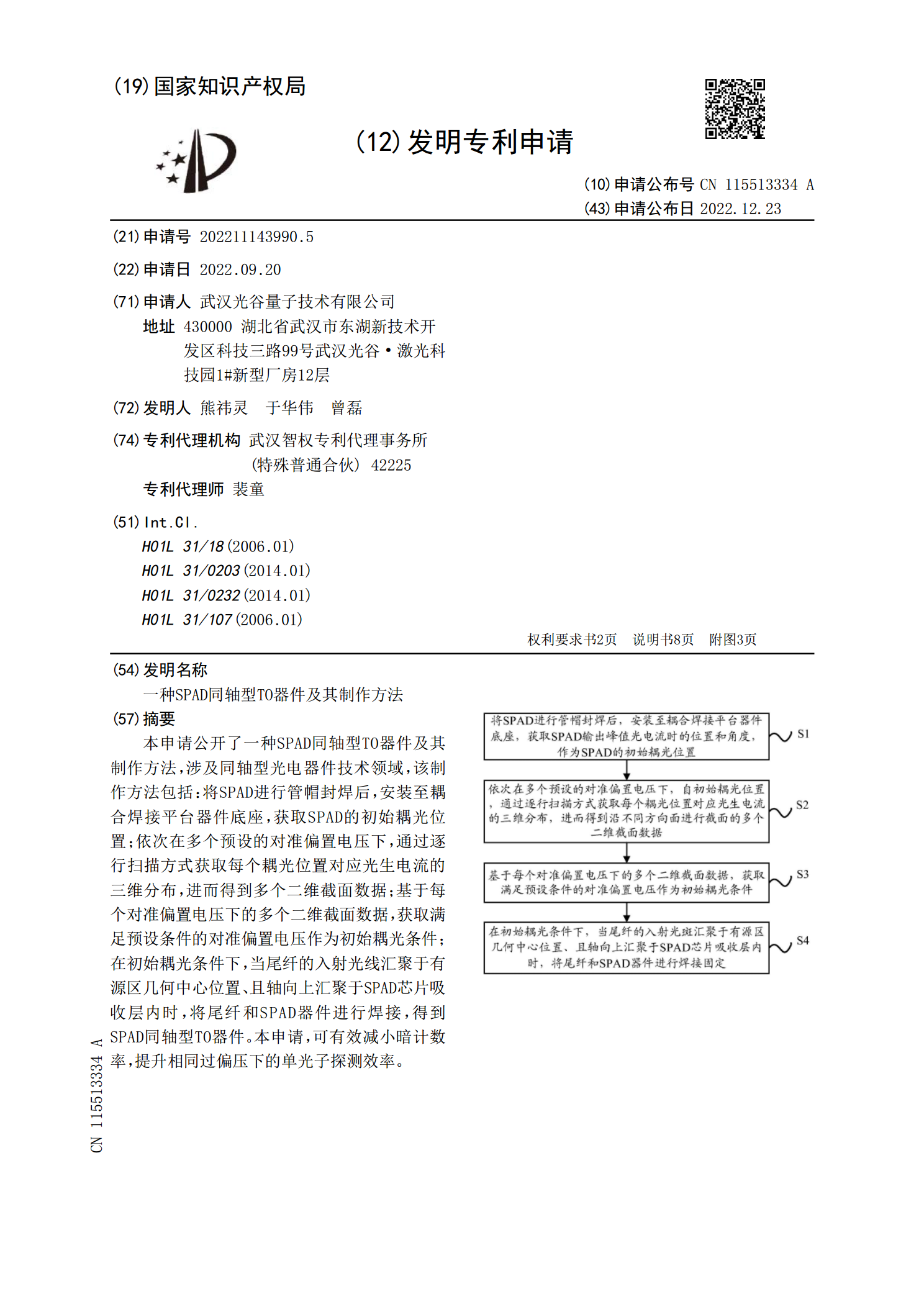

本发明公开了一种沟槽型功率器件结构及其制作方法,所述方法包括:提供半导体衬底;在半导体衬底上形成具有第一导电类型的外延层;在外延层中形成沟槽;对沟槽的底部执行第一离子注入,注入具有第二导电类型的离子,以在沟槽的底部下方的外延层中形成第二导电类型掺杂区;对沟槽的底部执行第二离子注入,注入具有第一导电类型的离子,以在沟槽的底部下方的外延层中形成第一导电类型掺杂区;其中,第二导电类型掺杂区的深度大于第一导电类型掺杂区的深度,第一导电类型掺杂区用于隔离第二导电类型掺杂区与沟槽。根据本发明提供的沟槽型功率器件结构及

一种沟槽型半超结功率器件及其制作方法.pdf

本发明公开了一种沟槽型半超结功率器件及其制作方法,其中制作方法包括:在衬底上形成双外延层,并进行刻蚀形成沟槽;在双外延层上方以及沟槽内形成P型硅;去除双外延层上方的全部P型硅以及沟槽内的部分P型硅;在双外延层以及沟槽内保留的P型硅上方形成氧化层,并在沟槽内填充多晶硅;去除双外延层上方的氧化层和多晶硅,对多晶硅进行N型离子注入,形成源区。采用双层外延片,一次沟槽刻蚀在沟槽下部形成P柱区域,利用氧化层作为隔离,在沟槽上部填充多晶硅形成沟道,工艺简单,降低了器件制造成本。双外延层以及保留的P型硅上方形成的氧化层

p型栅增强型HEMT器件及其制作方法.pdf

本发明公开了一种p型栅增强型HEMT器件及其制作方法。所述的制作方法包括制作异质结的步骤以及制作与异质结配合的栅极、源极、漏极的步骤;以及在异质结上形成第三半导体并对非栅下区域的第三半导体进行减薄处理,之后将非栅下区域内的第三半导体转化为第四半导体,并保留位于栅下区域的第三半导体,第四半导体为高阻半导体。本发明提供的制作方法不需要二次外延,也不需要对器件的栅下区域进行刻蚀,避免了因刻蚀工艺引入的均匀性、重复性和引入损伤问题,同时通过对器件栅下区域以外的有源区进行部分刻蚀,减少损伤。

一种CMOS器件及其制作方法.pdf

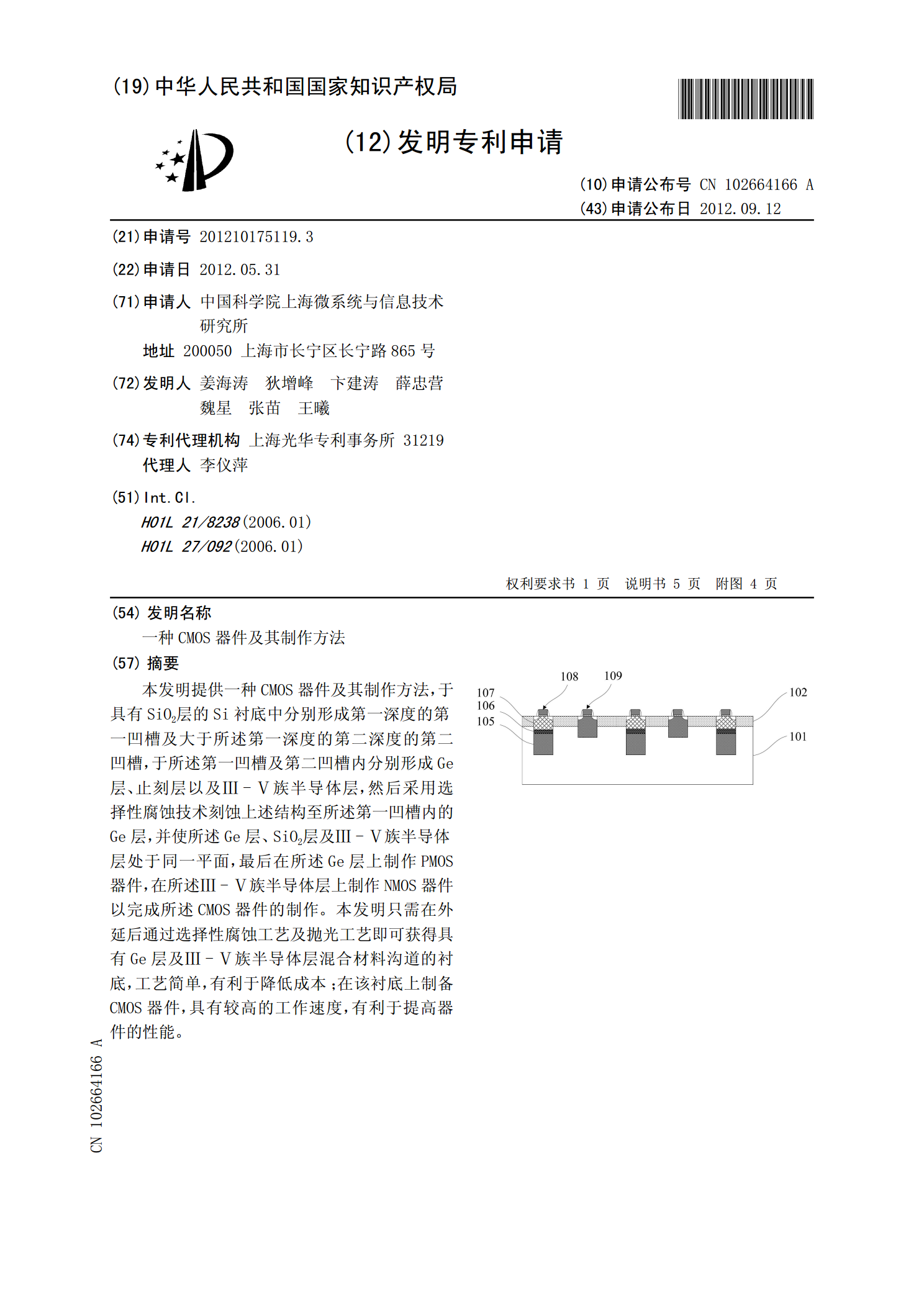

本发明提供一种CMOS器件及其制作方法,于具有SiO2层的Si衬底中分别形成第一深度的第一凹槽及大于所述第一深度的第二深度的第二凹槽,于所述第一凹槽及第二凹槽内分别形成Ge层、止刻层以及Ⅲ-Ⅴ族半导体层,然后采用选择性腐蚀技术刻蚀上述结构至所述第一凹槽内的Ge层,并使所述Ge层、SiO2层及Ⅲ-Ⅴ族半导体层处于同一平面,最后在所述Ge层上制作PMOS器件,在所述Ⅲ-Ⅴ族半导体层上制作NMOS器件以完成所述CMOS器件的制作。本发明只需在外延后通过选择性腐蚀工艺及抛光工艺即可获得具有Ge层及Ⅲ-Ⅴ族半导体层