用于生产晶片级封装体的方法和对应的半导体封装体.pdf

增梅****主啊

亲,该文档总共19页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

用于生产晶片级封装体的方法和对应的半导体封装体.pdf

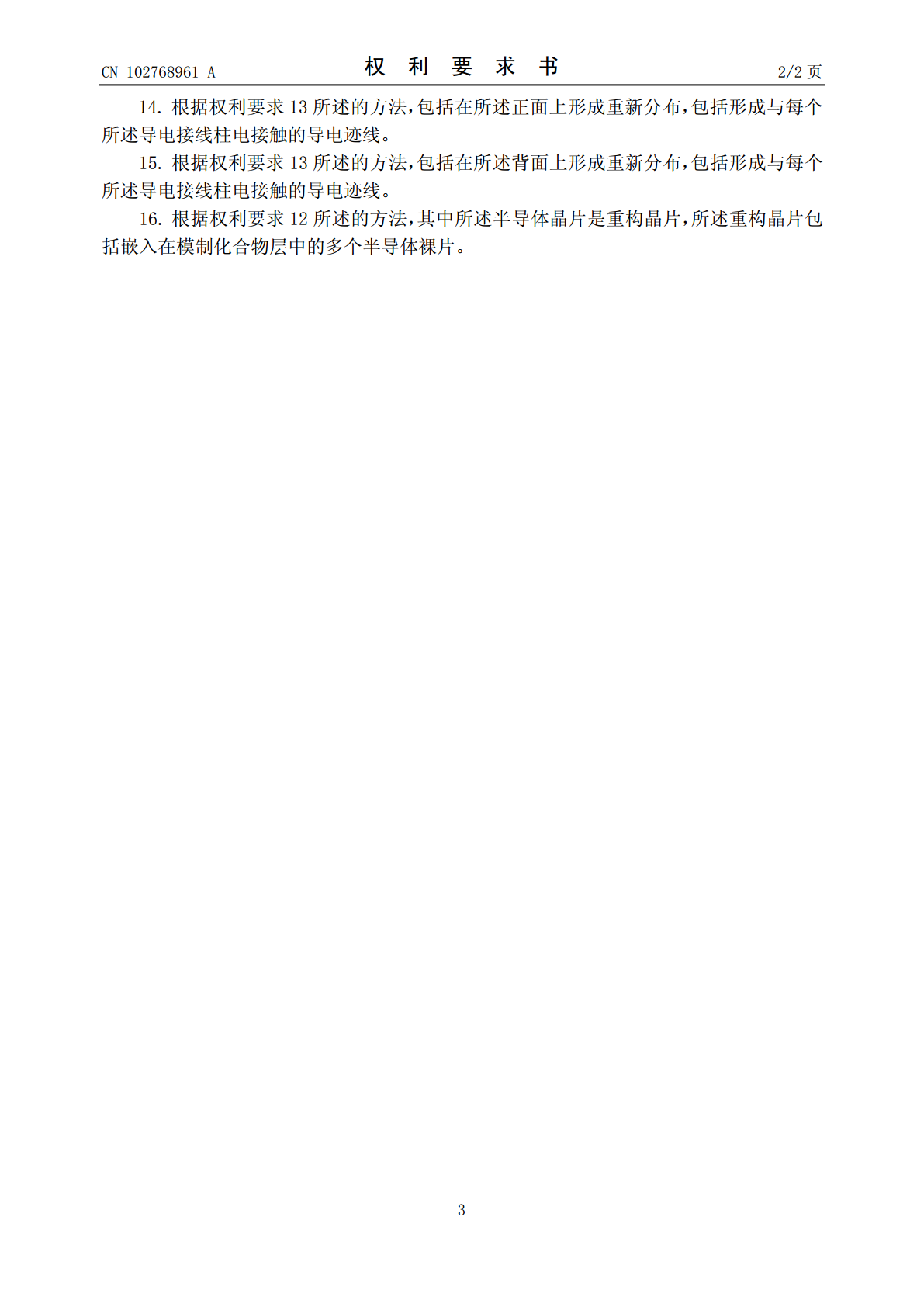

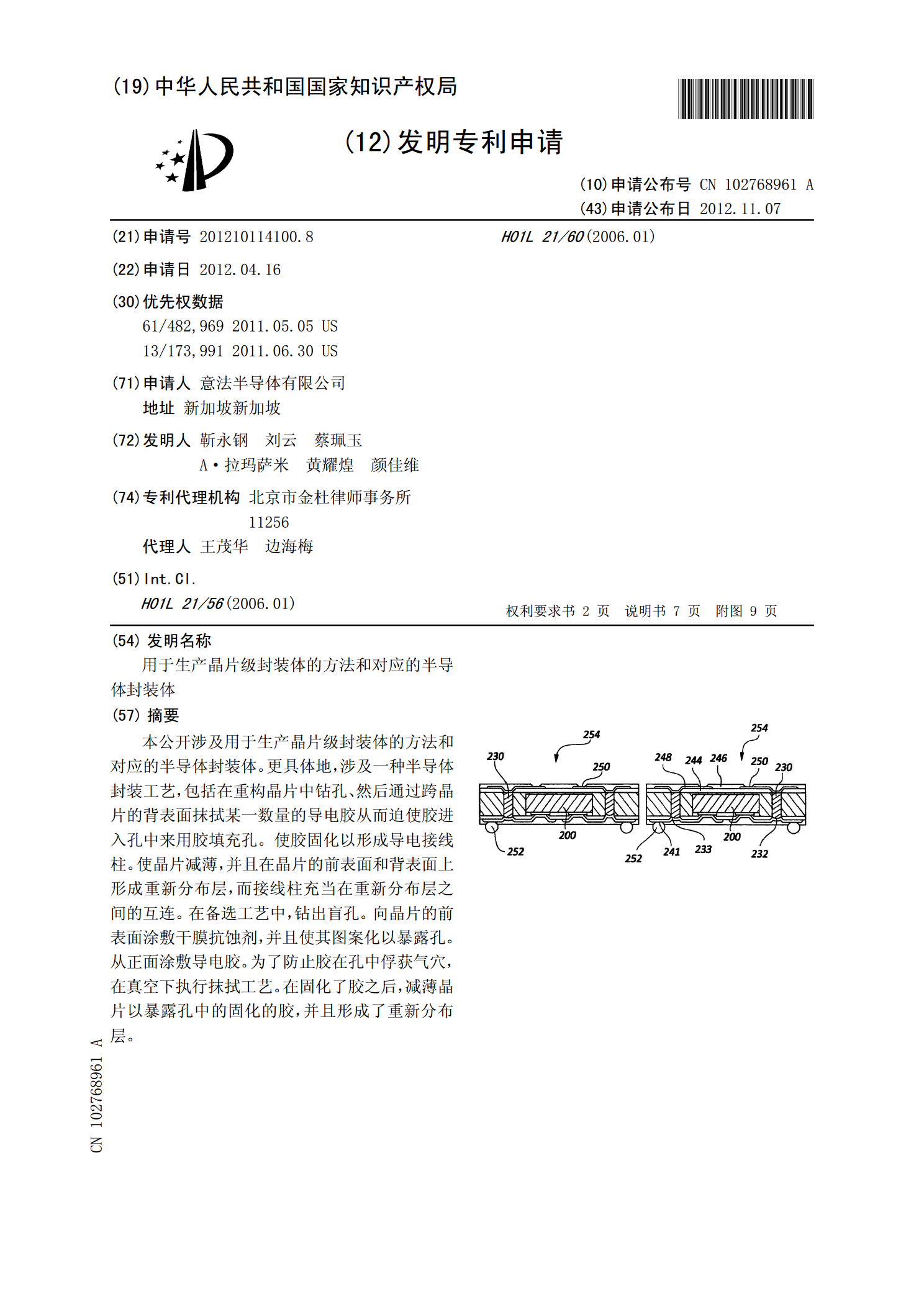

本公开涉及用于生产晶片级封装体的方法和对应的半导体封装体。更具体地,涉及一种半导体封装工艺,包括在重构晶片中钻孔、然后通过跨晶片的背表面抹拭某一数量的导电胶从而迫使胶进入孔中来用胶填充孔。使胶固化以形成导电接线柱。使晶片减薄,并且在晶片的前表面和背表面上形成重新分布层,而接线柱充当在重新分布层之间的互连。在备选工艺中,钻出盲孔。向晶片的前表面涂敷干膜抗蚀剂,并且使其图案化以暴露孔。从正面涂敷导电胶。为了防止胶在孔中俘获气穴,在真空下执行抹拭工艺。在固化了胶之后,减薄晶片以暴露孔中的固化的胶,并且形成了重新

晶片封装体.pdf

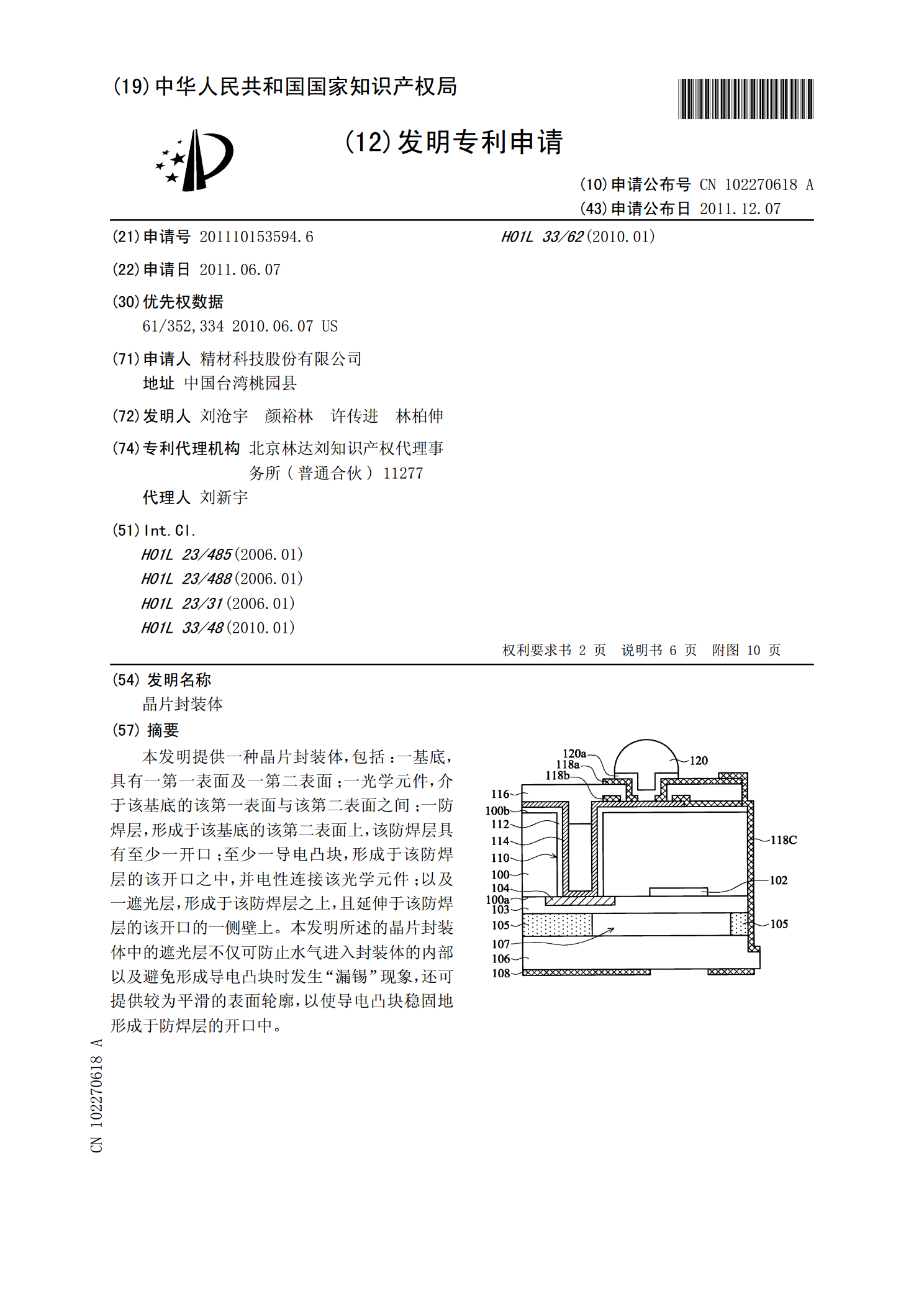

本发明提供一种晶片封装体,包括:一基底,具有一第一表面及一第二表面;一光学元件,介于该基底的该第一表面与该第二表面之间;一防焊层,形成于该基底的该第二表面上,该防焊层具有至少一开口;至少一导电凸块,形成于该防焊层的该开口之中,并电性连接该光学元件;以及一遮光层,形成于该防焊层之上,且延伸于该防焊层的该开口的一侧壁上。本发明所述的晶片封装体中的遮光层不仅可防止水气进入封装体的内部以及避免形成导电凸块时发生“漏锡”现象,还可提供较为平滑的表面轮廓,以使导电凸块稳固地形成于防焊层的开口中。

芯片封装方法及封装体.pdf

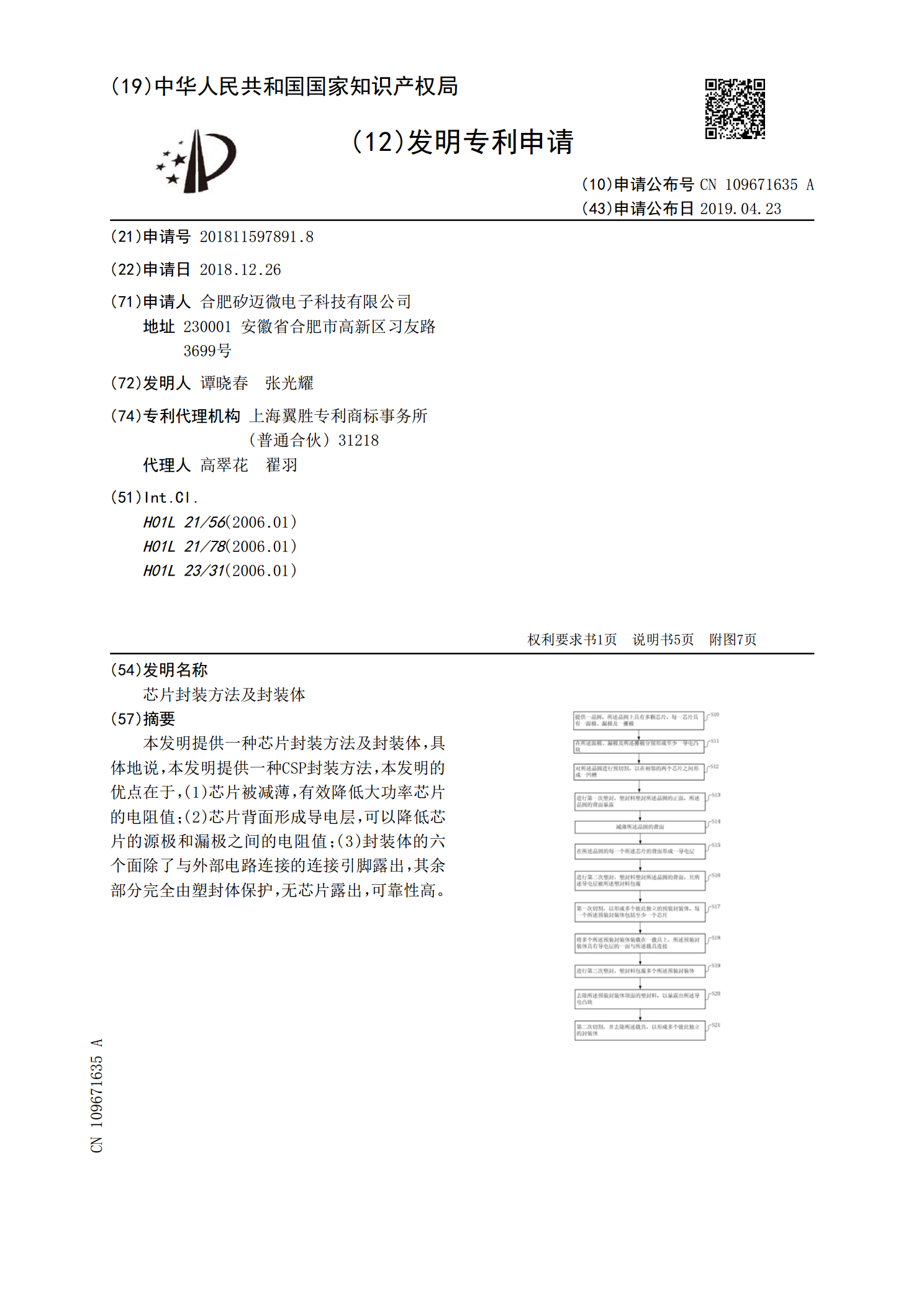

本发明提供一种芯片封装方法及封装体,具体地说,本发明提供一种CSP封装方法,本发明的优点在于,(1)芯片被减薄,有效降低大功率芯片的电阻值;(2)芯片背面形成导电层,可以降低芯片的源极和漏极之间的电阻值;(3)封装体的六个面除了与外部电路连接的连接引脚露出,其余部分完全由塑封体保护,无芯片露出,可靠性高。

用于实现超薄晶片级封装(WLP)的封装体的低成本、低轮廓的焊料凸点工艺.pdf

本发明公开了一种用于实现超薄晶片级封装(WLP)的封装体的低成本、低轮廓的焊料凸点工艺。具体而言,本文说明了用于浸焊工艺的技术,其提供了低轮廓、低成本的焊料凸点形成工艺,可以实施它以促进封装厚度缩放(例如减小总体封装厚度)。例如,本文公开的浸焊工艺可以实现超薄晶片级封装(WLP)、超薄晶片级方形扁平无引脚(WQFN)封装等。

封装母板、芯片的封装方法及封装体.pdf

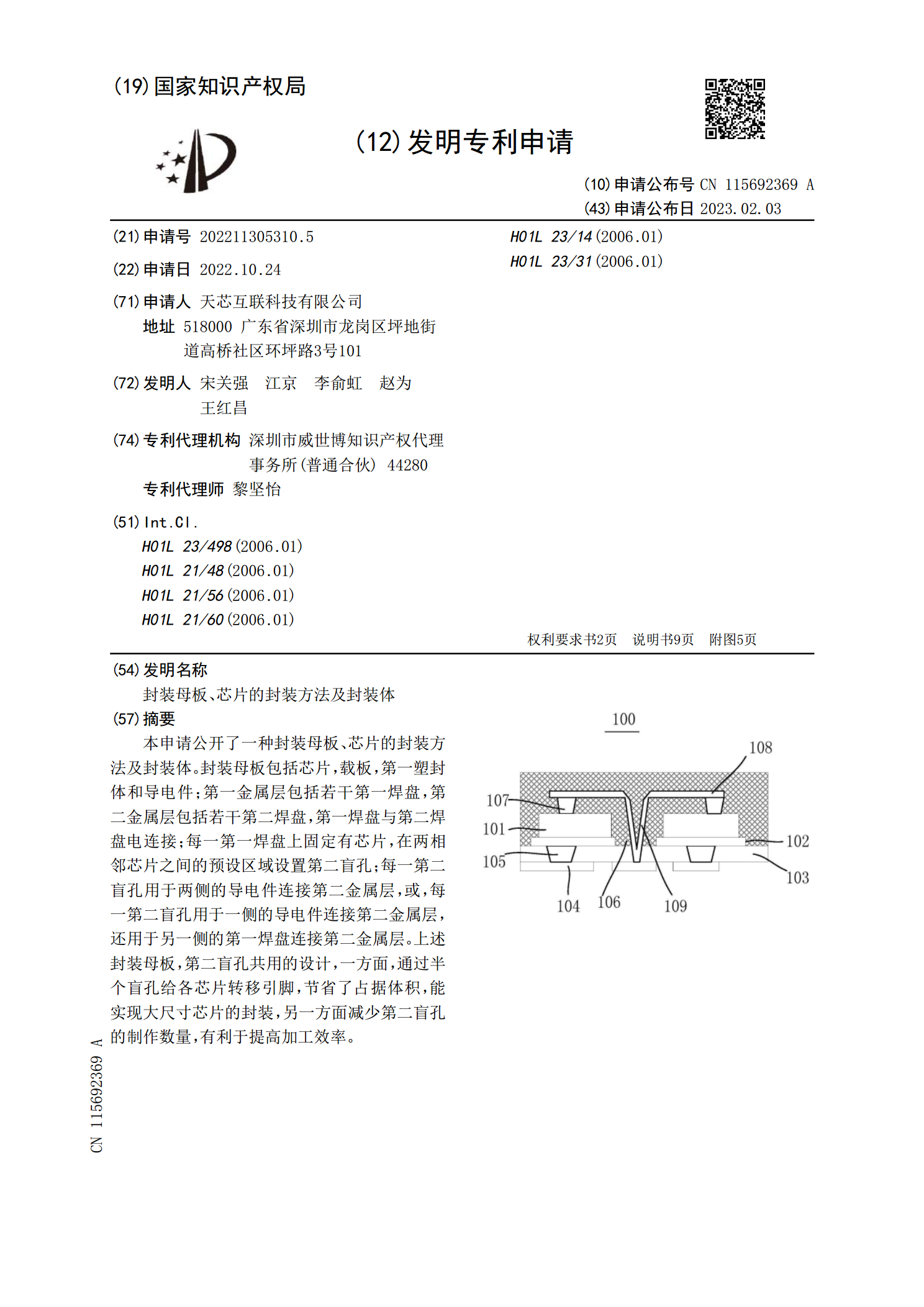

本申请公开了一种封装母板、芯片的封装方法及封装体。封装母板包括芯片,载板,第一塑封体和导电件;第一金属层包括若干第一焊盘,第二金属层包括若干第二焊盘,第一焊盘与第二焊盘电连接;每一第一焊盘上固定有芯片,在两相邻芯片之间的预设区域设置第二盲孔;每一第二盲孔用于两侧的导电件连接第二金属层,或,每一第二盲孔用于一侧的导电件连接第二金属层,还用于另一侧的第一焊盘连接第二金属层。上述封装母板,第二盲孔共用的设计,一方面,通过半个盲孔给各芯片转移引脚,节省了占据体积,能实现大尺寸芯片的封装,另一方面减少第二盲孔的制作