具有高可靠性的分离栅VDMOS器件及其制造方法.pdf

夏萍****文章

亲,该文档总共16页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

具有高可靠性的分离栅VDMOS器件及其制造方法.pdf

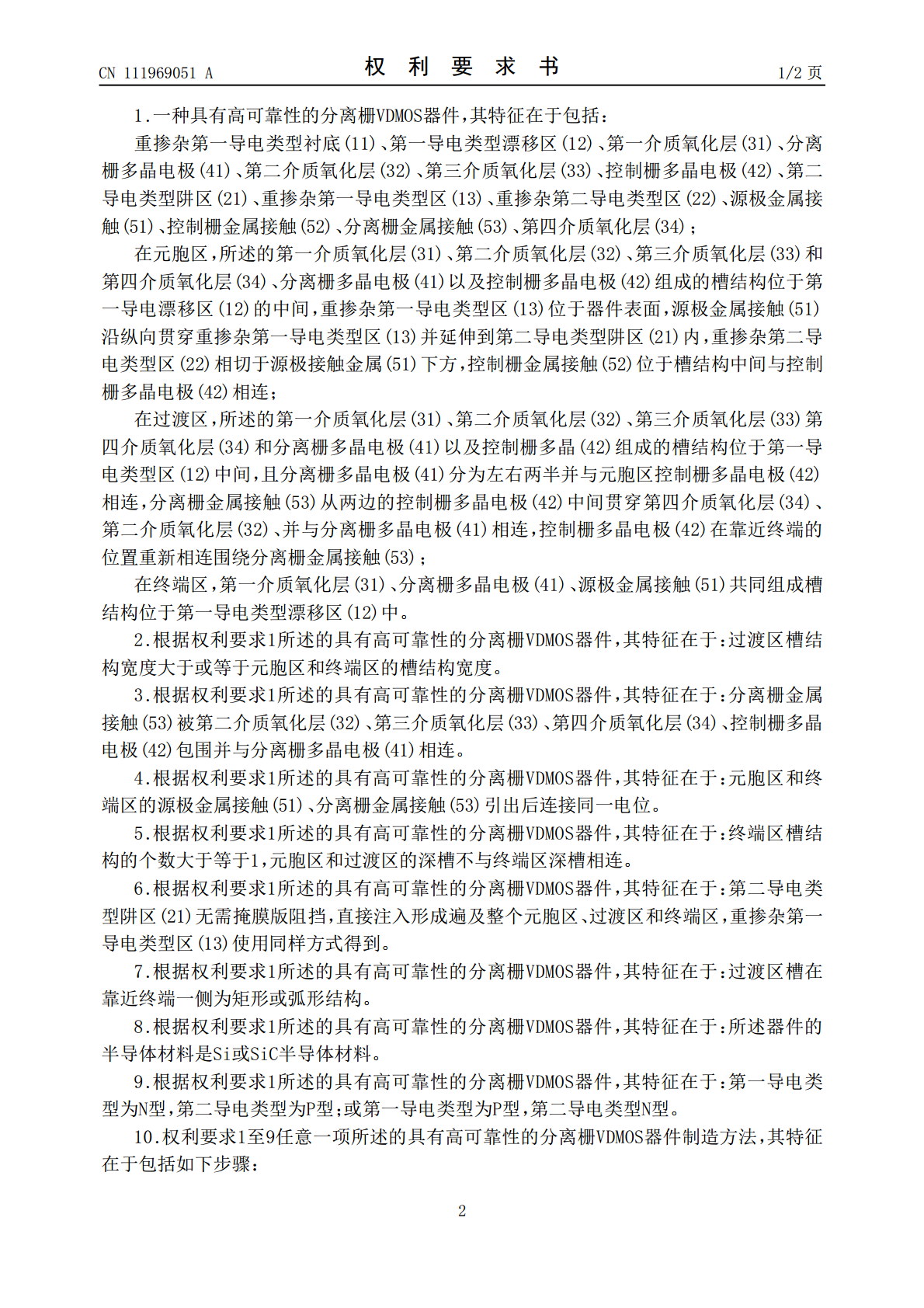

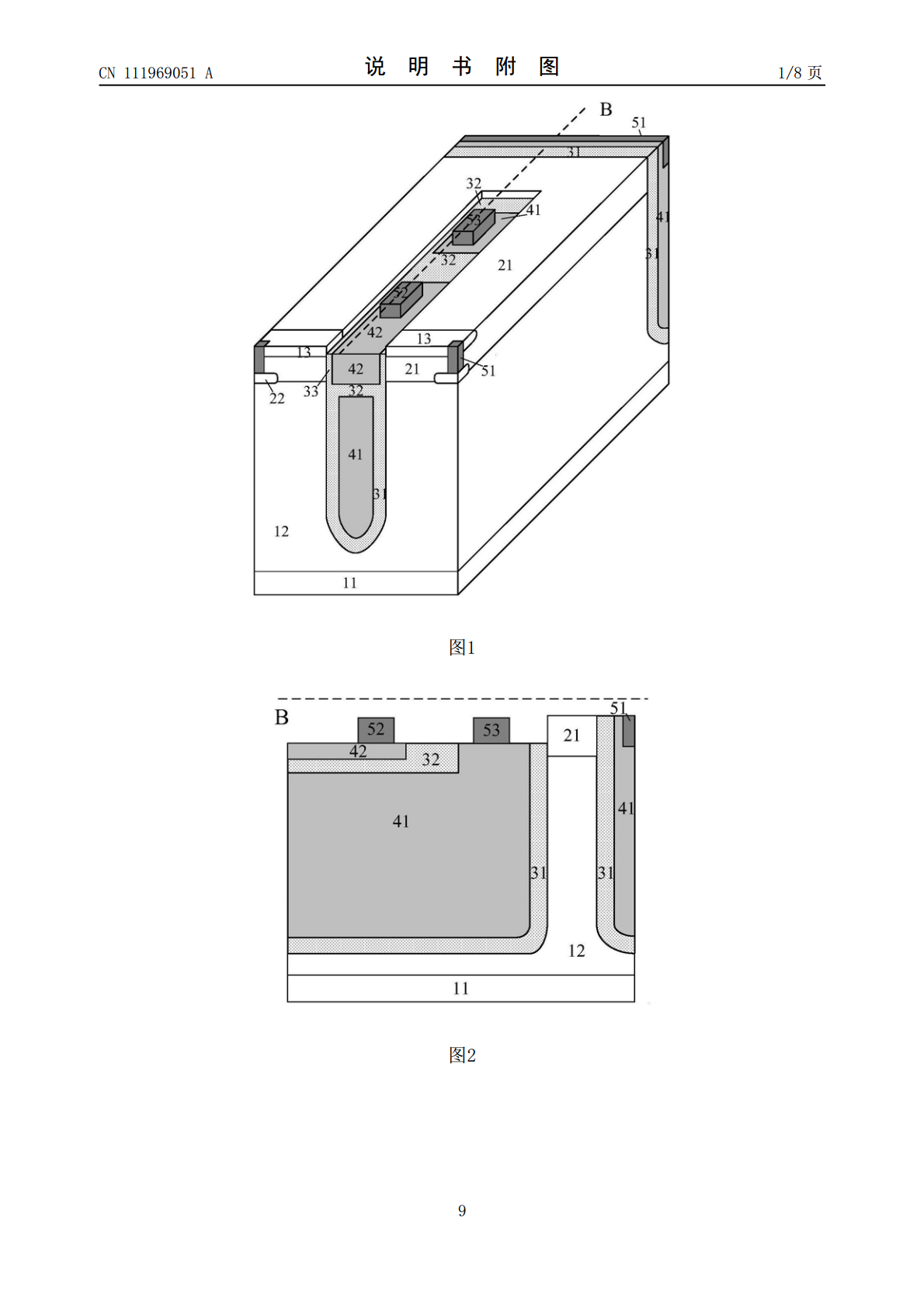

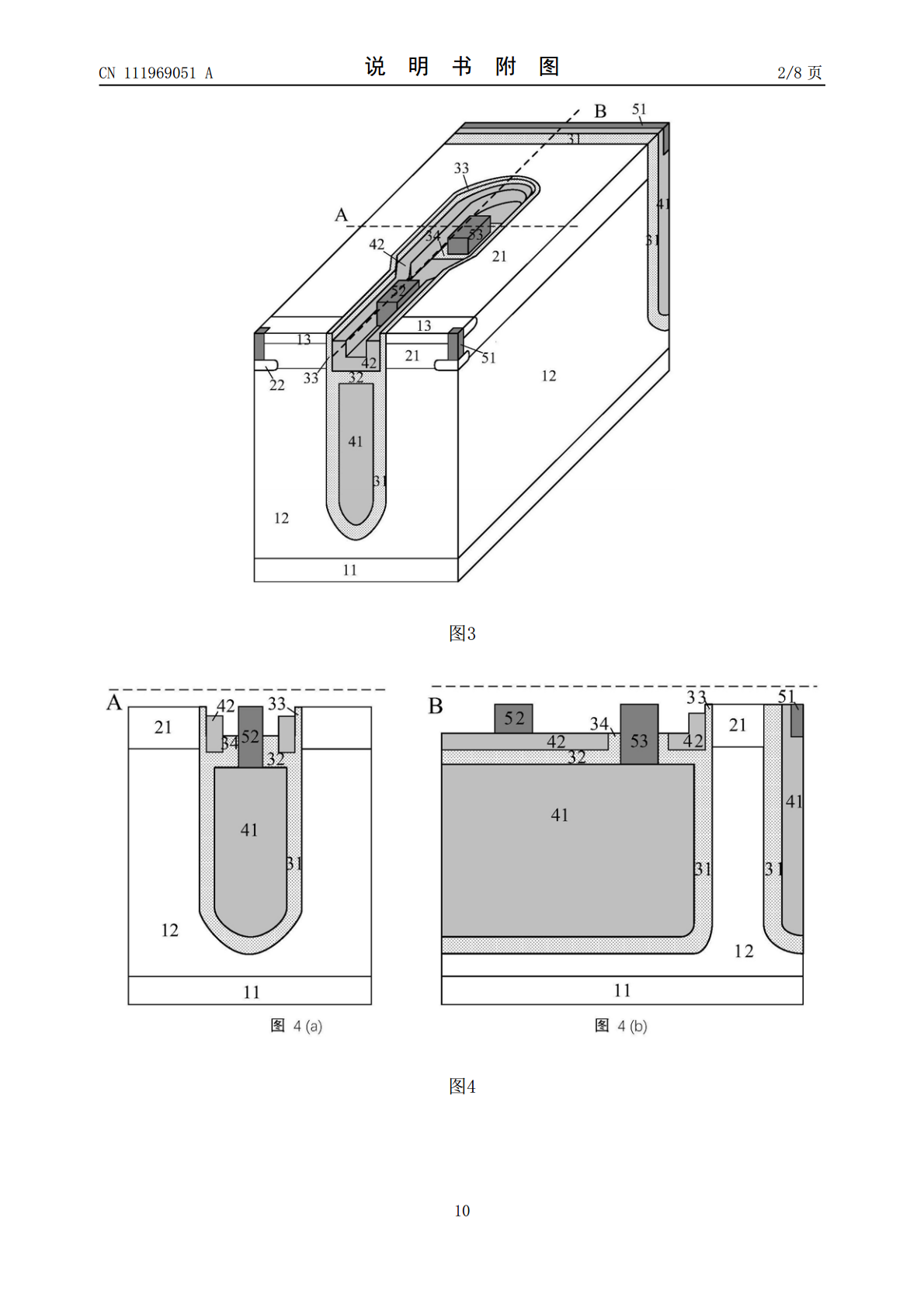

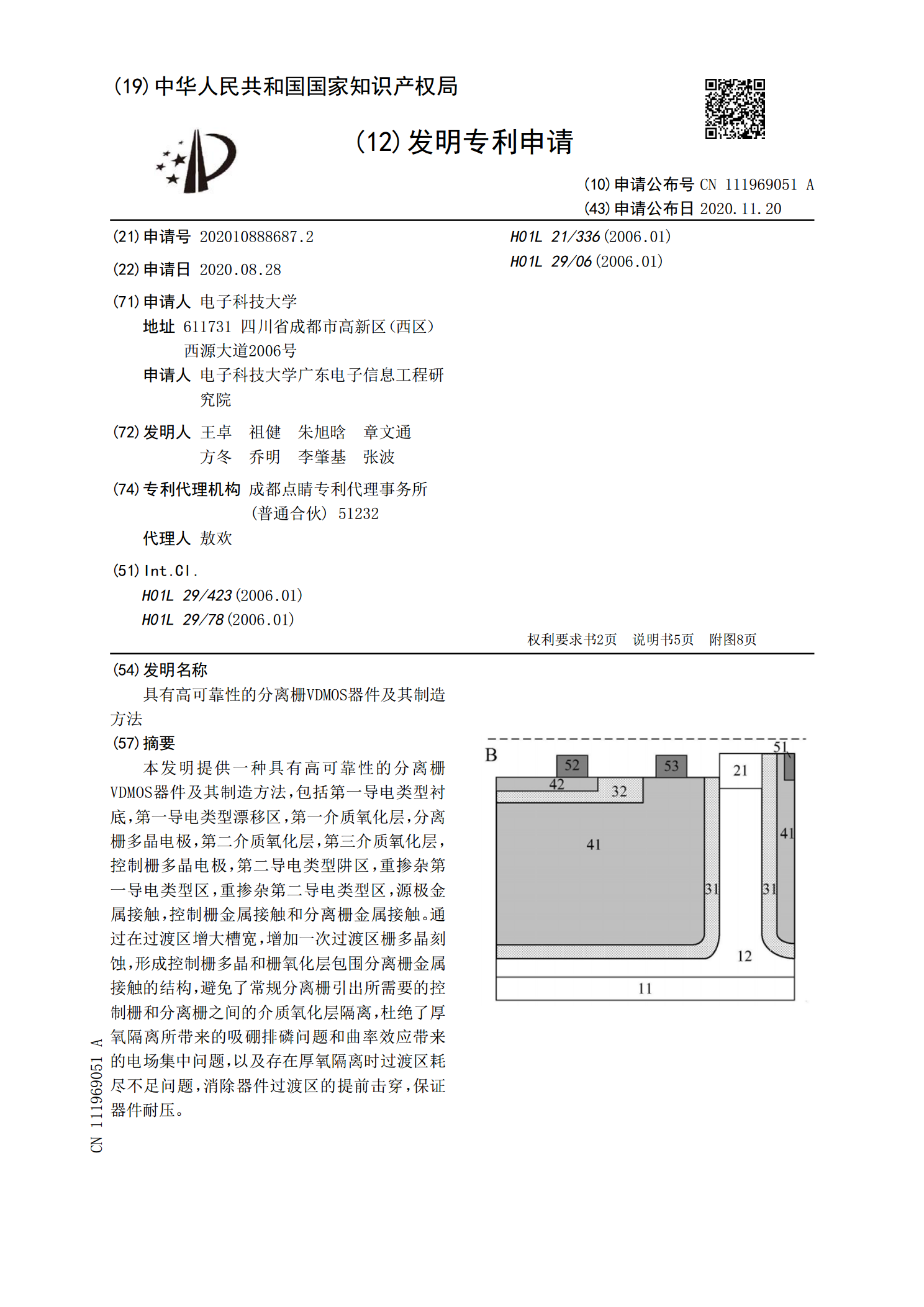

本发明提供一种具有高可靠性的分离栅VDMOS器件及其制造方法,包括第一导电类型衬底,第一导电类型漂移区,第一介质氧化层,分离栅多晶电极,第二介质氧化层,第三介质氧化层,控制栅多晶电极,第二导电类型阱区,重掺杂第一导电类型区,重掺杂第二导电类型区,源极金属接触,控制栅金属接触和分离栅金属接触。通过在过渡区增大槽宽,增加一次过渡区栅多晶刻蚀,形成控制栅多晶和栅氧化层包围分离栅金属接触的结构,避免了常规分离栅引出所需要的控制栅和分离栅之间的介质氧化层隔离,杜绝了厚氧隔离所带来的吸硼排磷问题和曲率效应带来的电场集

具有屏蔽栅的VDMOS器件及其制备方法.pdf

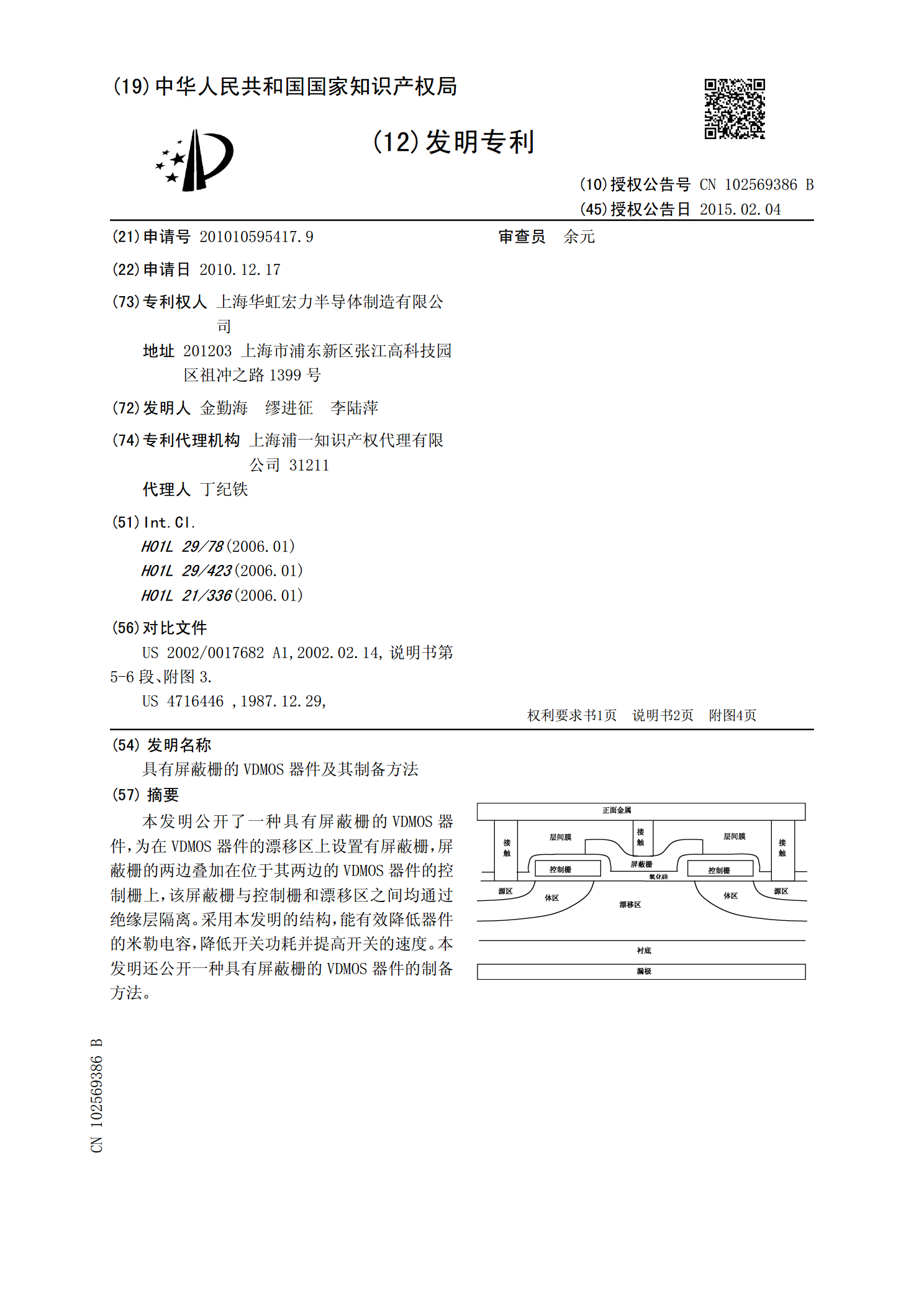

本发明公开了一种具有屏蔽栅的VDMOS器件,为在VDMOS器件的漂移区上设置有屏蔽栅,屏蔽栅的两边叠加在位于其两边的VDMOS器件的控制栅上,该屏蔽栅与控制栅和漂移区之间均通过绝缘层隔离。采用本发明的结构,能有效降低器件的米勒电容,降低开关功耗并提高开关的速度。本发明还公开一种具有屏蔽栅的VDMOS器件的制备方法。

分离栅功率MOS器件及其制造方法.pdf

公开了一种分离栅功率MOS器件及其制造方法,方法包括:在衬底上形成外延层,在外延层中形成沟槽;在外延层表面和沟槽中形成第一绝缘层;在空腔中填充多晶硅并进行回蚀刻;在第一栅极导体的表面旋转涂布形成第二绝缘层;在第二绝缘层上形成掩膜,去除外延层表面和沟槽中所述掩膜侧壁的第一绝缘层,暴露沟槽的上部;在沟槽上部的侧壁和外延层的表面形成栅氧化层;在沟槽的上部中形成第二栅极导体。本申请的分离栅功率MOS器件的制造方法中,采用SOG工艺形成第二绝缘层,在回蚀刻第一绝缘层时采用掩膜保护第二绝缘层,降低了第二绝缘层厚度过厚

VDMOS器件及其制造方法.pdf

本发明提供一种VDMOS器件及其制造方法,所述器件包括结构相同的元胞单元;各元胞单元构成元胞水平结构;所述元胞水平结构,包括:若干个并列的源区,和围绕各所述源区的栅极区;各所述栅极区于延伸方向上交汇重叠形成栅极交汇区,其余的形成栅极非交汇区;于所述栅极交汇区设有分隔区;于所述元胞单元对应所述栅极非交汇区设有JFET区;于所述元胞单元对应所述分隔区设有JFET隔断区;所述JFET隔断区处不同导电类型的掺杂离子浓度差大于所述JFET区处浓度差,使栅极交汇区于斜线方向上的耗尽层易于扩展,从而耗尽层更易于接触和融

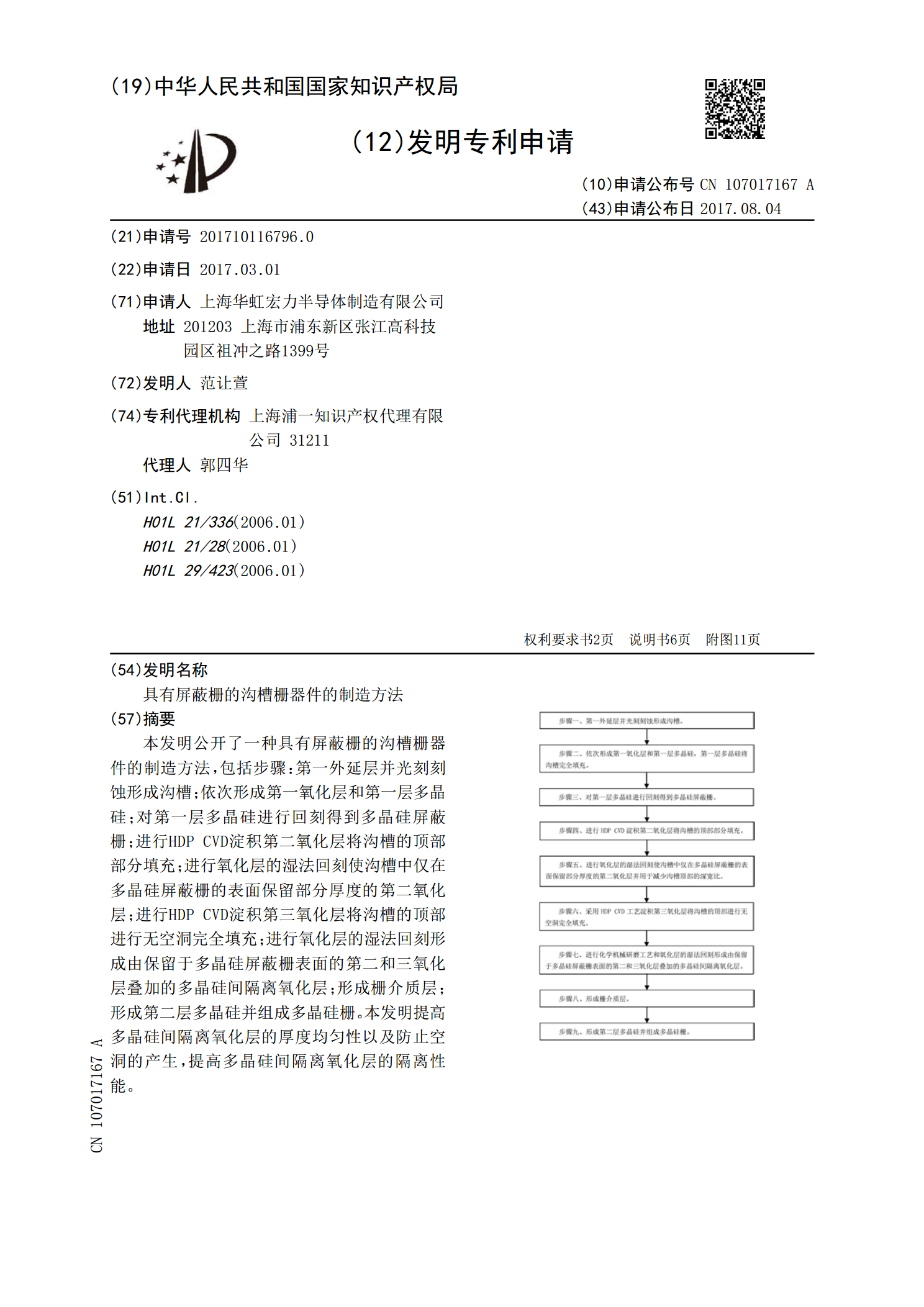

具有屏蔽栅的沟槽栅器件的制造方法.pdf

本发明公开了一种具有屏蔽栅的沟槽栅器件的制造方法,包括步骤:第一外延层并光刻刻蚀形成沟槽;依次形成第一氧化层和第一层多晶硅;对第一层多晶硅进行回刻得到多晶硅屏蔽栅;进行HDPCVD淀积第二氧化层将沟槽的顶部部分填充;进行氧化层的湿法回刻使沟槽中仅在多晶硅屏蔽栅的表面保留部分厚度的第二氧化层;进行HDPCVD淀积第三氧化层将沟槽的顶部进行无空洞完全填充;进行氧化层的湿法回刻形成由保留于多晶硅屏蔽栅表面的第二和三氧化层叠加的多晶硅间隔离氧化层;形成栅介质层;形成第二层多晶硅并组成多晶硅栅。本发明提高多晶硅