半导体薄膜制备装置及制备方法.pdf

夏萍****文章

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

半导体薄膜制备装置及制备方法.pdf

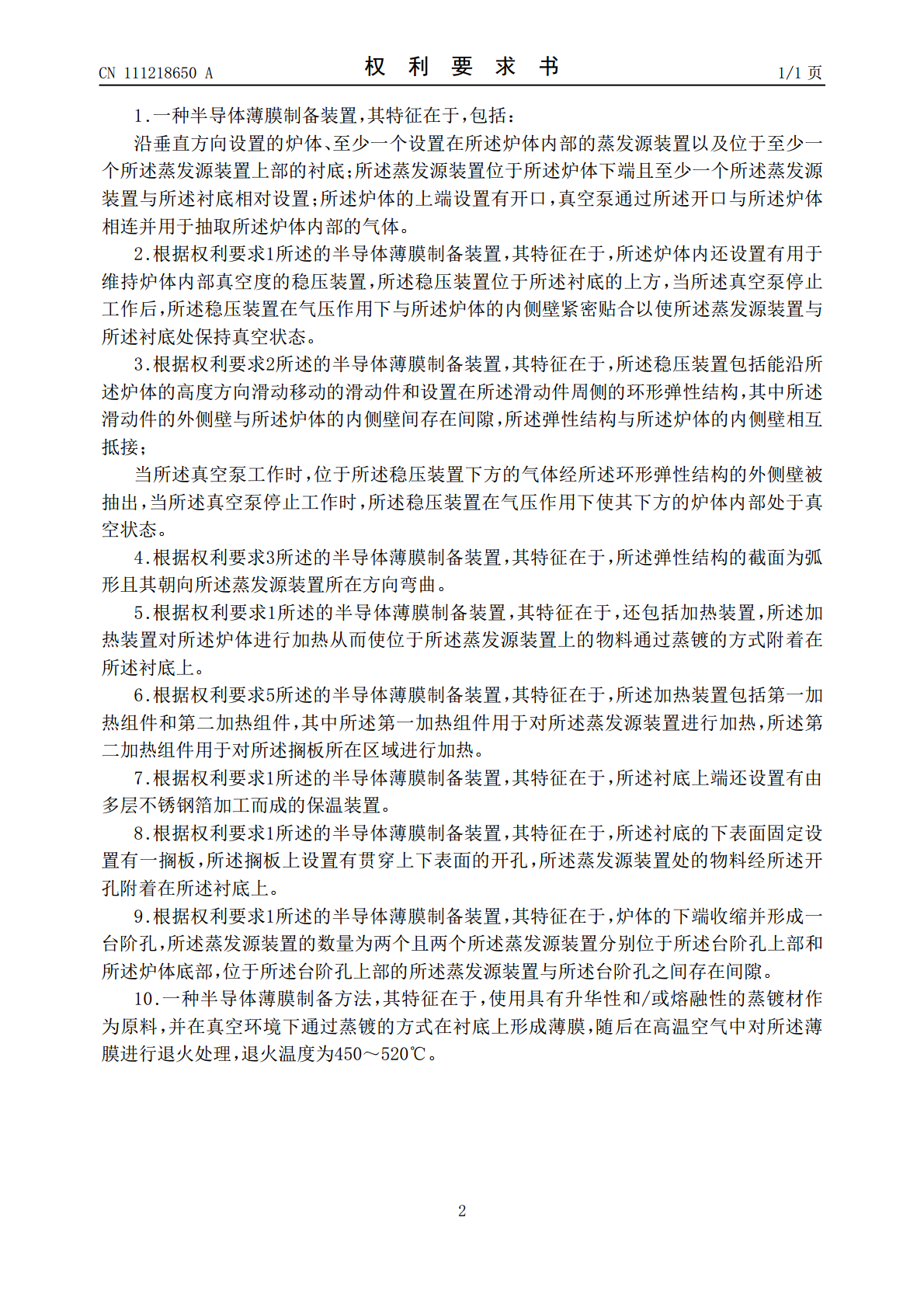

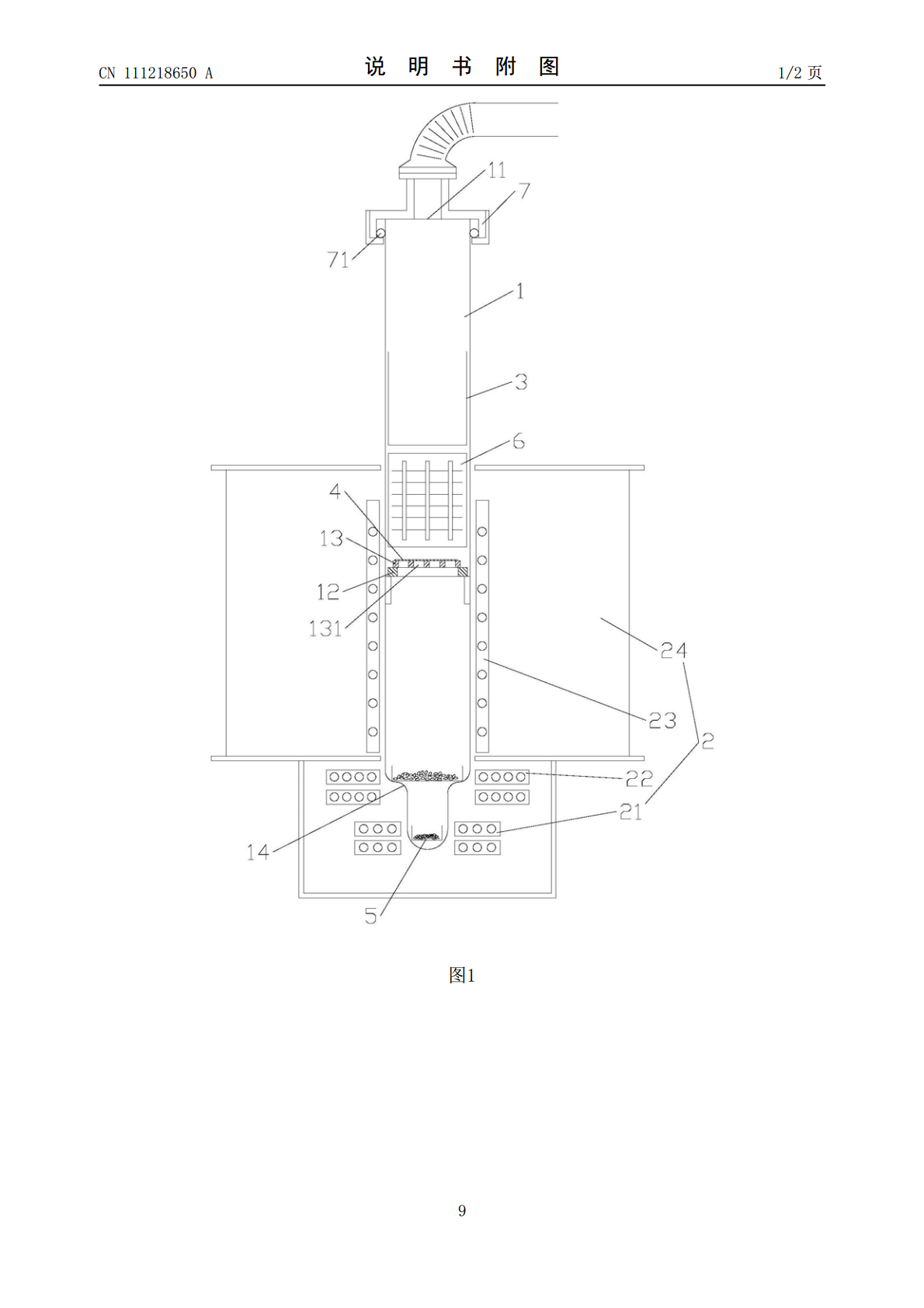

本发明提供了一种半导体薄膜制备装置及制备方法,涉及半导体薄膜加工技术领域,主要目的是解决现有技术中存在的薄膜厚度较薄的技术问题。该半导体薄膜制备装置,包括:沿垂直方向设置的炉体、至少一个设置在所述炉体内部的蒸发源装置以及位于至少一个所述蒸发源装置上部的衬底;所述蒸发源装置位于所述炉体下端且至少一个所述蒸发源装置与所述衬底相对设置;所述炉体的上端设置有开口,真空泵通过所述开口与所述炉体相连并用于抽取所述炉体内部的气体。当该半导体薄膜制备装置启动时,蒸发源装置与衬底所在处均处于真空状态,位于蒸发源装置上的物料

一种半导体薄膜的制备方法.pdf

本发明公开了一种半导体薄膜的制备方法,包括以下步骤:S101.提供基底;S102.在基底上形成薄膜;S103.在薄膜上通过涂胶、曝光和显影光刻自定义图形:光刻胶形成掩蔽层,在没有光刻胶的薄膜部分形成腐蚀窗口;S104.真空条件下,对腐蚀窗口内的薄膜进行湿法腐蚀;S105.去除显影后剩余的光刻胶。本发明有效解决了腐蚀过程中气泡残留的问题,保证了腐蚀的均匀性,提高了产品的整体良品率。

半导体装置及其制备方法.pdf

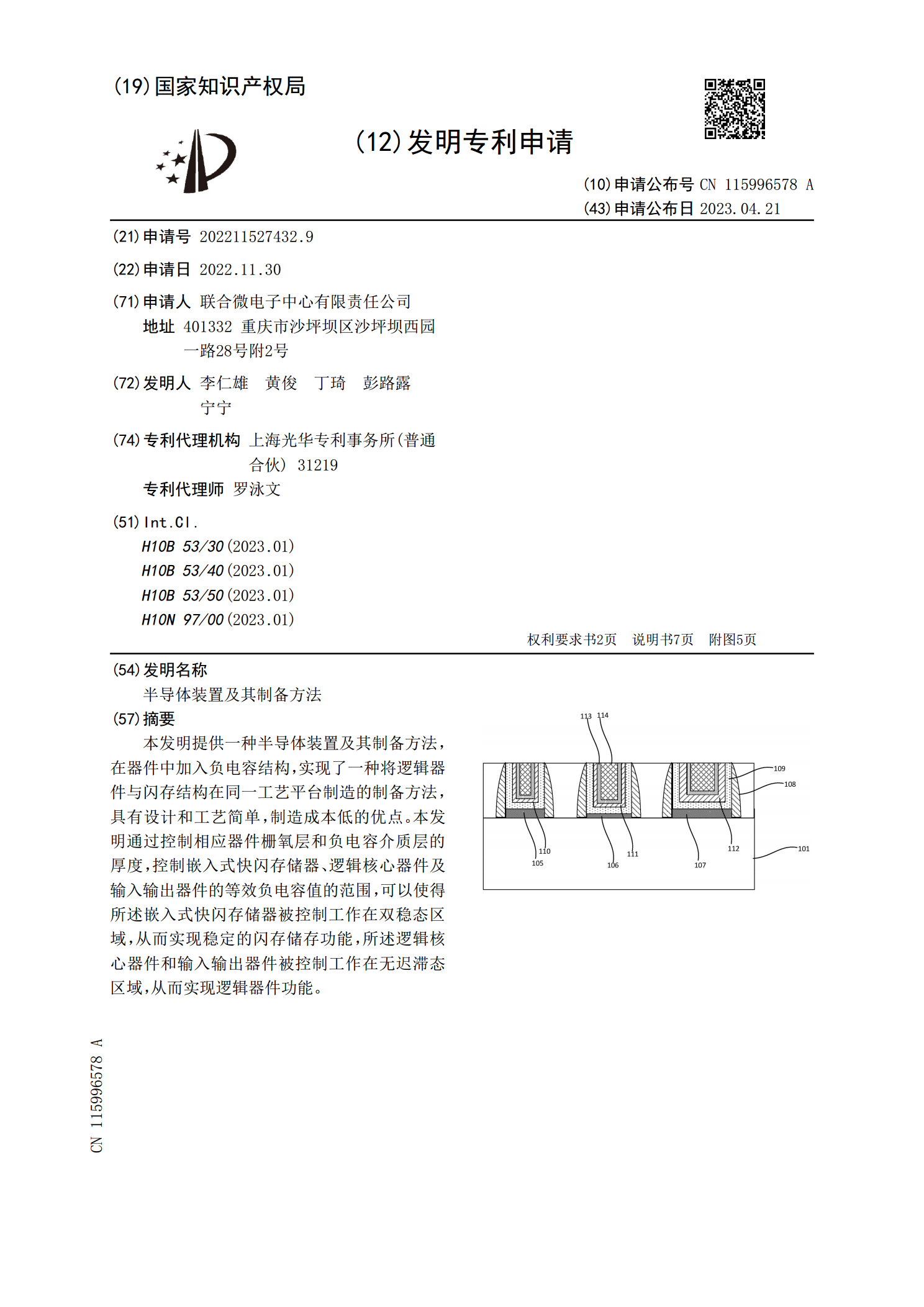

本发明提供一种半导体装置及其制备方法,在器件中加入负电容结构,实现了一种将逻辑器件与闪存结构在同一工艺平台制造的制备方法,具有设计和工艺简单,制造成本低的优点。本发明通过控制相应器件栅氧层和负电容介质层的厚度,控制嵌入式快闪存储器、逻辑核心器件及输入输出器件的等效负电容值的范围,可以使得所述嵌入式快闪存储器被控制工作在双稳态区域,从而实现稳定的闪存储存功能,所述逻辑核心器件和输入输出器件被控制工作在无迟滞态区域,从而实现逻辑器件功能。

半导体装置的制备方法和半导体装置.pdf

本发明公开了一种半导体装置的制备方法和半导体装置,包括:提供第一衬底,并在第一衬底表面形成第一非金属键合材料层;提供第二衬底,并在第二衬底表面形成器件材料层;在器件材料层表面形成第二非金属键合材料层;将第二非金属键合材料层和第一非金属键合材料层进行键合形成非金属键合层;去除第二衬底;对器件材料层进行图形化刻蚀以获得含有至少一个半导体器件的器件层。本发明通过非金属键合方式,避免了金属键合后图形化刻蚀金属四溢以及清洗金属粒子残留导致的漏电问题,本发明通过非金属键合方式,形成了有效的刻蚀高选择比,增加了工艺窗口

半导体结构的制备方法及半导体结构的制备装置.pdf

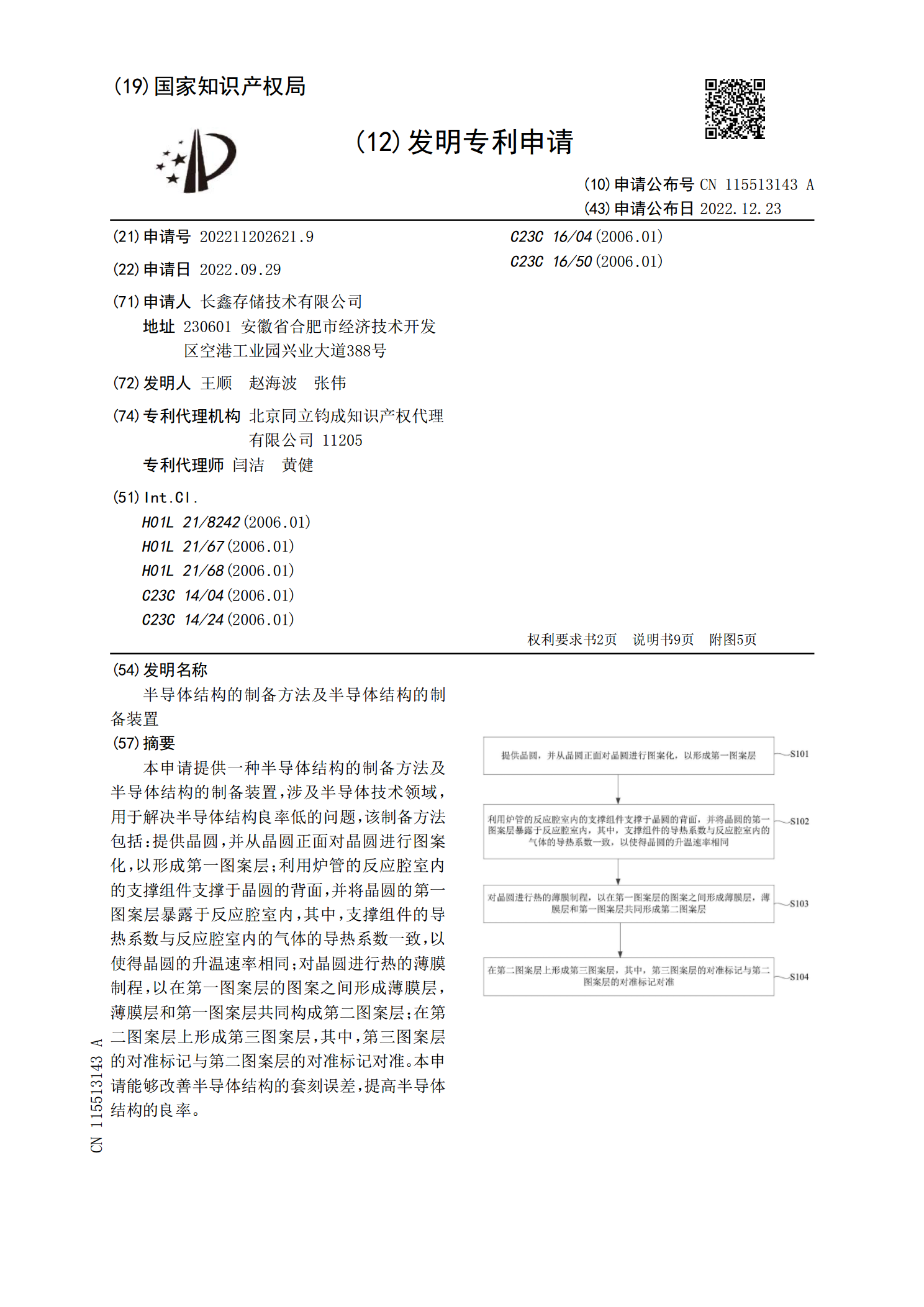

本申请提供一种半导体结构的制备方法及半导体结构的制备装置,涉及半导体技术领域,用于解决半导体结构良率低的问题,该制备方法包括:提供晶圆,并从晶圆正面对晶圆进行图案化,以形成第一图案层;利用炉管的反应腔室内的支撑组件支撑于晶圆的背面,并将晶圆的第一图案层暴露于反应腔室内,其中,支撑组件的导热系数与反应腔室内的气体的导热系数一致,以使得晶圆的升温速率相同;对晶圆进行热的薄膜制程,以在第一图案层的图案之间形成薄膜层,薄膜层和第一图案层共同构成第二图案层;在第二图案层上形成第三图案层,其中,第三图案层的对准标记与