多晶硅的沉积方法及接触插塞的制造方法.pdf

努力****绮亦

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

多晶硅的沉积方法及接触插塞的制造方法.pdf

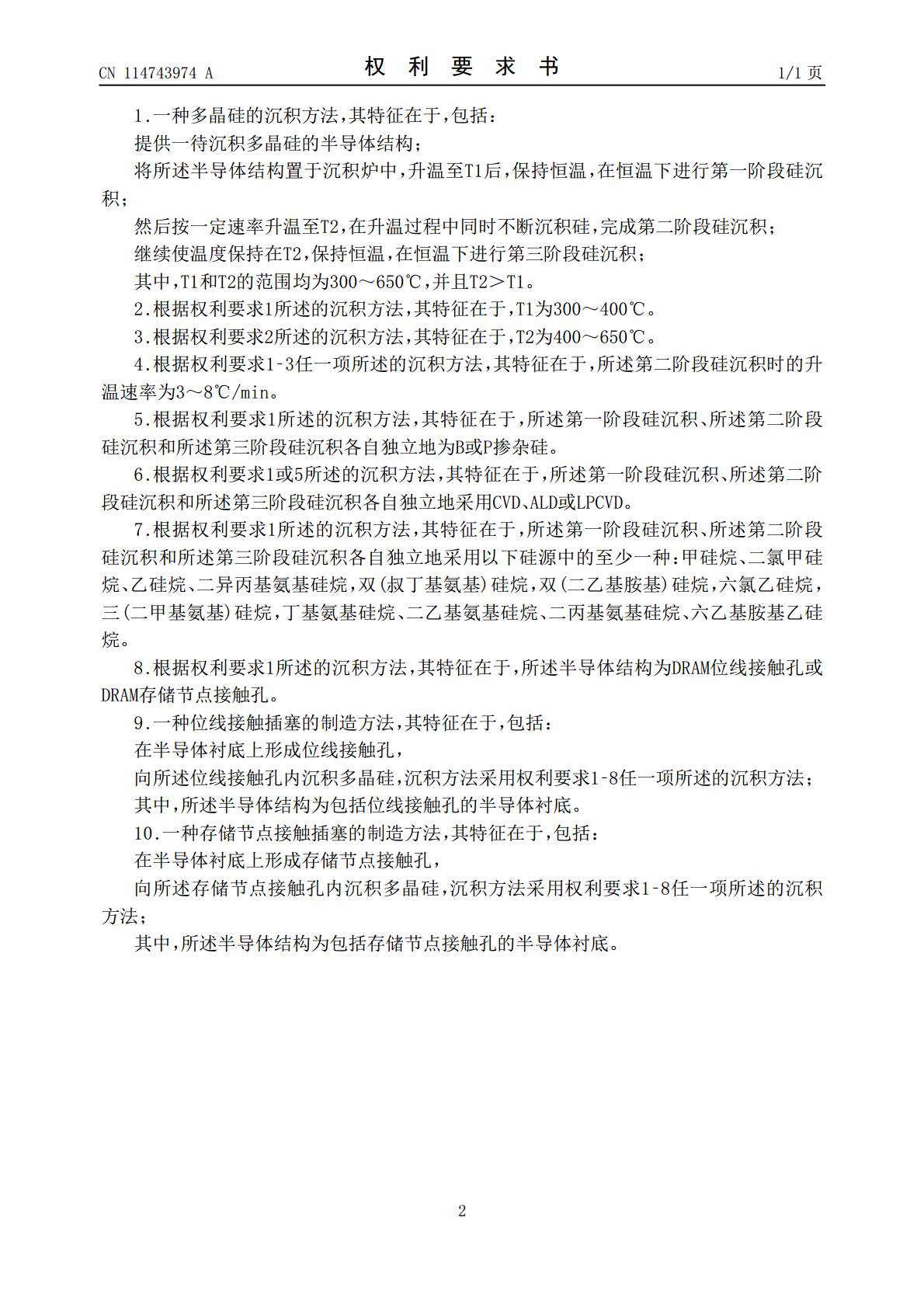

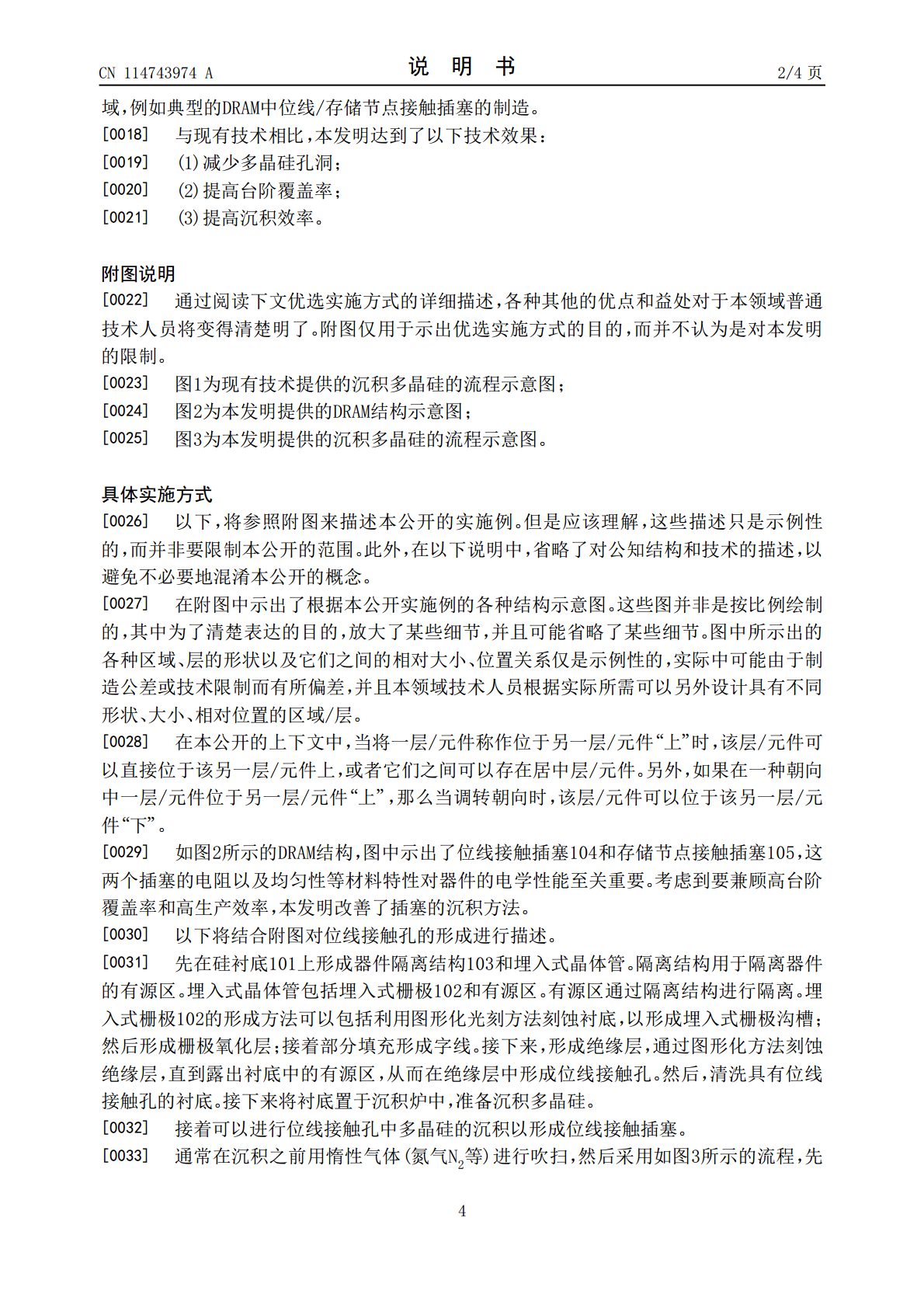

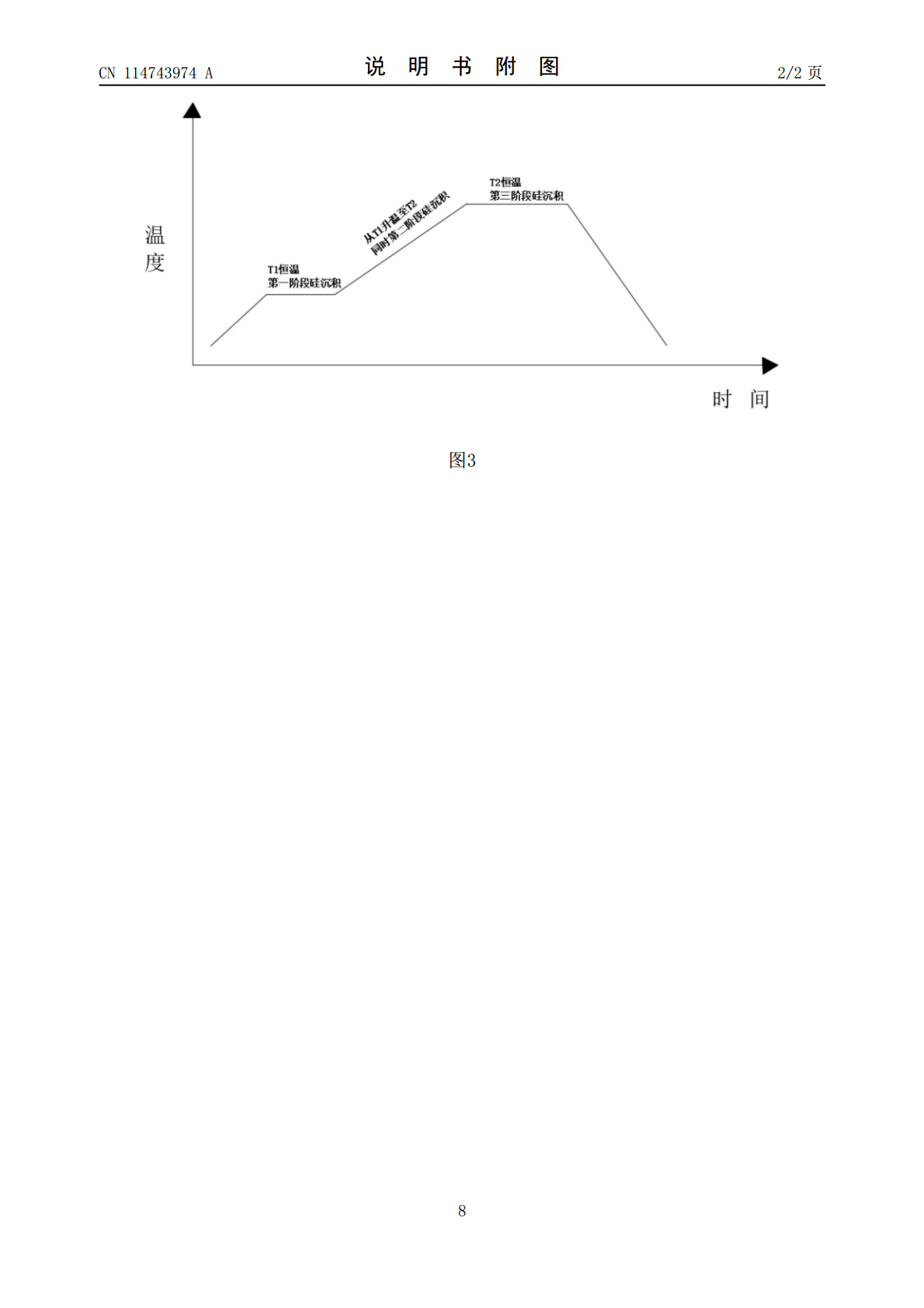

本发明涉及多晶硅的沉积方法及位线/存储节点接触插塞的制造方法。一种多晶硅的沉积方法,包括:提供一待沉积多晶硅的半导体结构;将所述半导体结构置于沉积炉中,升温至T1后,保持恒温,在恒温下进行第一阶段硅沉积;然后按一定速率升温至T2,在升温过程中同时不断沉积硅,完成第二阶段硅沉积;继续使温度保持在T2,保持恒温,在恒温下进行第三阶段硅沉积;其中,T1和T2的范围均为300~650℃,并且T2>T1。本发明用于凹槽内沉积时具有较高的台阶覆盖率,并且由于在升温过程中完成了部分硅沉积,沉积效率相比现有技术大幅提高。

接触孔插塞的制造方法.pdf

本发明提供一种接触孔插塞的制造方法。上述方法包括提供半导体基板;沉积导电牺牲层;于导电牺牲层上形成硬遮罩图案;移除未被硬遮罩图案覆盖的导电牺牲层,直到半导体基板的电晶体结构顶部的氧化保护层暴露出来为止;移除未被硬遮罩图案覆盖的导电牺牲层,形成底部互连的导电牺牲图案;于导电牺牲图案的侧壁上形成氧化保护层;移除未被硬遮罩图案覆盖的部分氧化保护层和导电牺牲图案;移除未被硬遮罩图案覆盖的导电牺牲图案的底部,以形成导电牺牲柱。本发明提供的一种接触孔插塞的制造方法,其具有高深宽比且具有垂直的侧壁轮廓,以改善已知技术的

接触插塞的形成方法.pdf

本发明提供了一种接触插塞的形成方法,在对形成有接触孔的基底执行清洗工艺之后,以及在向所述接触孔填充导电材料之前,增加了对所述基底执行的烘烤工艺。从而,使得接触孔中残留的清洗剂受热蒸发,实现了残留的清洗剂的去除,并使后续形成在接触孔中的接触插塞不会受到残留的清洗剂的影响。最终,保证了接触插塞的填充效果,保障了半导体器件与金属互连层的连接及电性能,提高了成品率。

接触插塞底部轮廓的检测方法.pdf

本发明提供了一种接触插塞底部轮廓的检测方法,该方法包括:提供一晶片,所述晶片包括形成有有源区的半导体基底、位于半导体基底上的第一介电层、贯穿第一介电层并与有源区电连接的接触插塞、形成于第一介电层和接触插塞上的第二介电层以及贯穿第二介电层并与接触插塞电连接的金属层;去除所述金属层和第二介电层;采用干法刻蚀的方式去除部分第一介电层;去除所述接触插塞以形成检测样片;以及采用扫描式电子显微镜检测所述检测样片。本发明可利用扫描式电子显微镜获取清晰的接触插塞底部轮廓的照片,并获得精确的检测结果。

开口结构及其形成方法、接触插塞及其形成方法.pdf

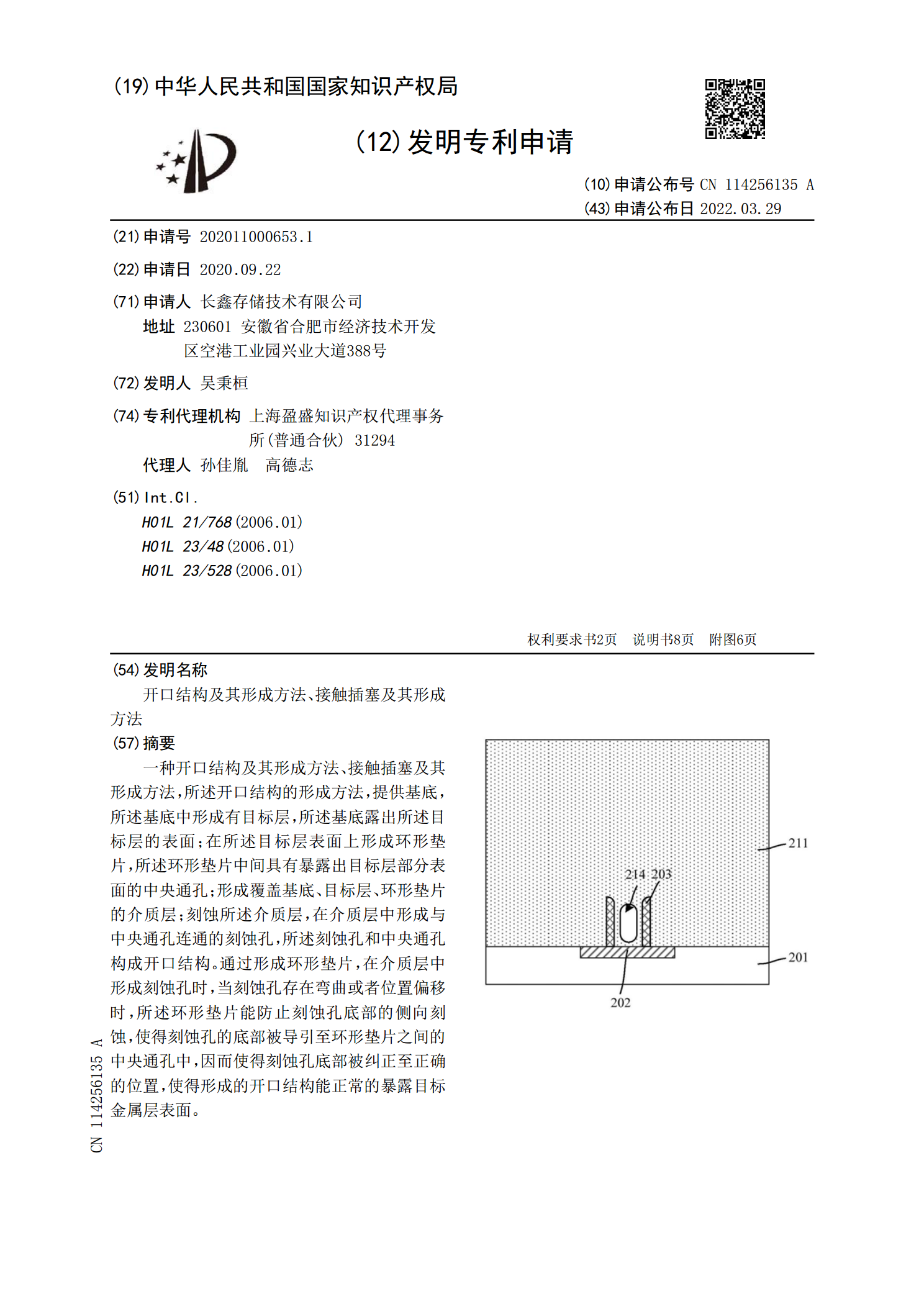

一种开口结构及其形成方法、接触插塞及其形成方法,所述开口结构的形成方法,提供基底,所述基底中形成有目标层,所述基底露出所述目标层的表面;在所述目标层表面上形成环形垫片,所述环形垫片中间具有暴露出目标层部分表面的中央通孔;形成覆盖基底、目标层、环形垫片的介质层;刻蚀所述介质层,在介质层中形成与中央通孔连通的刻蚀孔,所述刻蚀孔和中央通孔构成开口结构。通过形成环形垫片,在介质层中形成刻蚀孔时,当刻蚀孔存在弯曲或者位置偏移时,所述环形垫片能防止刻蚀孔底部的侧向刻蚀,使得刻蚀孔的底部被导引至环形垫片之间的中央通孔中