非交叠时钟信号产生电路.pdf

盼易****君a

亲,该文档总共13页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

非交叠时钟信号产生电路.pdf

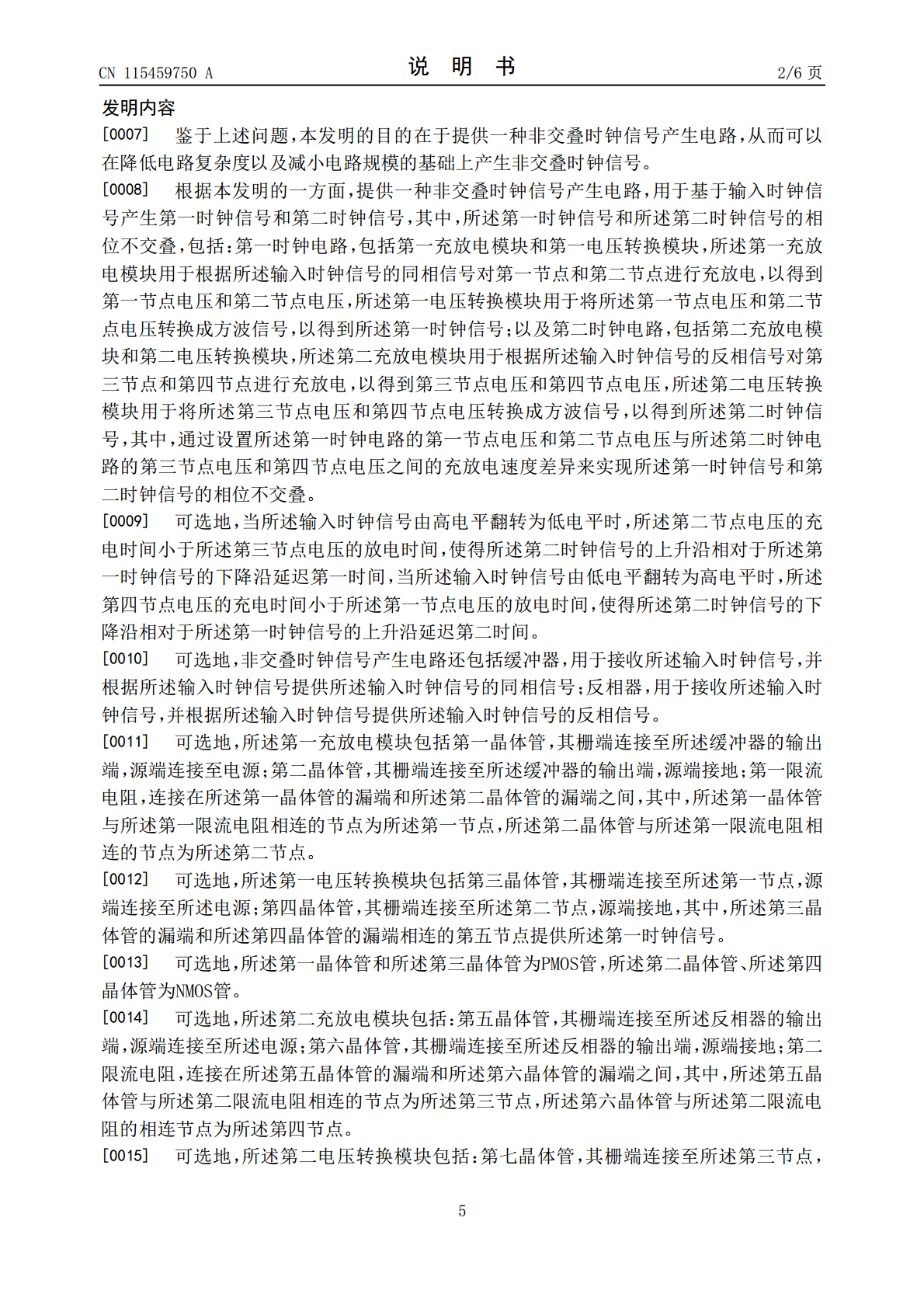

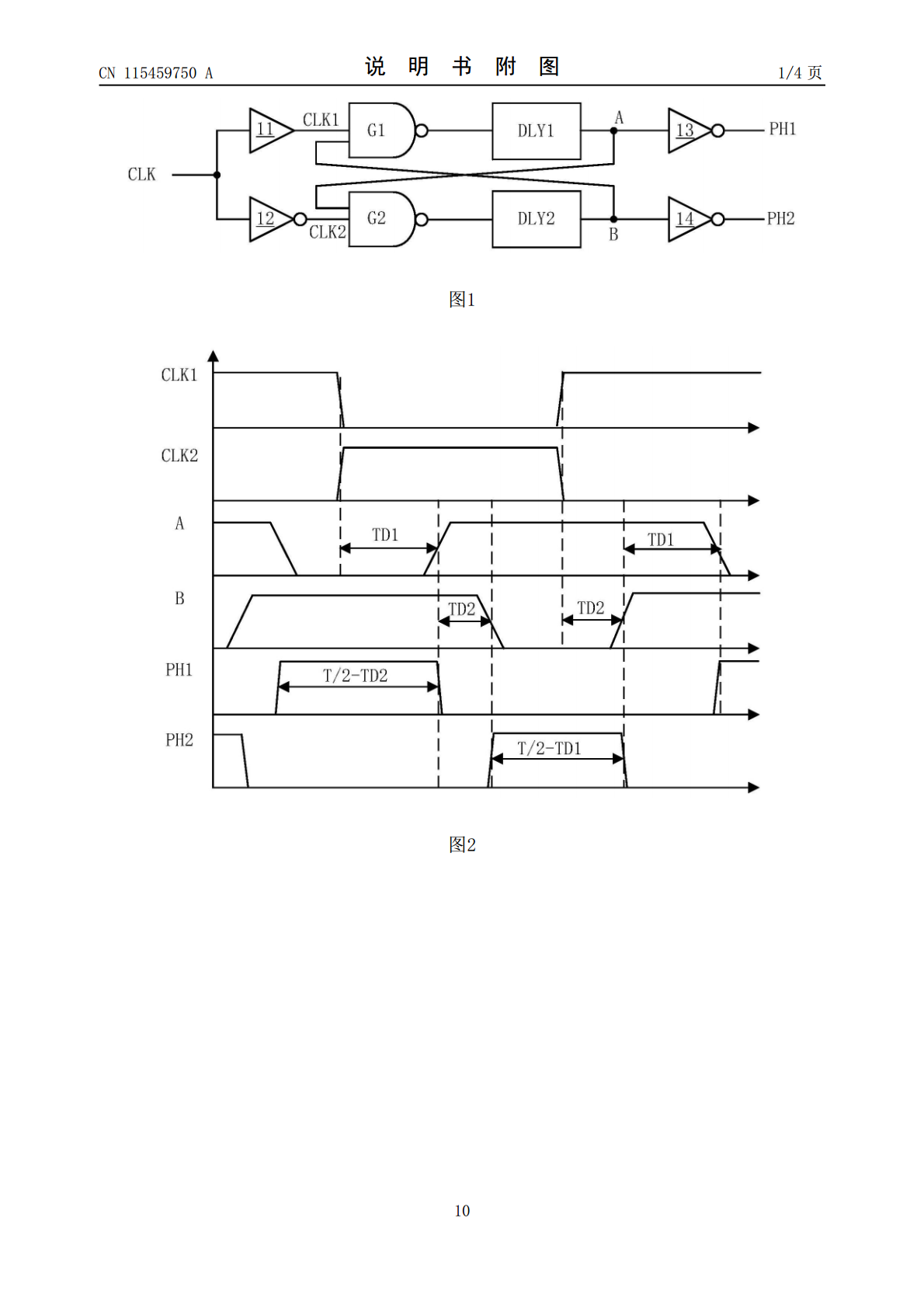

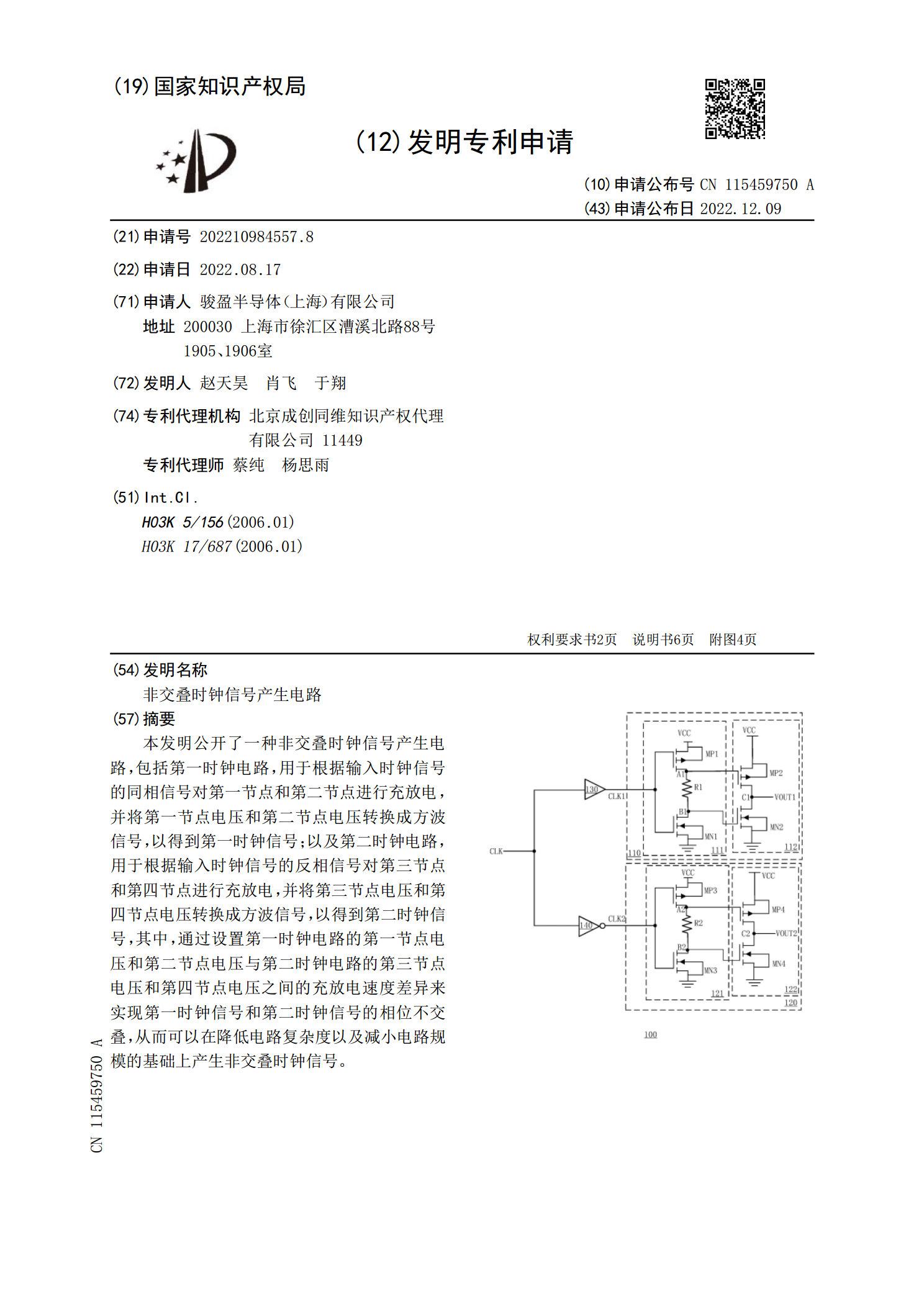

本发明公开了一种非交叠时钟信号产生电路,包括第一时钟电路,用于根据输入时钟信号的同相信号对第一节点和第二节点进行充放电,并将第一节点电压和第二节点电压转换成方波信号,以得到第一时钟信号;以及第二时钟电路,用于根据输入时钟信号的反相信号对第三节点和第四节点进行充放电,并将第三节点电压和第四节点电压转换成方波信号,以得到第二时钟信号,其中,通过设置第一时钟电路的第一节点电压和第二节点电压与第二时钟电路的第三节点电压和第四节点电压之间的充放电速度差异来实现第一时钟信号和第二时钟信号的相位不交叠,从而可以在降低电

两相非交叠时钟产生电路.pdf

本发明提供了一种两相非交叠时钟产生电路,所述电路包括:用于输入时钟信号的信号输入端,连接输入端以用于调制所述时钟信号以获取第一局部信号的第一时钟电路,连接输入端以用于调制所述时钟信号以获取第二局部信号的第二时钟电路,连接第一时钟电路用于输出第一局部信号的第一输出端,连接第二时钟电路用于输出第二局部信号的第二输出端。本发明叠加线路较少,且一个时钟信号仅经过两次分歧、一次变化之后就输出四个子时钟信号,且四个子时钟信号的输出时延各有不同,在用于控制电路开关的通断方面,能够使节点在同一时刻不受两个电压源的驱动,并

时钟信号产生电路、时钟信号产生方法及电子设备.pdf

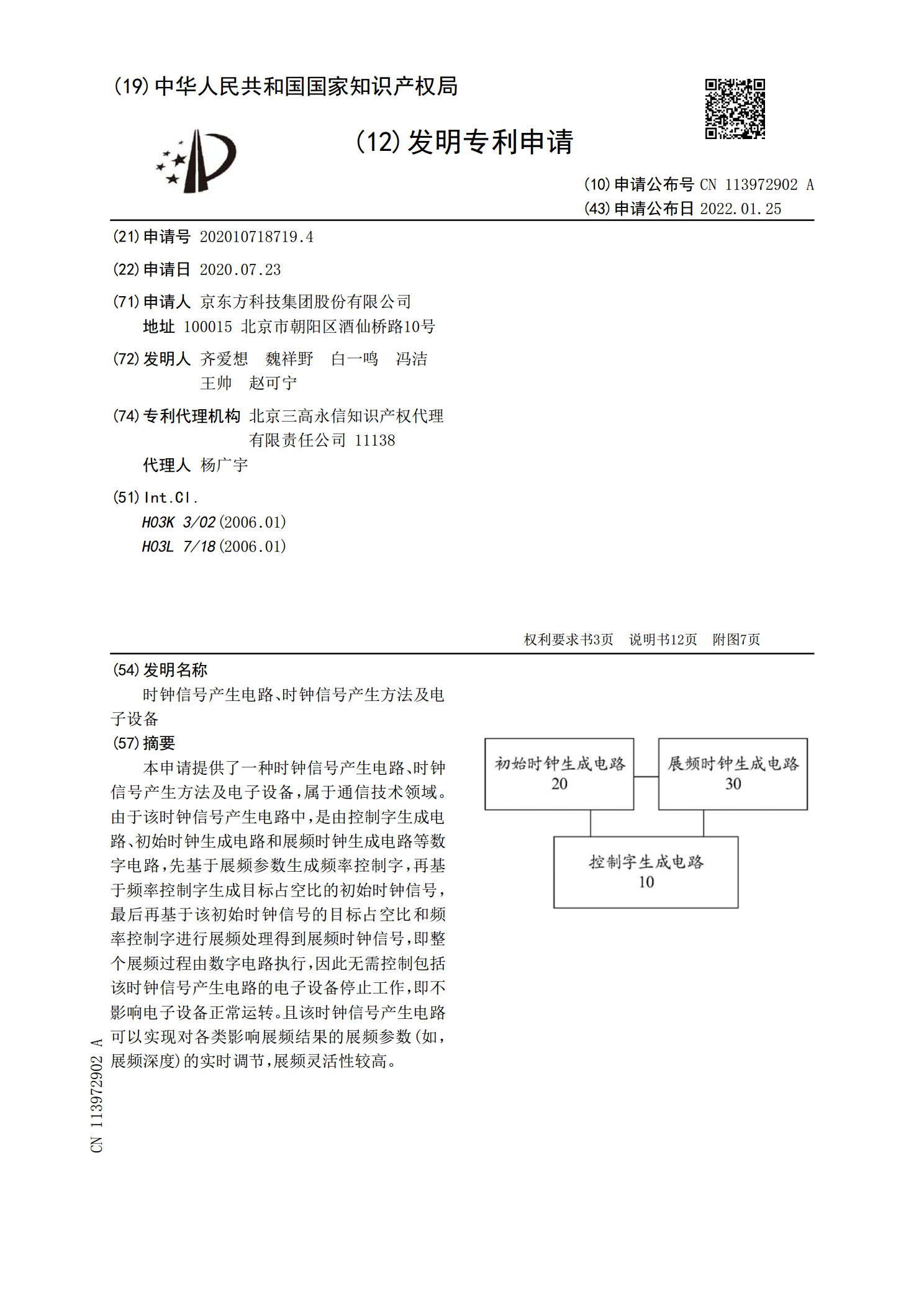

本申请提供了一种时钟信号产生电路、时钟信号产生方法及电子设备,属于通信技术领域。由于该时钟信号产生电路中,是由控制字生成电路、初始时钟生成电路和展频时钟生成电路等数字电路,先基于展频参数生成频率控制字,再基于频率控制字生成目标占空比的初始时钟信号,最后再基于该初始时钟信号的目标占空比和频率控制字进行展频处理得到展频时钟信号,即整个展频过程由数字电路执行,因此无需控制包括该时钟信号产生电路的电子设备停止工作,即不影响电子设备正常运转。且该时钟信号产生电路可以实现对各类影响展频结果的展频参数(如,展频深度)的

用于时钟信号产生的集成电路、方法及系统.pdf

本申请案涉及一种用于时钟信号产生的集成电路、方法及系统。本说明书描述一种集成电路,所述集成电路包括:单线接口;时钟电路,其经配置以检测来自所述单线接口的电压且产生具有基于所述所检测电压的频率的时钟信号;及数字系统,其与所述单线接口及所述时钟电路耦合。所述数字系统经配置以:从所述单线接口接收数据信号;使用来自所述单线接口的电力信号给所述数字系统供电;且执行由所述时钟信号时控的一或多个操作。

一种基于非交叠时钟电荷转移技术的积分电路.pdf

本发明公开了基于非交叠时钟电荷转移技术的积分电路,左边为开关电容积分器,其作用是在非交叠时钟控制信号s1,s2的控制下,对点Vramp进行充放电,右边为非交叠时钟产生电路,其作用是产生非交叠时钟控制信号s1,s2。比较传统积分器而言,本发明具有响应快速,精确度高的优点,可以应用于对积分器响应和精度要求较高的场合。另一方面,本发明所述放大器A2结构,采用带米勒补偿的两级放大器,通过引入负的零来增加相位裕度。在500KHz传感器输出频率下,典型直流增益约为80dB,GBW为25MHz,最大输出电流吸收能力为2