集成电路结构.pdf

曦晨****22

亲,该文档总共22页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

集成电路结构及制造集成电路结构的方法.pdf

本发明实施例提供了一种集成电路(IC)结构。IC结构包括半导体衬底;形成在半导体衬底上的互连结构;以及形成在互连结构上的再分布层(RDL)金属部件。RDL金属部件还包括设置在互连结构上的阻挡层;设置在阻挡层上的扩散层,其中,扩散层包括金属和氧;以及设置在扩散层上的金属层。本发明实施例还提供另一种集成电路结构和一种制造集成电路结构的方法。

集成电路结构.pdf

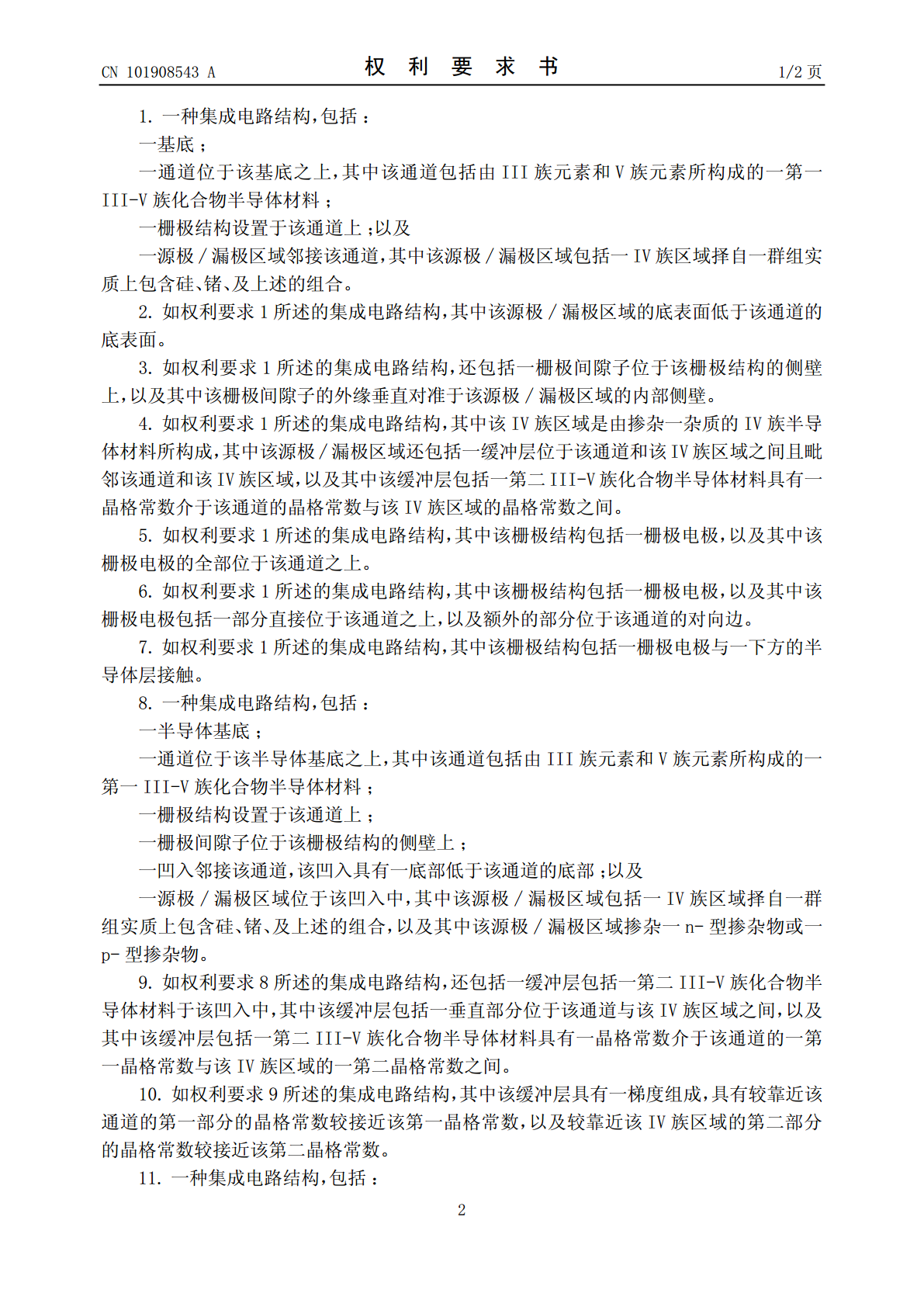

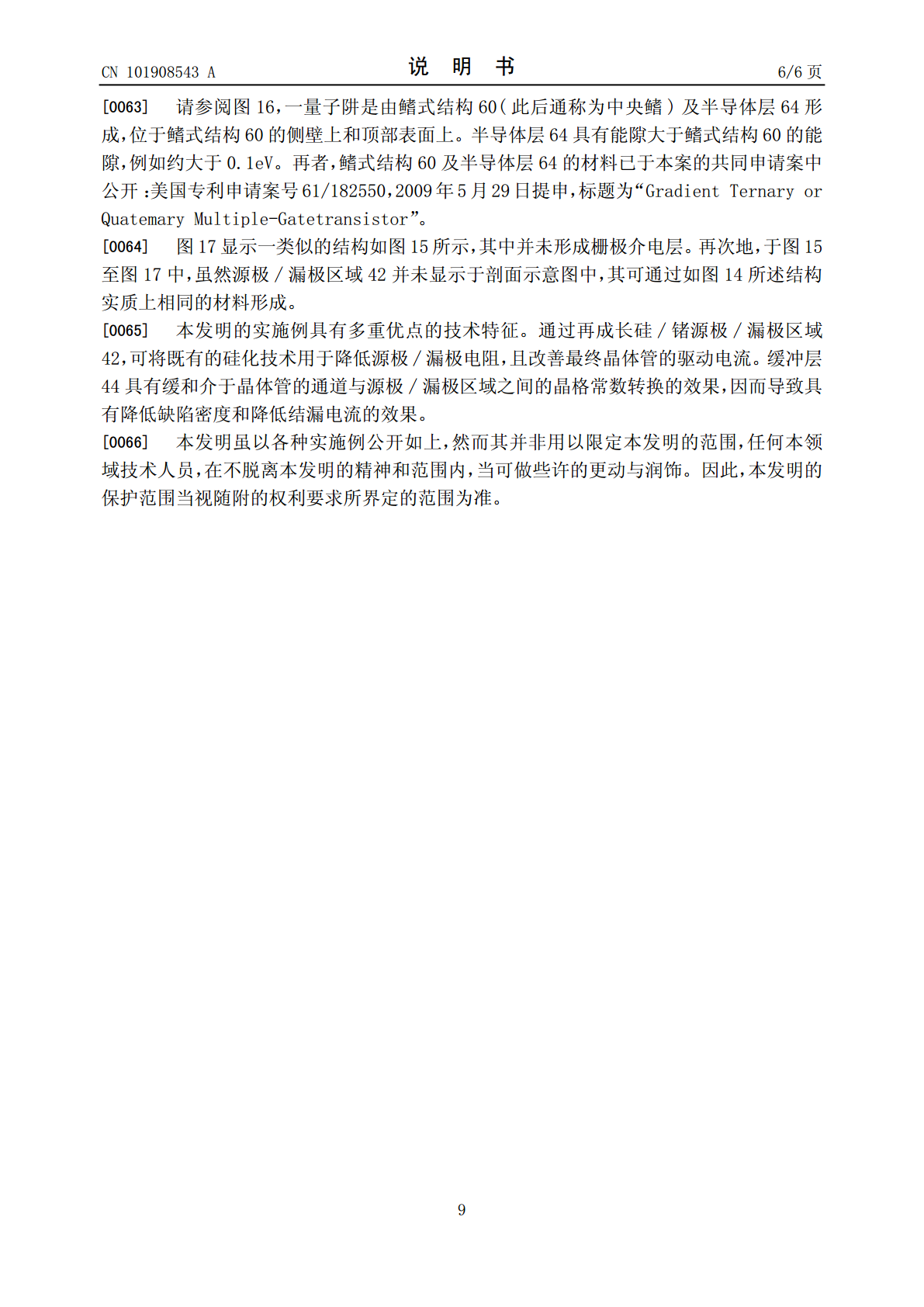

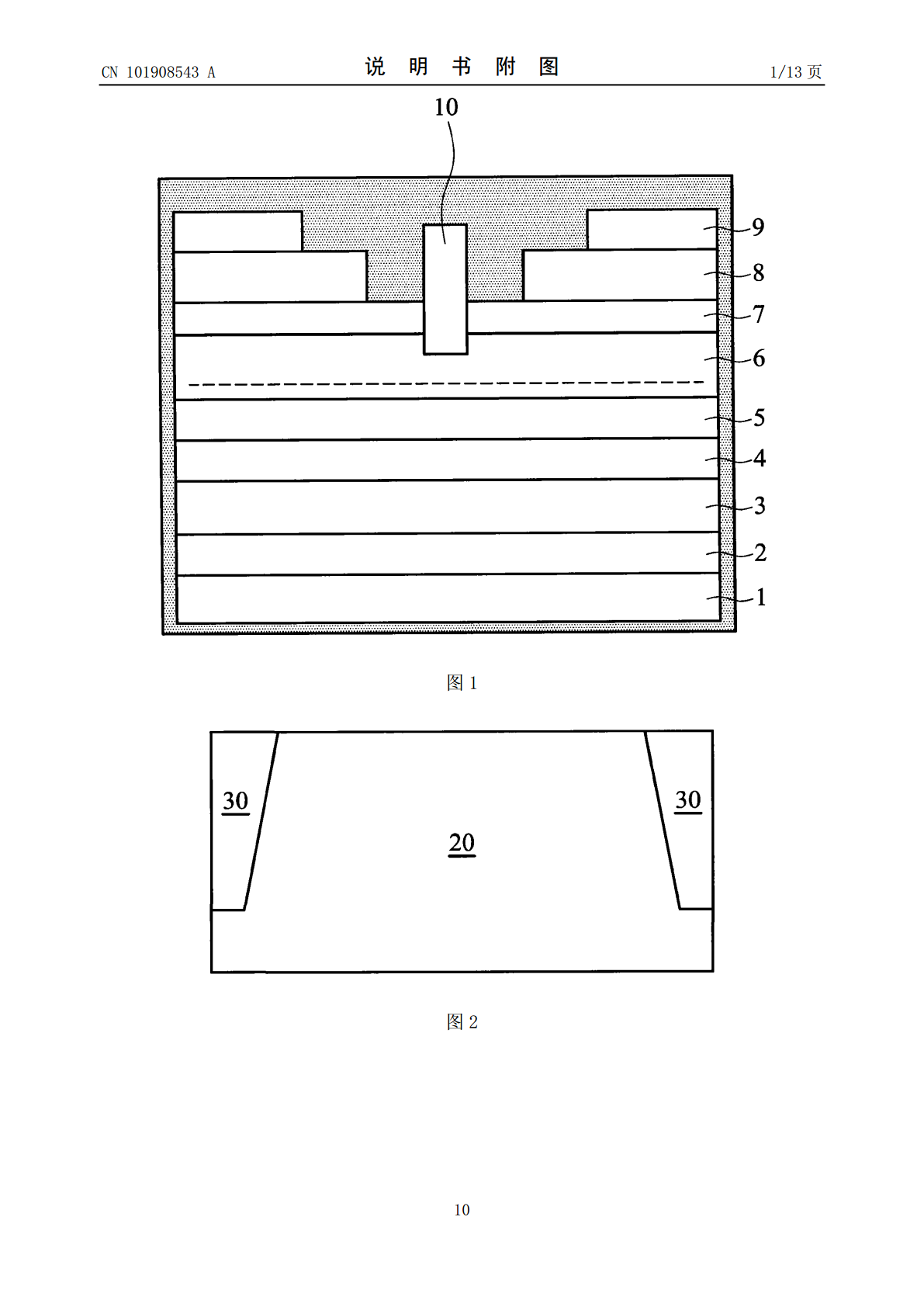

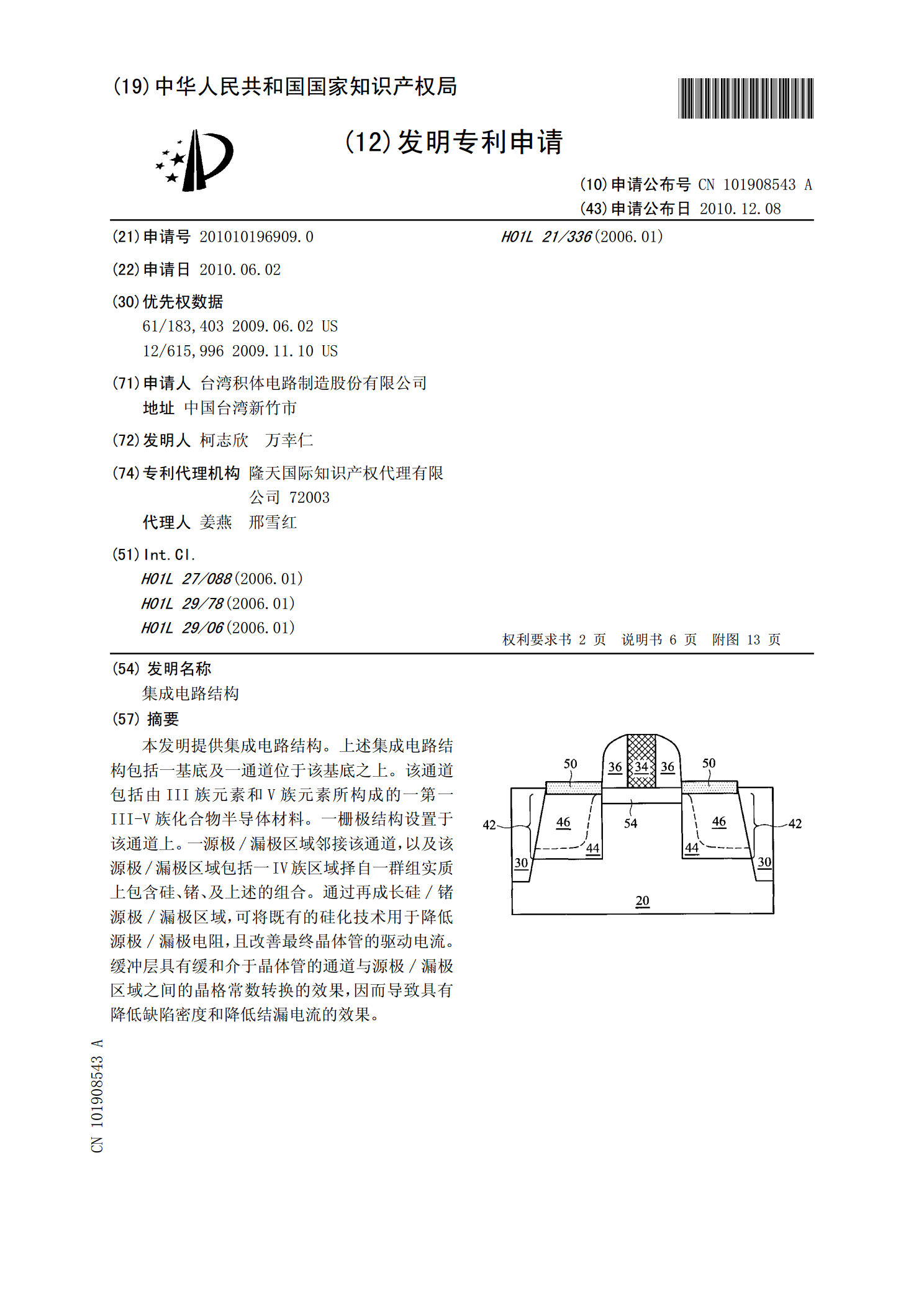

本发明提供集成电路结构。上述集成电路结构包括一基底及一通道位于该基底之上。该通道包括由III族元素和V族元素所构成的一第一III-V族化合物半导体材料。一栅极结构设置于该通道上。一源极/漏极区域邻接该通道,以及该源极/漏极区域包括一IV族区域择自一群组实质上包含硅、锗、及上述的组合。通过再成长硅/锗源极/漏极区域,可将既有的硅化技术用于降低源极/漏极电阻,且改善最终晶体管的驱动电流。缓冲层具有缓和介于晶体管的通道与源极/漏极区域之间的晶格常数转换的效果,因而导致具有降低缺陷密度和降低结漏电流的效果。

集成电路结构.pdf

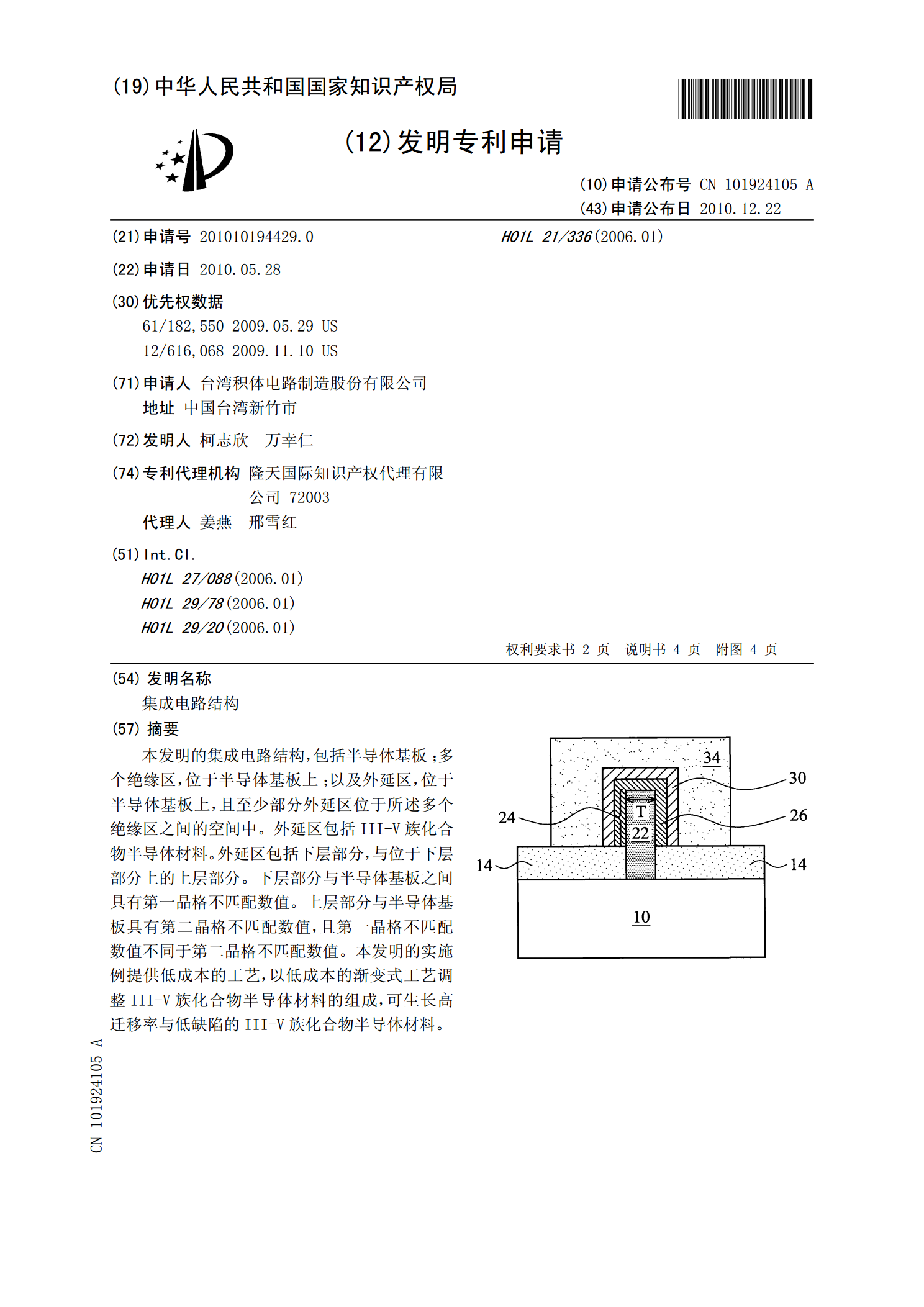

本发明的集成电路结构,包括半导体基板;多个绝缘区,位于半导体基板上;以及外延区,位于半导体基板上,且至少部分外延区位于所述多个绝缘区之间的空间中。外延区包括III-V族化合物半导体材料。外延区包括下层部分,与位于下层部分上的上层部分。下层部分与半导体基板之间具有第一晶格不匹配数值。上层部分与半导体基板具有第二晶格不匹配数值,且第一晶格不匹配数值不同于第二晶格不匹配数值。本发明的实施例提供低成本的工艺,以低成本的渐变式工艺调整III-V族化合物半导体材料的组成,可生长高迁移率与低缺陷的III-V族化合物半导

集成电路结构.pdf

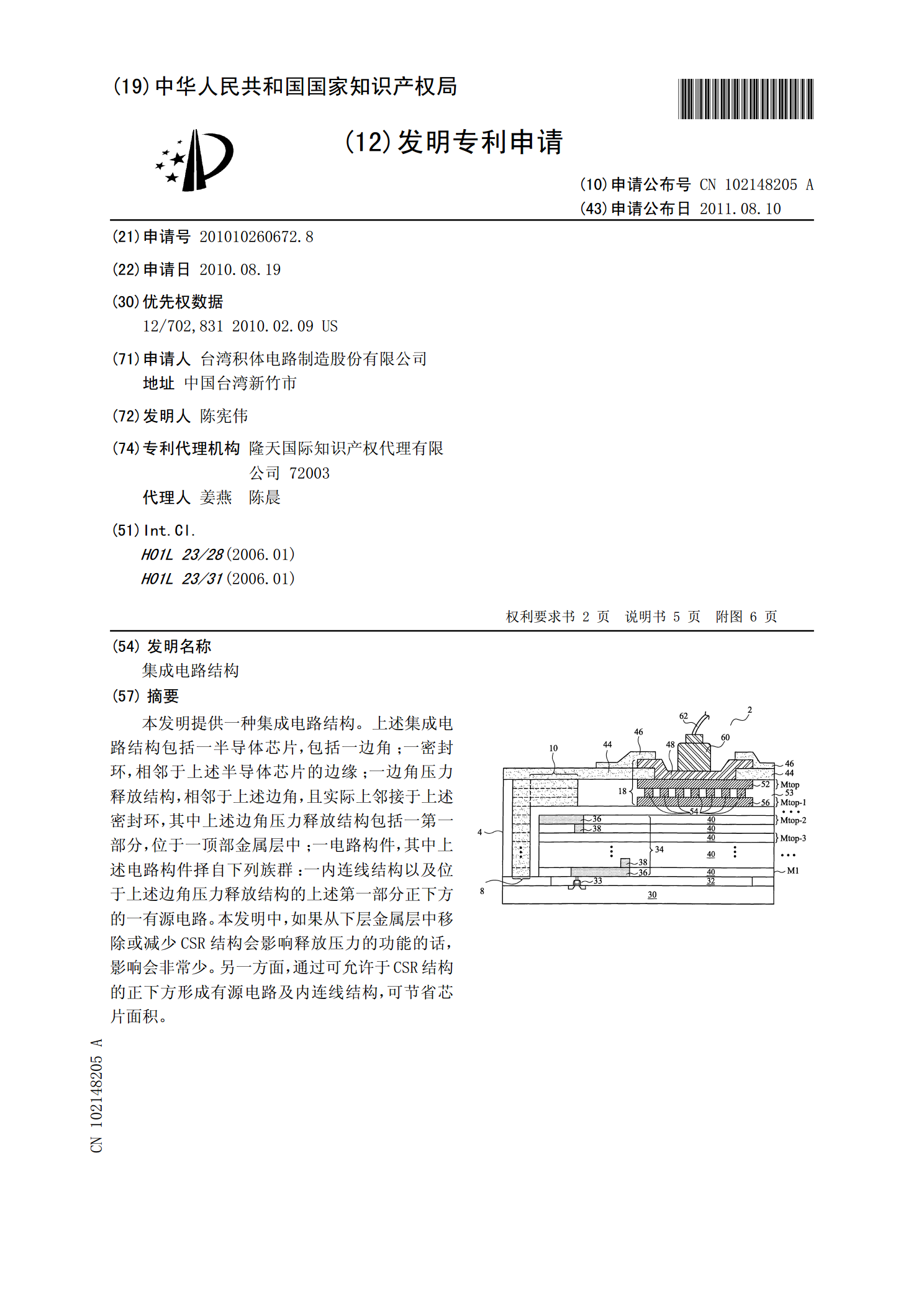

本发明提供一种集成电路结构。上述集成电路结构包括一半导体芯片,包括一边角;一密封环,相邻于上述半导体芯片的边缘;一边角压力释放结构,相邻于上述边角,且实际上邻接于上述密封环,其中上述边角压力释放结构包括一第一部分,位于一顶部金属层中;一电路构件,其中上述电路构件择自下列族群:一内连线结构以及位于上述边角压力释放结构的上述第一部分正下方的一有源电路。本发明中,如果从下层金属层中移除或减少CSR结构会影响释放压力的功能的话,影响会非常少。另一方面,通过可允许于CSR结构的正下方形成有源电路及内连线结构,可节省

集成电路结构.pdf

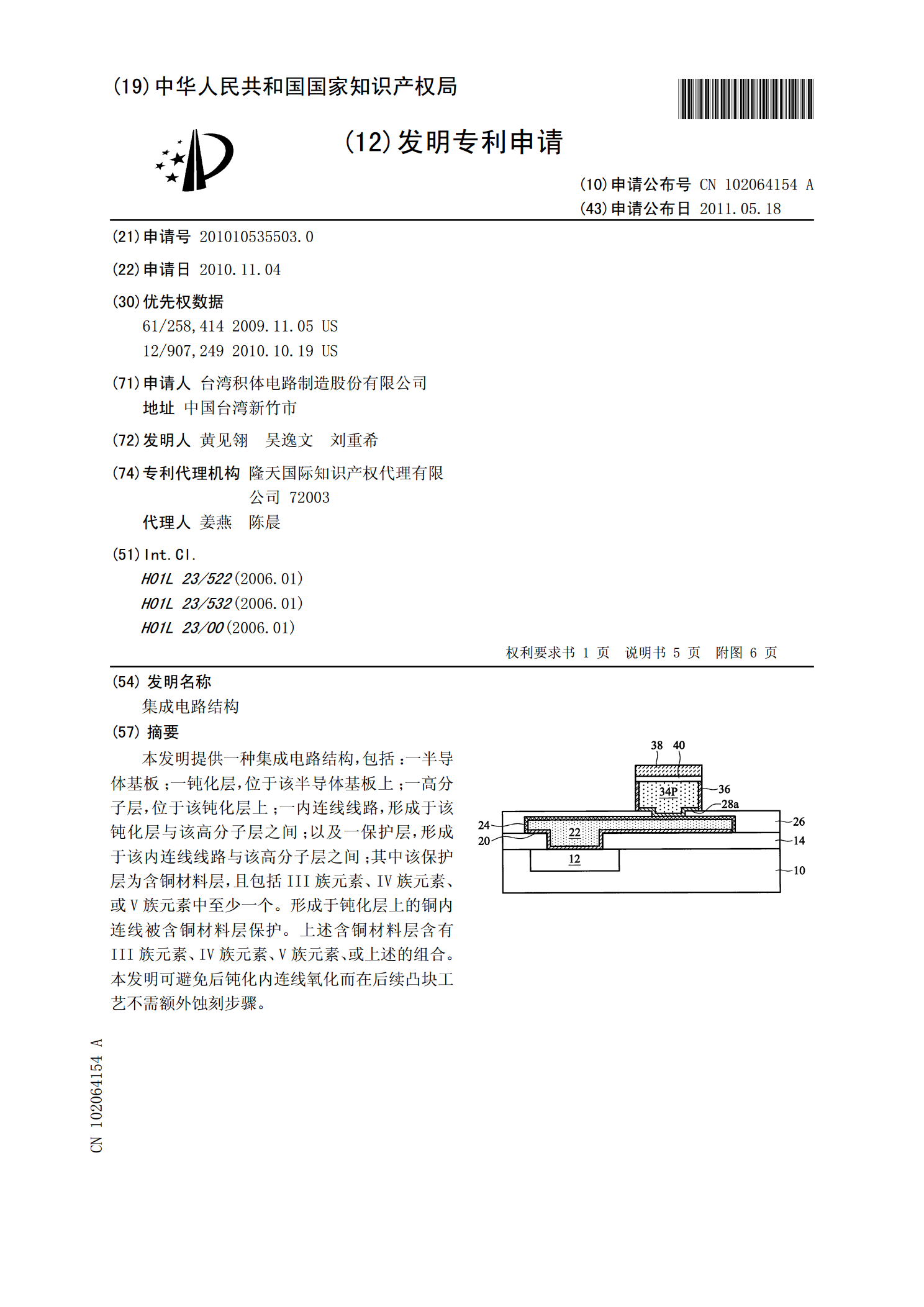

本发明提供一种集成电路结构,包括:一半导体基板;一钝化层,位于该半导体基板上;一高分子层,位于该钝化层上;一内连线线路,形成于该钝化层与该高分子层之间;以及一保护层,形成于该内连线线路与该高分子层之间;其中该保护层为含铜材料层,且包括III族元素、IV族元素、或V族元素中至少一个。形成于钝化层上的铜内连线被含铜材料层保护。上述含铜材料层含有III族元素、IV族元素、V族元素、或上述的组合。本发明可避免后钝化内连线氧化而在后续凸块工艺不需额外蚀刻步骤。