一种具有高k介质的屏蔽栅沟槽型MOSFET结构.pdf

是雁****找我

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种具有高k介质的屏蔽栅沟槽型MOSFET结构.pdf

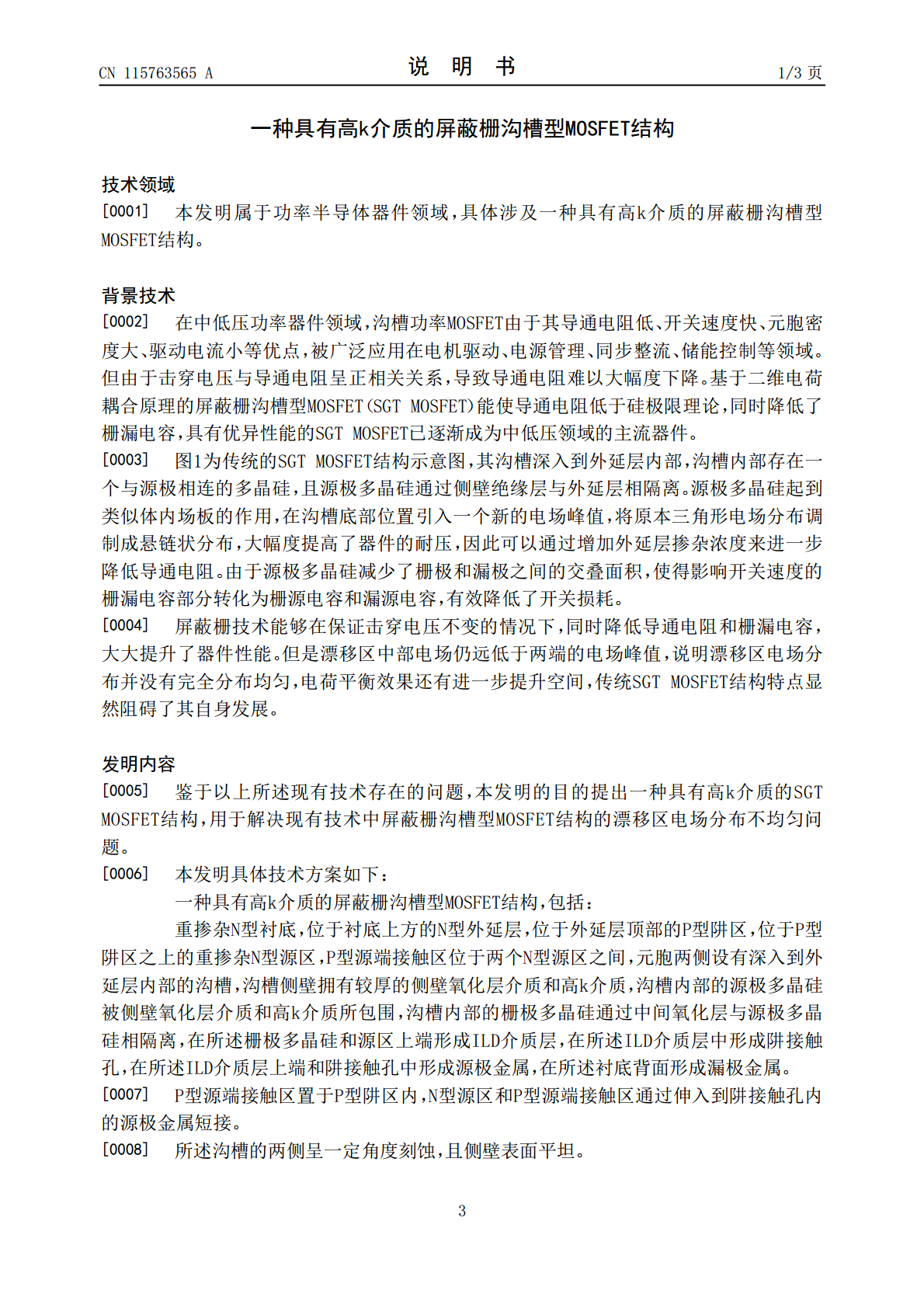

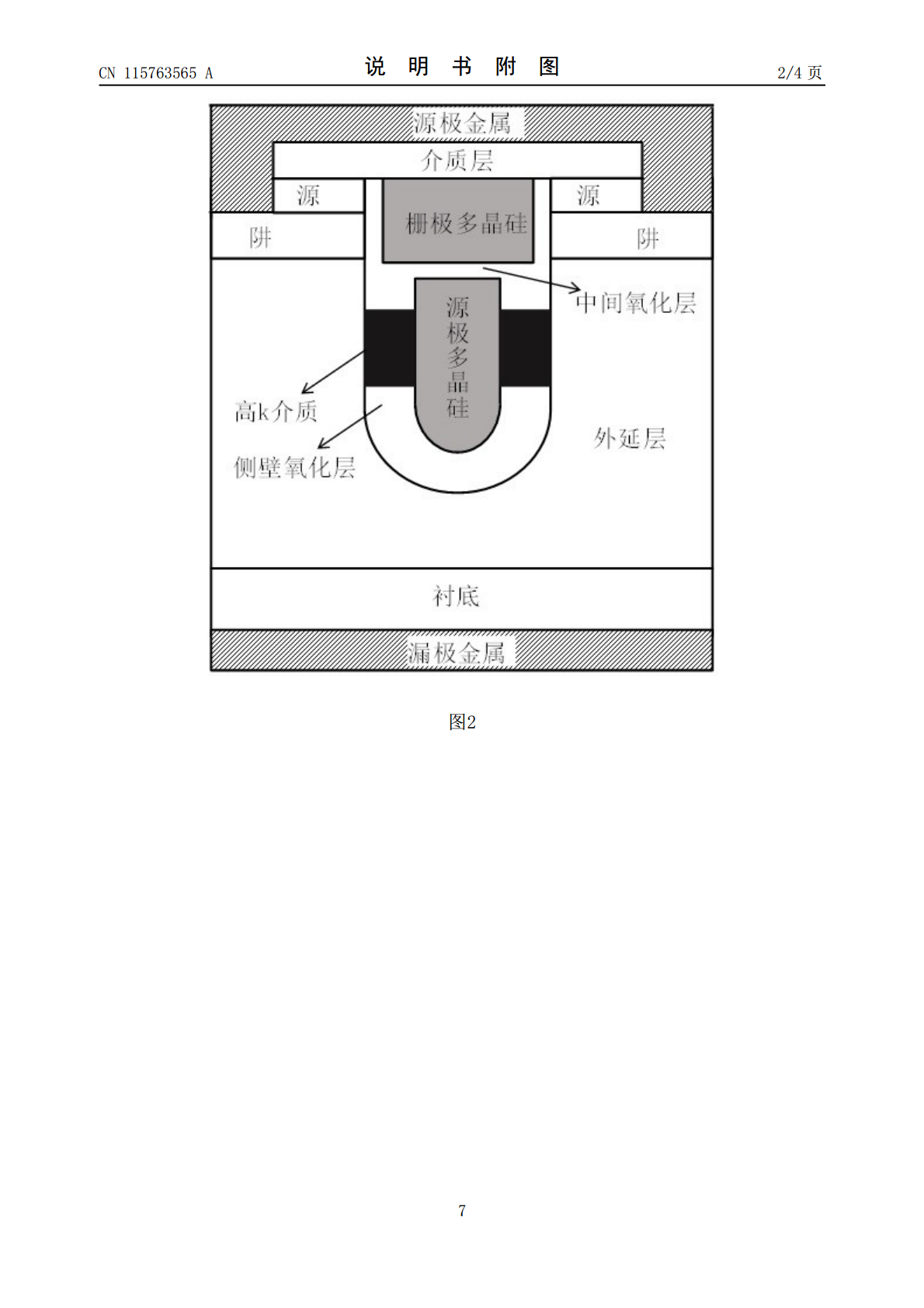

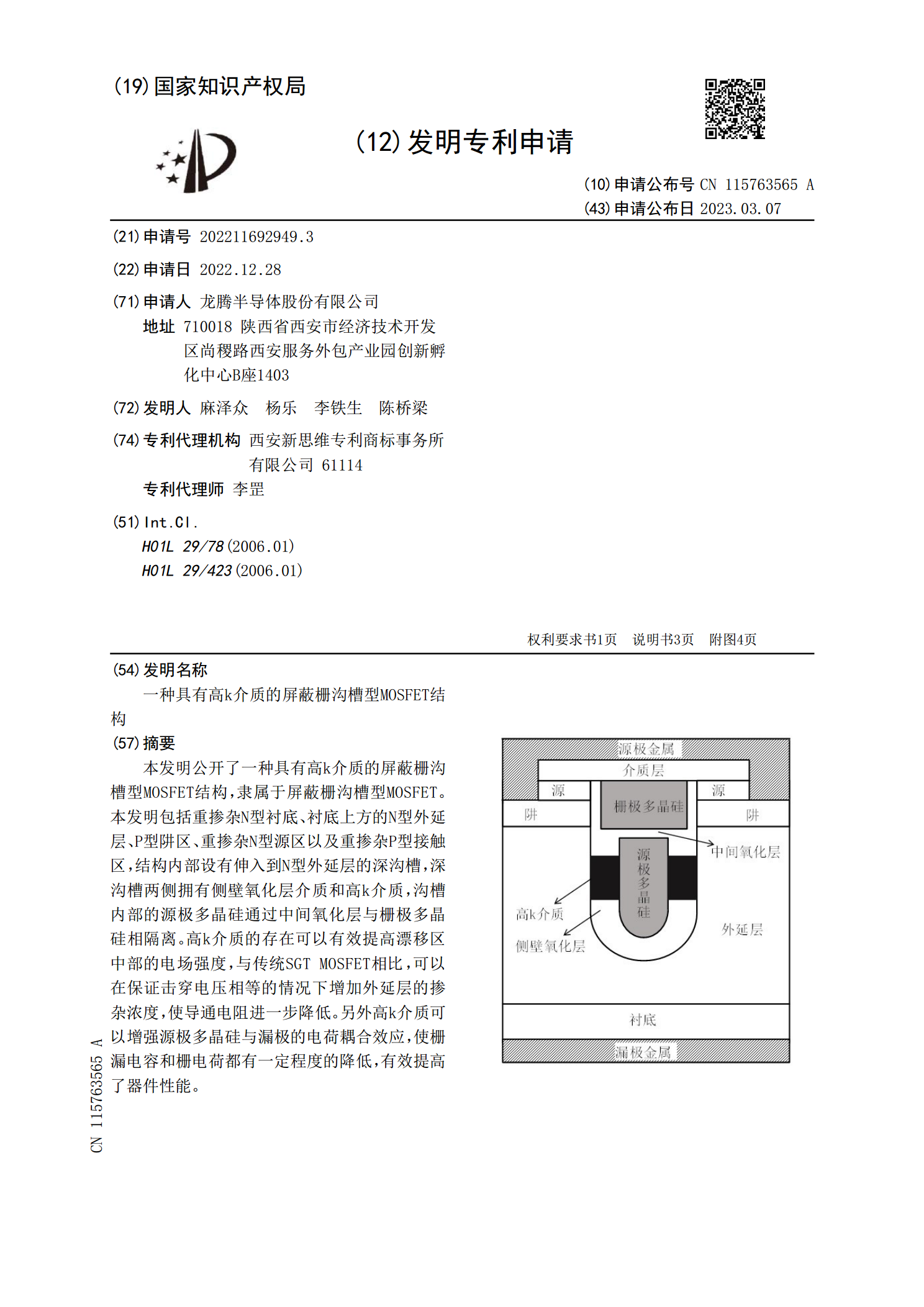

本发明公开了一种具有高k介质的屏蔽栅沟槽型MOSFET结构,隶属于屏蔽栅沟槽型MOSFET。本发明包括重掺杂N型衬底、衬底上方的N型外延层、P型阱区、重掺杂N型源区以及重掺杂P型接触区,结构内部设有伸入到N型外延层的深沟槽,深沟槽两侧拥有侧壁氧化层介质和高k介质,沟槽内部的源极多晶硅通过中间氧化层与栅极多晶硅相隔离。高k介质的存在可以有效提高漂移区中部的电场强度,与传统SGTMOSFET相比,可以在保证击穿电压相等的情况下增加外延层的掺杂浓度,使导通电阻进一步降低。另外高k介质可以增强源极多晶硅与漏极的

屏蔽栅沟槽型MOSFET的制造方法.pdf

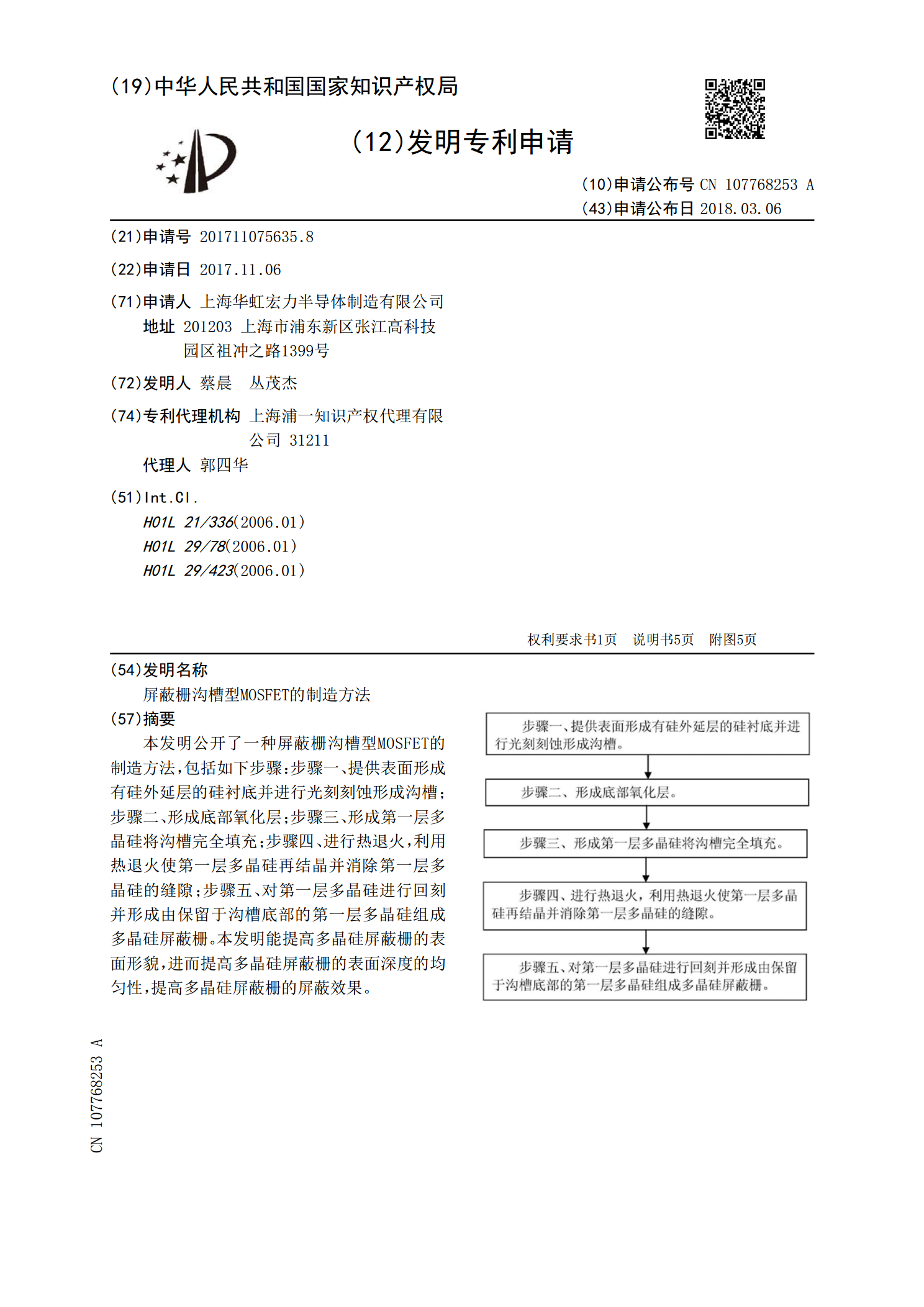

本发明公开了一种屏蔽栅沟槽型MOSFET的制造方法,包括如下步骤:步骤一、提供表面形成有硅外延层的硅衬底并进行光刻刻蚀形成沟槽;步骤二、形成底部氧化层;步骤三、形成第一层多晶硅将沟槽完全填充;步骤四、进行热退火,利用热退火使第一层多晶硅再结晶并消除第一层多晶硅的缝隙;步骤五、对第一层多晶硅进行回刻并形成由保留于沟槽底部的第一层多晶硅组成多晶硅屏蔽栅。本发明能提高多晶硅屏蔽栅的表面形貌,进而提高多晶硅屏蔽栅的表面深度的均匀性,提高多晶硅屏蔽栅的屏蔽效果。

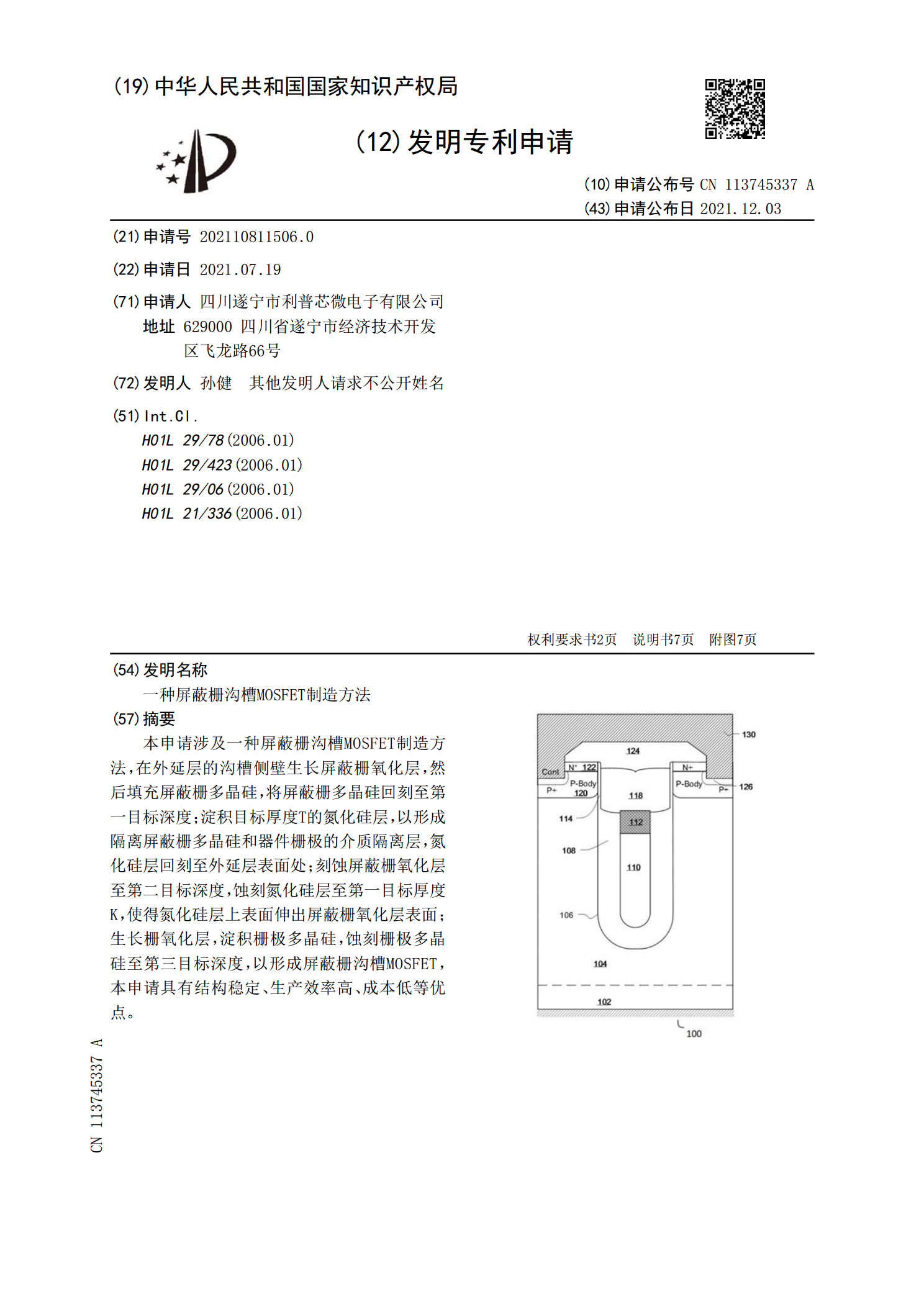

一种屏蔽栅沟槽MOSFET制造方法.pdf

本申请涉及一种屏蔽栅沟槽MOSFET制造方法,在外延层的沟槽侧壁生长屏蔽栅氧化层,然后填充屏蔽栅多晶硅,将屏蔽栅多晶硅回刻至第一目标深度;淀积目标厚度T的氮化硅层,以形成隔离屏蔽栅多晶硅和器件栅极的介质隔离层,氮化硅层回刻至外延层表面处;刻蚀屏蔽栅氧化层至第二目标深度,蚀刻氮化硅层至第一目标厚度K,使得氮化硅层上表面伸出屏蔽栅氧化层表面;生长栅氧化层,淀积栅极多晶硅,蚀刻栅极多晶硅至第三目标深度,以形成屏蔽栅沟槽MOSFET,本申请具有结构稳定、生产效率高、成本低等优点。

一种屏蔽栅沟槽MOSFET及其制造方法.pdf

本申请公开了一种屏蔽栅沟槽MOSFET及其制造方法,属于集成电路领域。该屏蔽栅沟槽MOSFET主要包括:衬底片;外延层,其生长在衬底片上;硬掩膜,其通过在外延层上淀积氧化硅形成,并在形成深沟槽后移除;深沟槽,其利用沟槽掩膜版在硬掩膜上刻蚀外延层得到;场介质层,其生长在深沟槽的表面且与述源极多晶硅的表面平齐;源极多晶硅,其填充在深沟槽内的场介质层上;栅极沟槽,其利用有源区掩膜版在场介质层表面刻蚀场介质层得到;栅极氧化硅,其通过在栅极沟槽表面氧化形成;栅极多晶硅,其在栅极沟槽的栅极氧化硅上淀积。本申请通过在栅

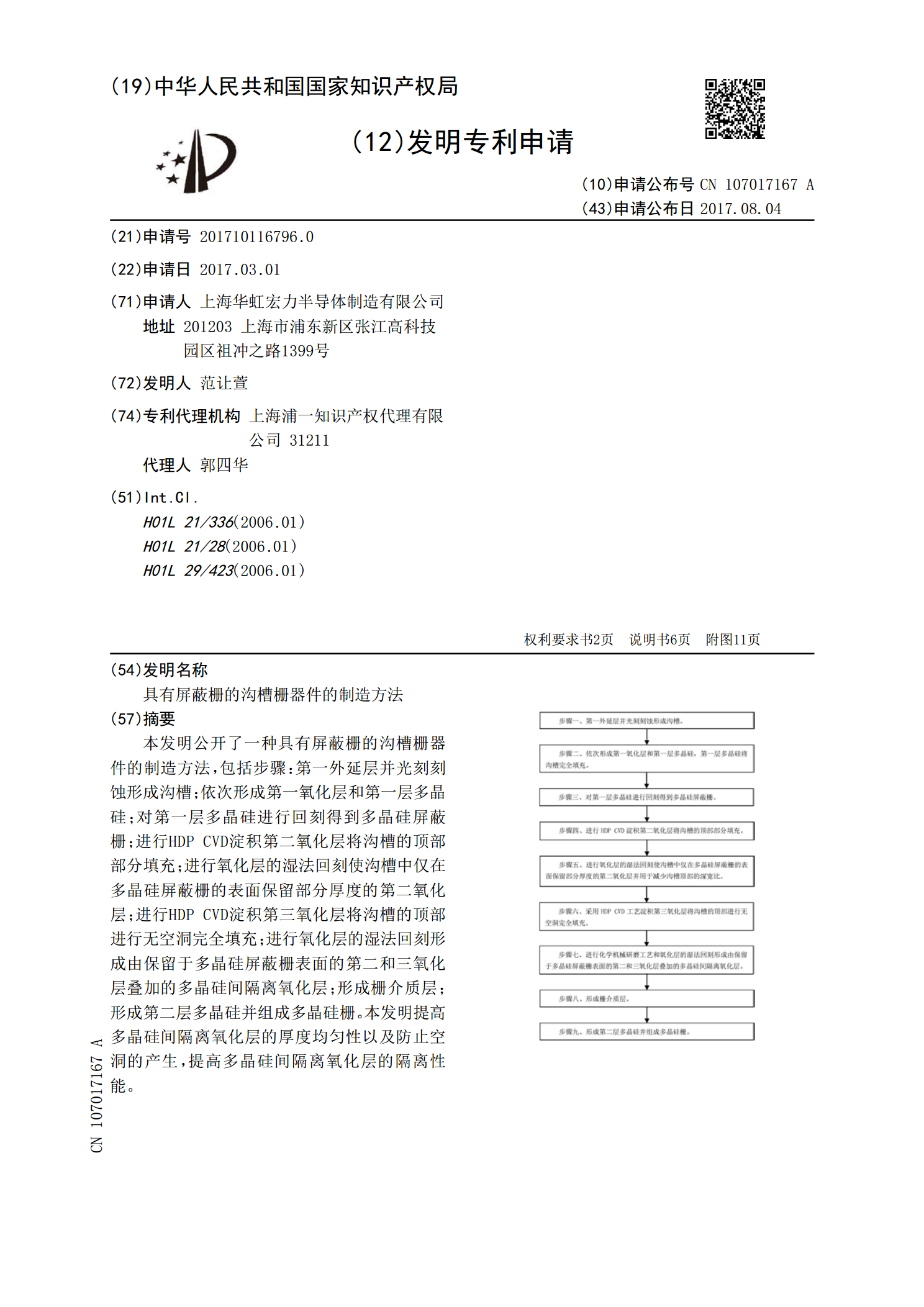

具有屏蔽栅的沟槽栅器件的制造方法.pdf

本发明公开了一种具有屏蔽栅的沟槽栅器件的制造方法,包括步骤:第一外延层并光刻刻蚀形成沟槽;依次形成第一氧化层和第一层多晶硅;对第一层多晶硅进行回刻得到多晶硅屏蔽栅;进行HDPCVD淀积第二氧化层将沟槽的顶部部分填充;进行氧化层的湿法回刻使沟槽中仅在多晶硅屏蔽栅的表面保留部分厚度的第二氧化层;进行HDPCVD淀积第三氧化层将沟槽的顶部进行无空洞完全填充;进行氧化层的湿法回刻形成由保留于多晶硅屏蔽栅表面的第二和三氧化层叠加的多晶硅间隔离氧化层;形成栅介质层;形成第二层多晶硅并组成多晶硅栅。本发明提高多晶硅