芯片插座、测试夹具及其芯片测试方法.pdf

一吃****福乾

亲,该文档总共21页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

芯片插座、测试夹具及其芯片测试方法.pdf

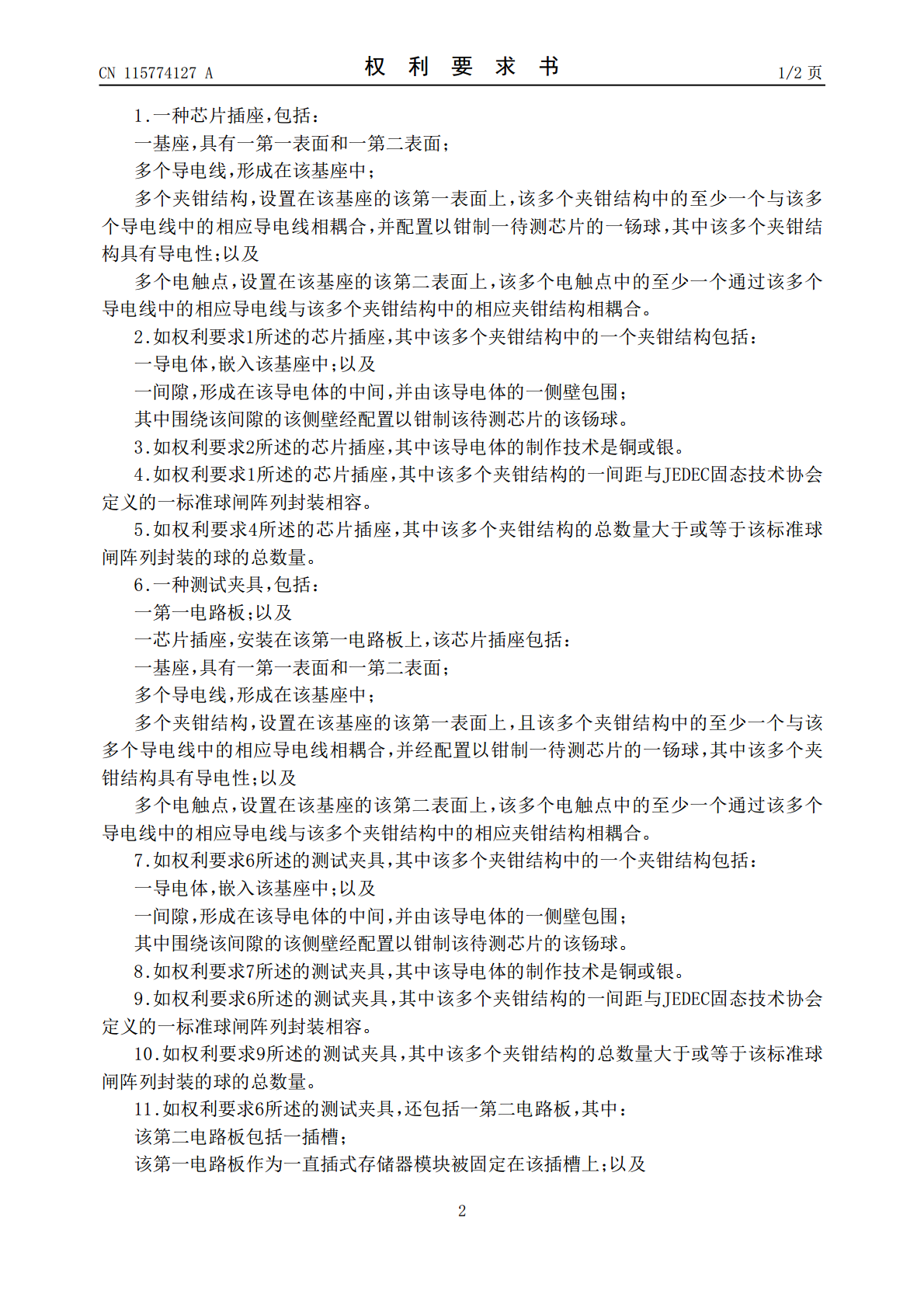

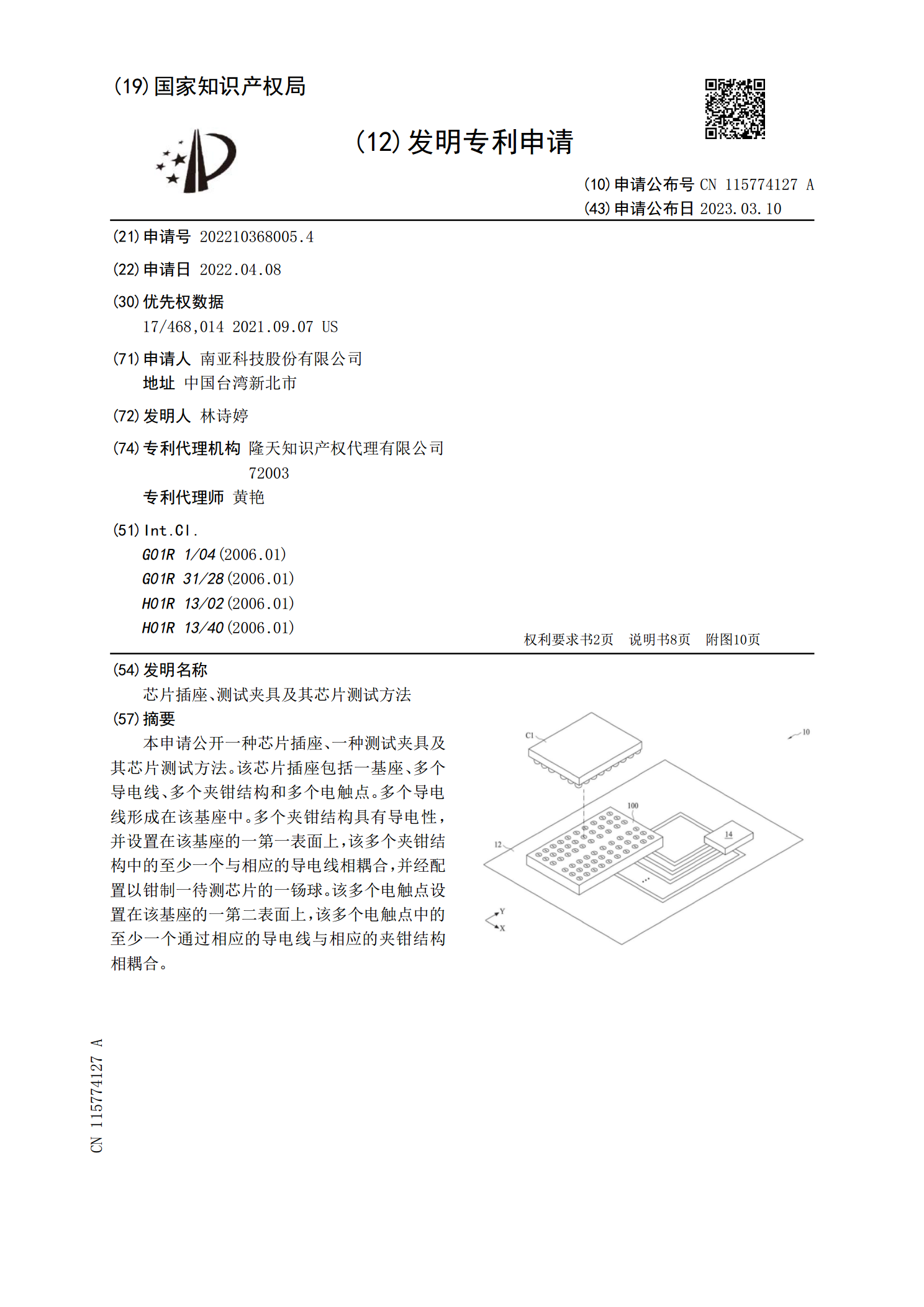

本申请公开一种芯片插座、一种测试夹具及其芯片测试方法。该芯片插座包括一基座、多个导电线、多个夹钳结构和多个电触点。多个导电线形成在该基座中。多个夹钳结构具有导电性,并设置在该基座的一第一表面上,该多个夹钳结构中的至少一个与相应的导电线相耦合,并经配置以钳制一待测芯片的一钖球。该多个电触点设置在该基座的一第二表面上,该多个电触点中的至少一个通过相应的导电线与相应的夹钳结构相耦合。

芯片及其测试方法.pdf

本发明涉及半导体领域,其提供了一种芯片及其测试方法,所述芯片包括光学链路,所述光学链路包括:波导,所述波导包括沿着芯片边缘布置的边缘波导部分,所述边缘波导部分距离所述芯片边缘的距离小于等于500μm,所述边缘波导部分对应的芯片边缘的累计长度为L,L≥4mm;光输入结构,被配置为向所述光学链路输入光;以及光输出结构,被配置为从所述光学链路输出光。

温度测量芯片多工位测试插座.pdf

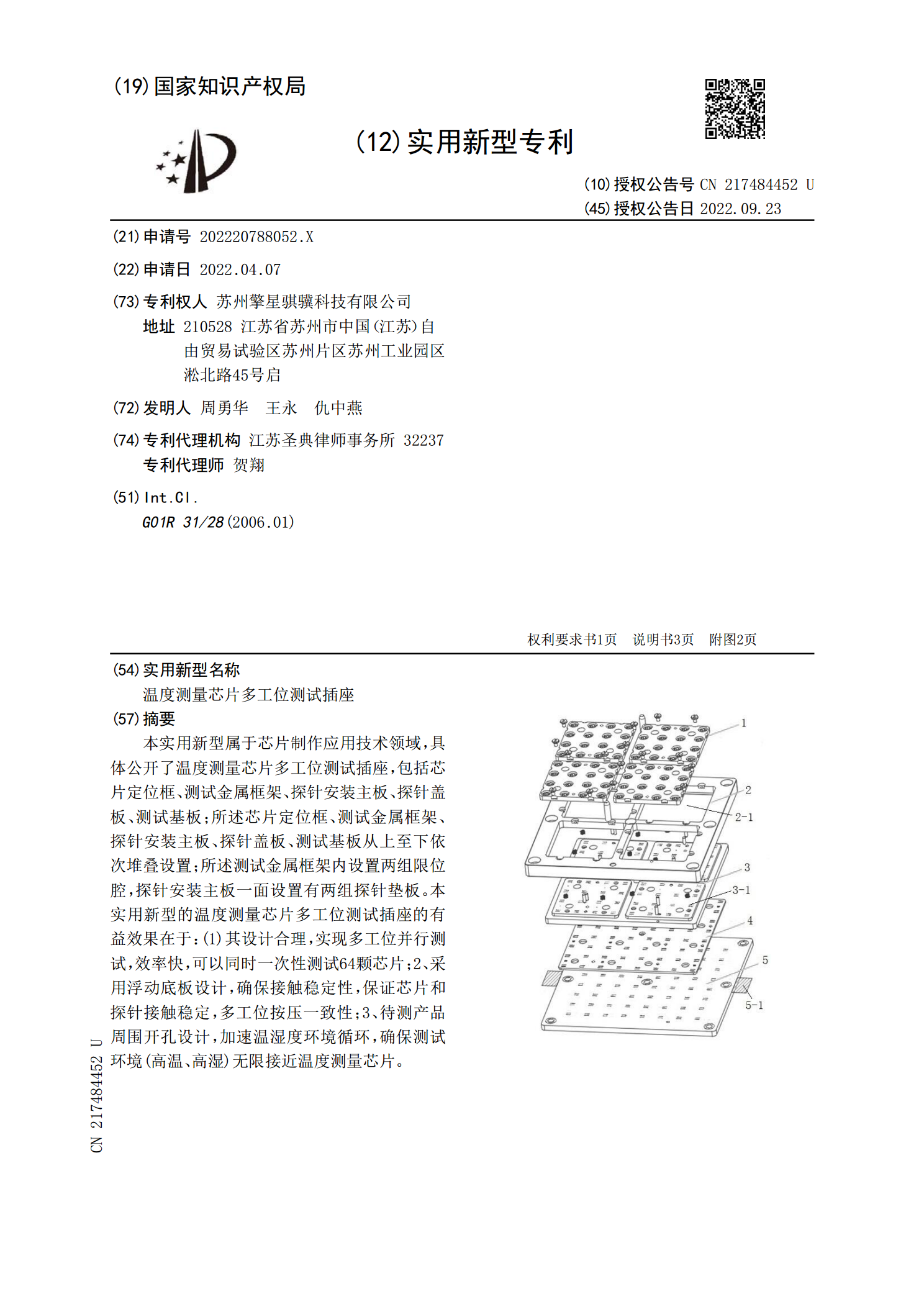

本实用新型属于芯片制作应用技术领域,具体公开了温度测量芯片多工位测试插座,包括芯片定位框、测试金属框架、探针安装主板、探针盖板、测试基板;所述芯片定位框、测试金属框架、探针安装主板、探针盖板、测试基板从上至下依次堆叠设置;所述测试金属框架内设置两组限位腔,探针安装主板一面设置有两组探针垫板。本实用新型的温度测量芯片多工位测试插座的有益效果在于:(1)其设计合理,实现多工位并行测试,效率快,可以同时一次性测试64颗芯片;2、采用浮动底板设计,确保接触稳定性,保证芯片和探针接触稳定,多工位按压一致性;3、待测

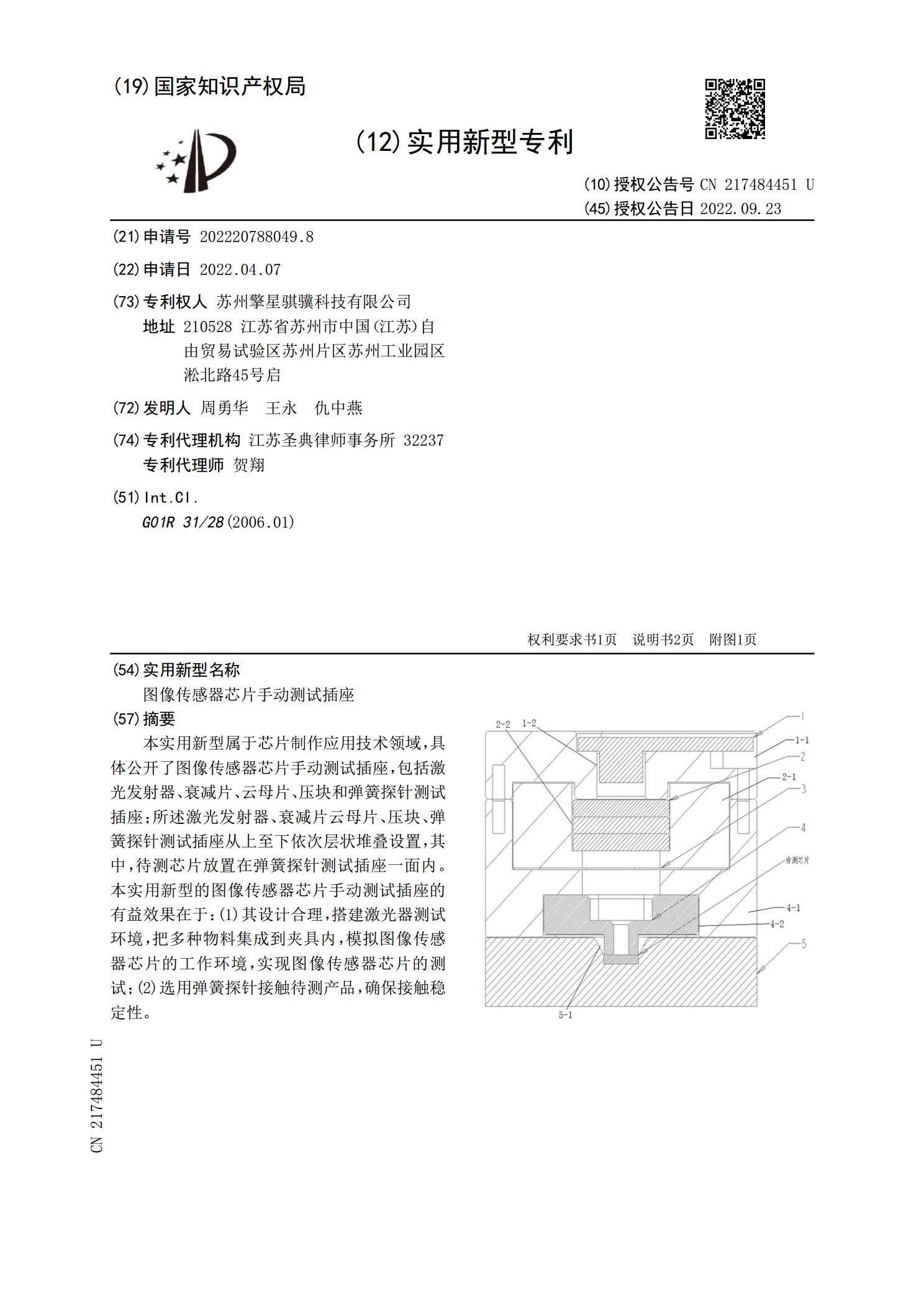

图像传感器芯片手动测试插座.pdf

本实用新型属于芯片制作应用技术领域,具体公开了图像传感器芯片手动测试插座,包括激光发射器、衰减片、云母片、压块和弹簧探针测试插座;所述激光发射器、衰减片云母片、压块、弹簧探针测试插座从上至下依次层状堆叠设置,其中,待测芯片放置在弹簧探针测试插座一面内。本实用新型的图像传感器芯片手动测试插座的有益效果在于:(1)其设计合理,搭建激光器测试环境,把多种物料集成到夹具内,模拟图像传感器芯片的工作环境,实现图像传感器芯片的测试;(2)选用弹簧探针接触待测产品,确保接触稳定性。

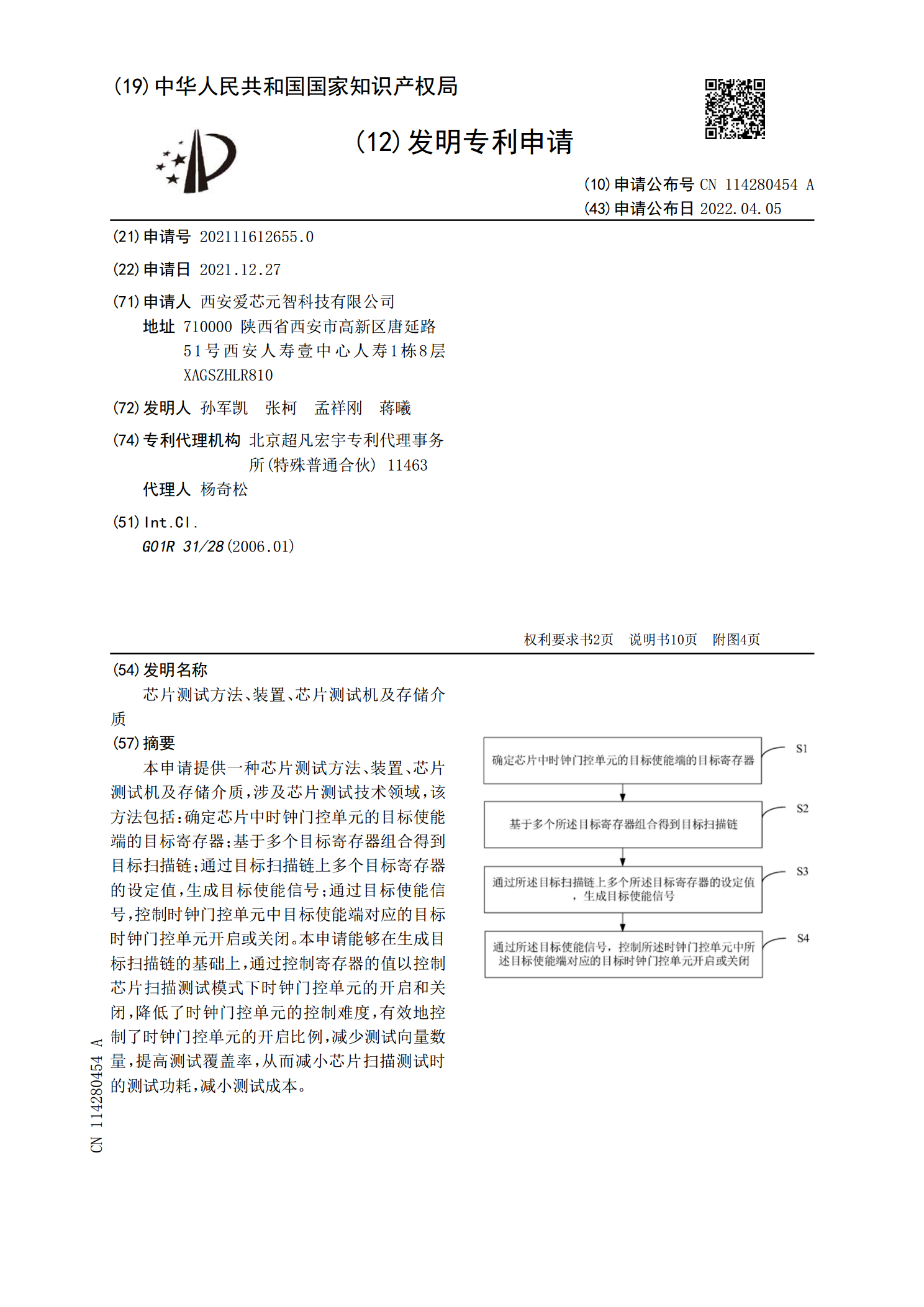

芯片测试方法、装置、芯片测试机及存储介质.pdf

本申请提供一种芯片测试方法、装置、芯片测试机及存储介质,涉及芯片测试技术领域,该方法包括:确定芯片中时钟门控单元的目标使能端的目标寄存器;基于多个目标寄存器组合得到目标扫描链;通过目标扫描链上多个目标寄存器的设定值,生成目标使能信号;通过目标使能信号,控制时钟门控单元中目标使能端对应的目标时钟门控单元开启或关闭。本申请能够在生成目标扫描链的基础上,通过控制寄存器的值以控制芯片扫描测试模式下时钟门控单元的开启和关闭,降低了时钟门控单元的控制难度,有效地控制了时钟门控单元的开启比例,减少测试向量数量,提高测试