非对称SiC沟槽结构及其制作方法、电子器件.pdf

一只****呀盟

亲,该文档总共22页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

非对称SiC沟槽结构及其制作方法、电子器件.pdf

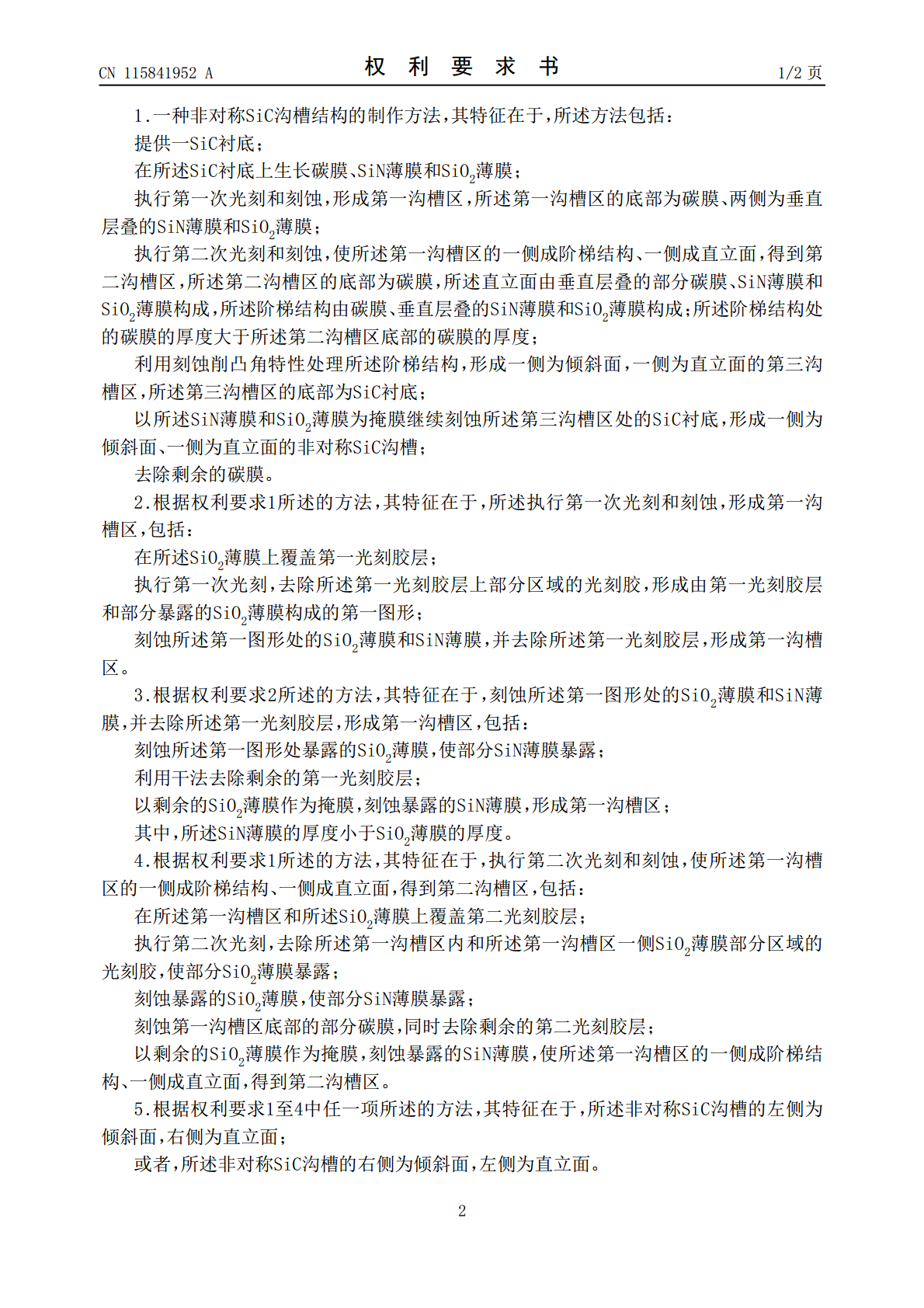

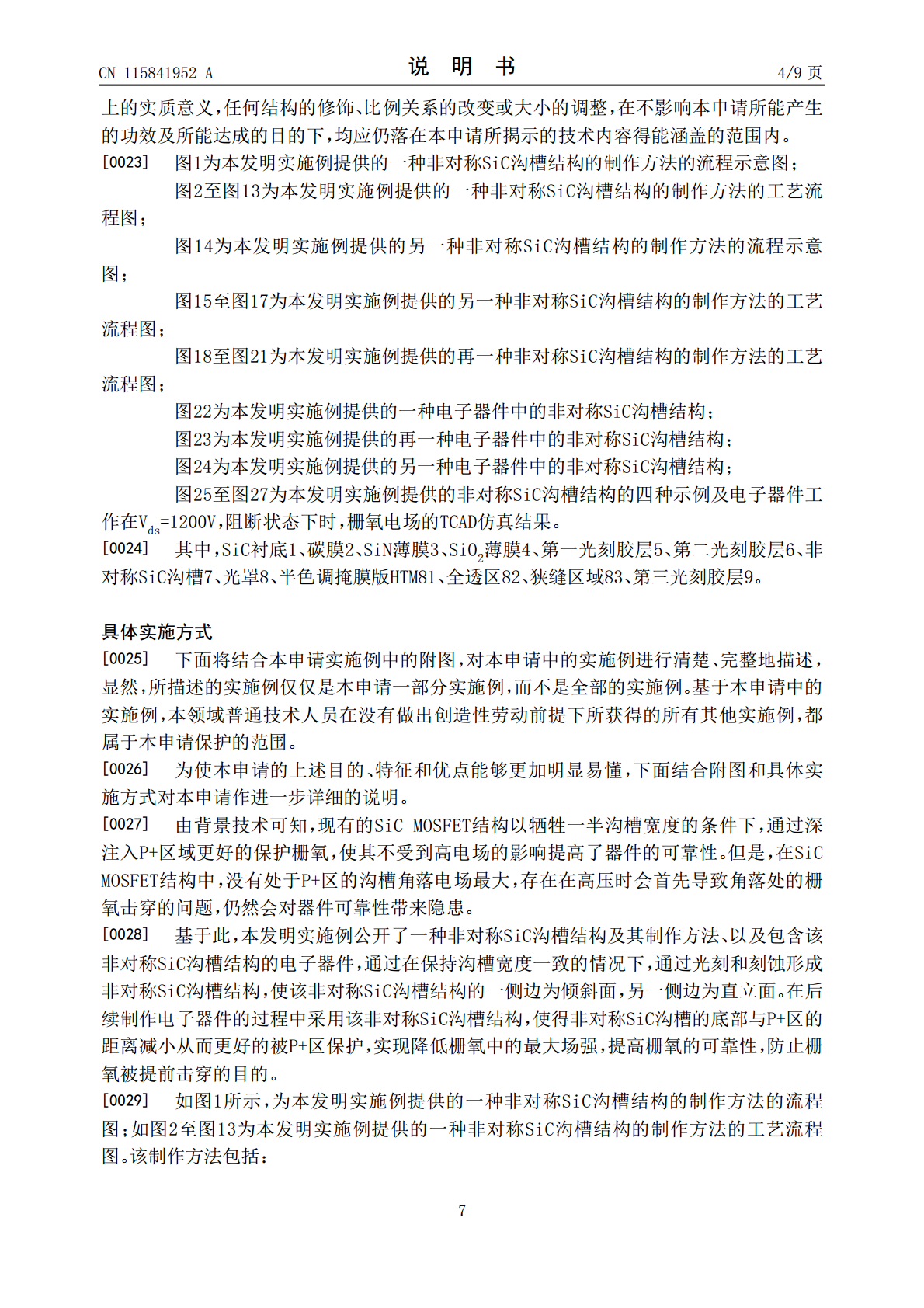

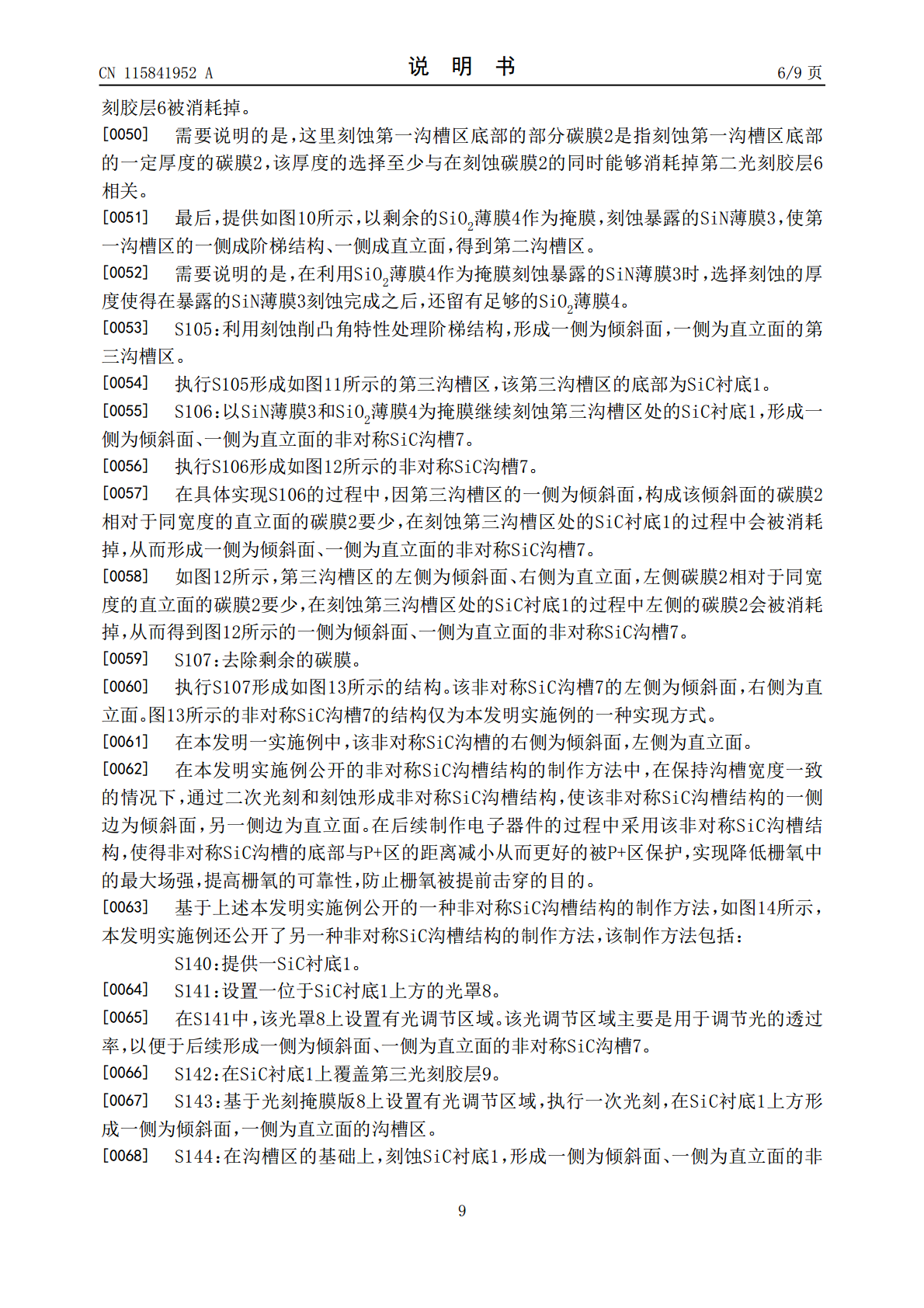

本申请公开了一种非对称SiC沟槽结构及其制作方法、电子器件,通过光刻和刻蚀形成非对称SiC沟槽结构,使该非对称SiC沟槽结构的一侧边为倾斜面,另一侧边为直立面。在后续制作电子器件的过程中采用该非对称SiC沟槽结构,使得非对称SiC沟槽的底部与P+区的距离减小从而更好的被P+区保护,实现降低栅氧中的最大场强,提高栅氧的可靠性,防止栅氧被提前击穿的目的。

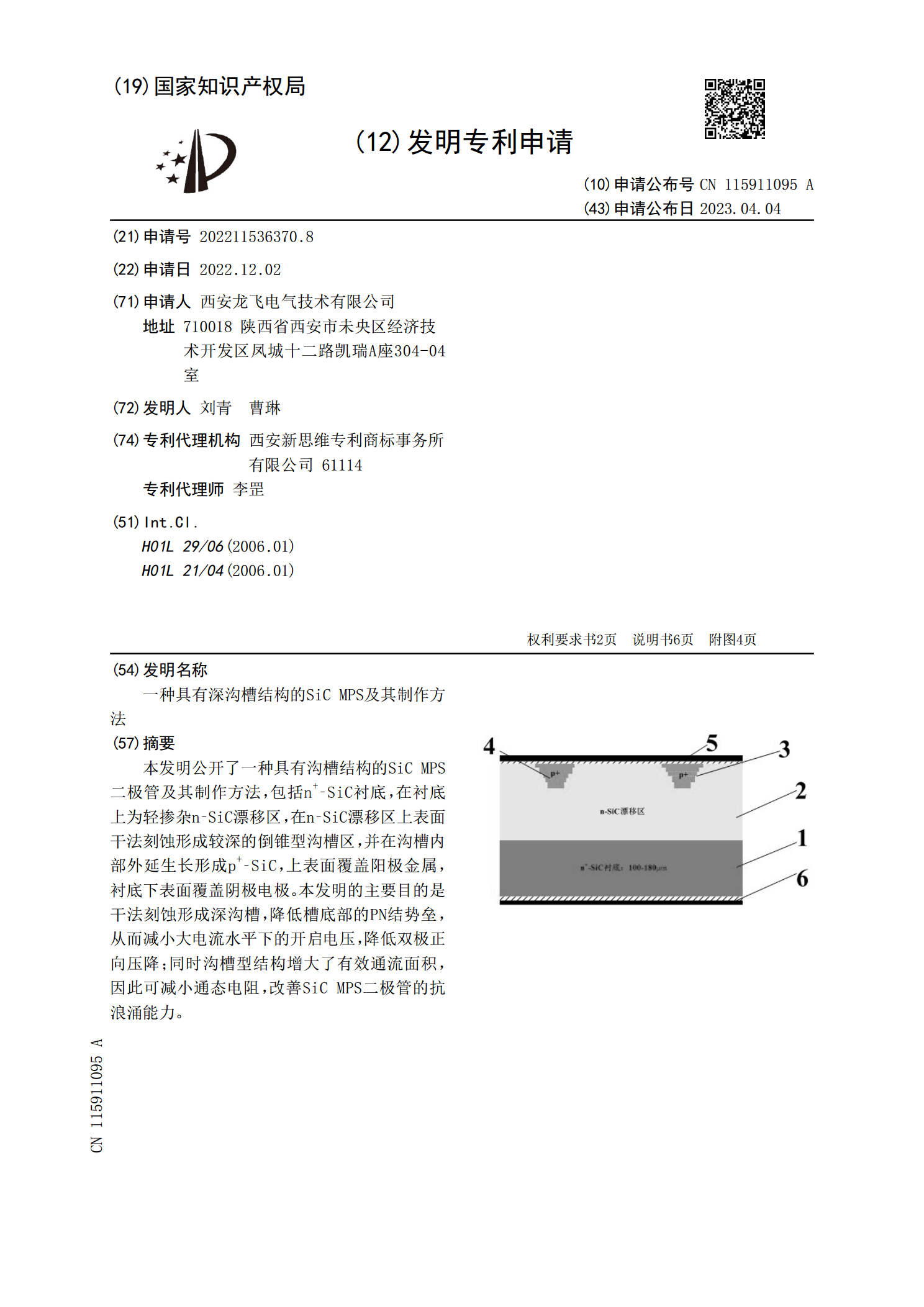

一种具有深沟槽结构的SiC MPS及其制作方法.pdf

本发明公开了一种具有沟槽结构的SiCMPS二极管及其制作方法,包括n

浅沟槽隔离结构及其制作方法.pdf

本申请涉及一种浅沟槽隔离结构及其制作方法。其中,浅沟槽隔离结构包括:浅沟槽,位于衬底内;离子注入区,位于衬底内,且位于浅沟槽的底壁外围;隔离材料层和等离子体阻挡层,填充于浅沟槽内,且等离子体阻挡层位于离子注入区与隔离材料层之间。等离子体阻挡层可以有效阻止等离子体继续进入离子注入区,从而对离子注入区进行有效保护。因此,本申请可以有效保障离子注入区对漏电通道的阻断作用,进而防止半导体器件的产品良率随工艺节点减小而降低,从而有利于实现相关产品向更先进工艺节点迈进。

一种沟槽型SiC MOSFET器件结构及其制造方法.pdf

本申请公开了一种沟槽型SiCMOSFET器件结构及其制造方法,该方法包括:在SiC衬底上生长SiC外延层;在SiC外延层形成体区;对体区进行源注入,形成源极;在体区内通过刻蚀形成栅沟槽;沉积形成第一介电层和第二介电层,第一介电层覆盖于栅沟槽的第一侧壁、第二侧壁以及底部,第二介电层填充于栅沟槽的第一侧壁和第二侧壁之间的中空区域;去除部分覆盖于第一侧壁的第一介电层,并至少保留覆盖于栅沟槽底部的第一介电层,形成空置区域;在露出于空置区域的第一侧壁表面生长栅氧化层;于栅氧化层和第二介电层之间填充填充物,形成栅极

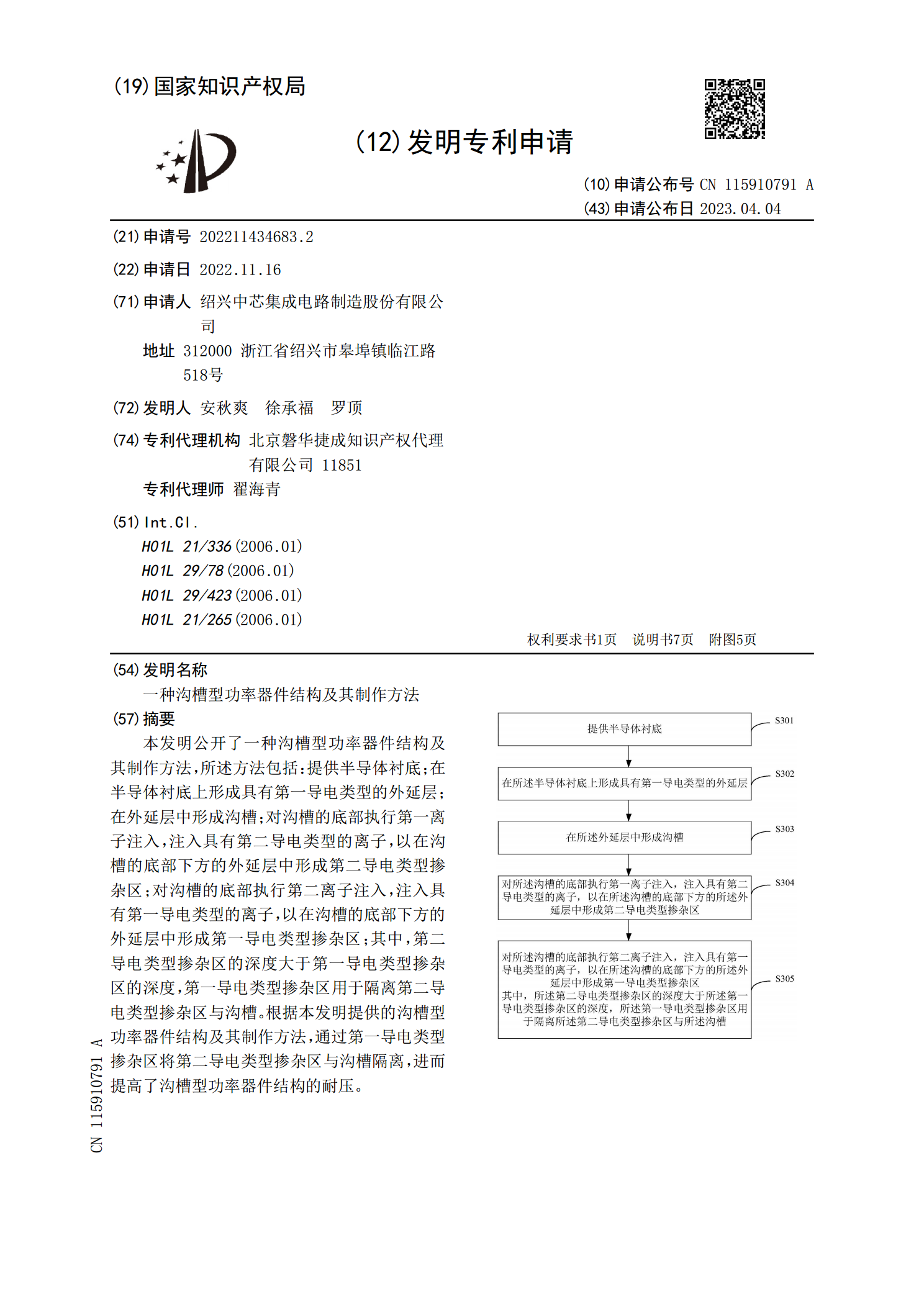

一种沟槽型功率器件结构及其制作方法.pdf

本发明公开了一种沟槽型功率器件结构及其制作方法,所述方法包括:提供半导体衬底;在半导体衬底上形成具有第一导电类型的外延层;在外延层中形成沟槽;对沟槽的底部执行第一离子注入,注入具有第二导电类型的离子,以在沟槽的底部下方的外延层中形成第二导电类型掺杂区;对沟槽的底部执行第二离子注入,注入具有第一导电类型的离子,以在沟槽的底部下方的外延层中形成第一导电类型掺杂区;其中,第二导电类型掺杂区的深度大于第一导电类型掺杂区的深度,第一导电类型掺杂区用于隔离第二导电类型掺杂区与沟槽。根据本发明提供的沟槽型功率器件结构及