一种半导体芯片的加强结构及半导体芯片.pdf

玉环****找我

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种半导体芯片的加强结构及半导体芯片.pdf

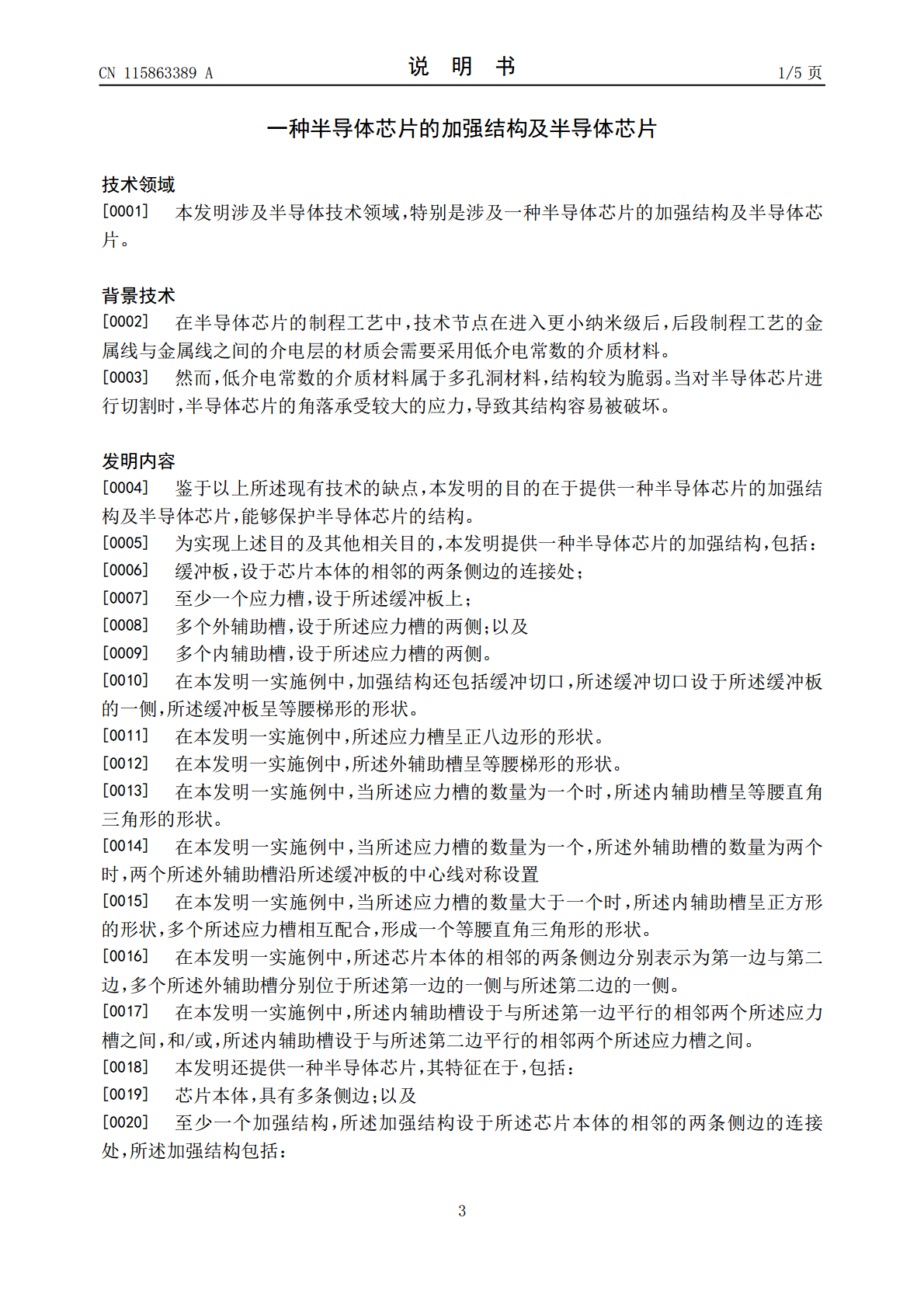

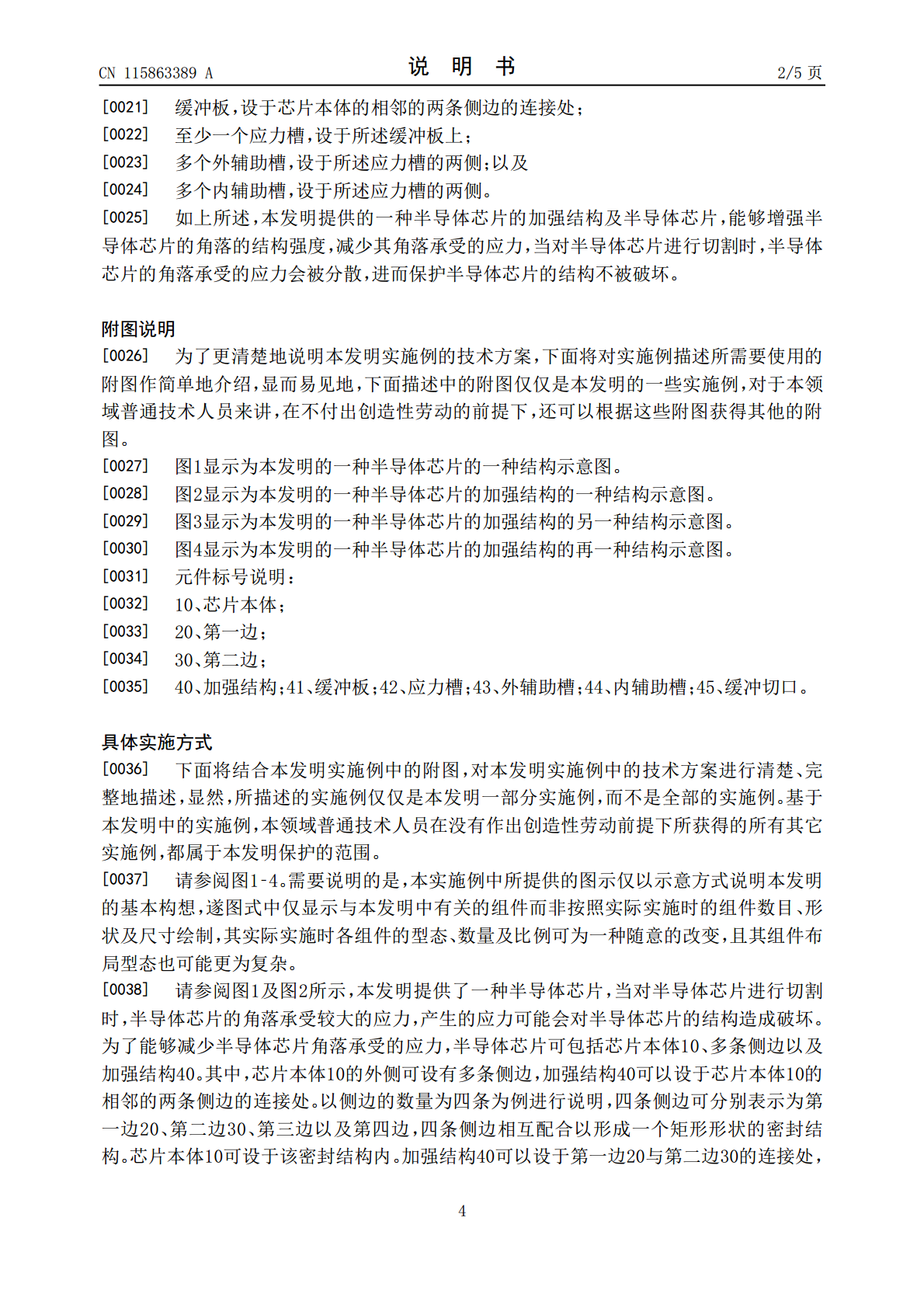

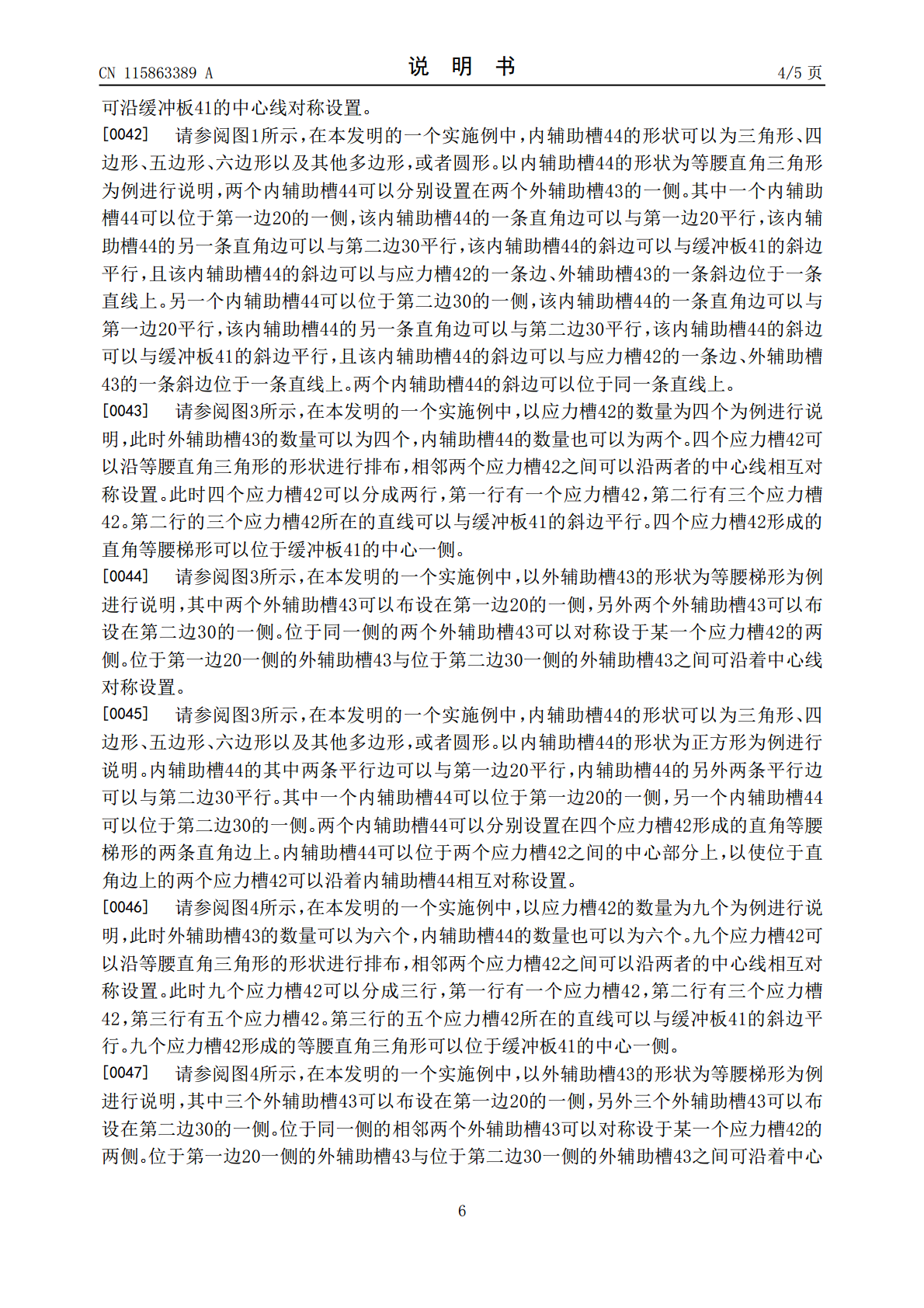

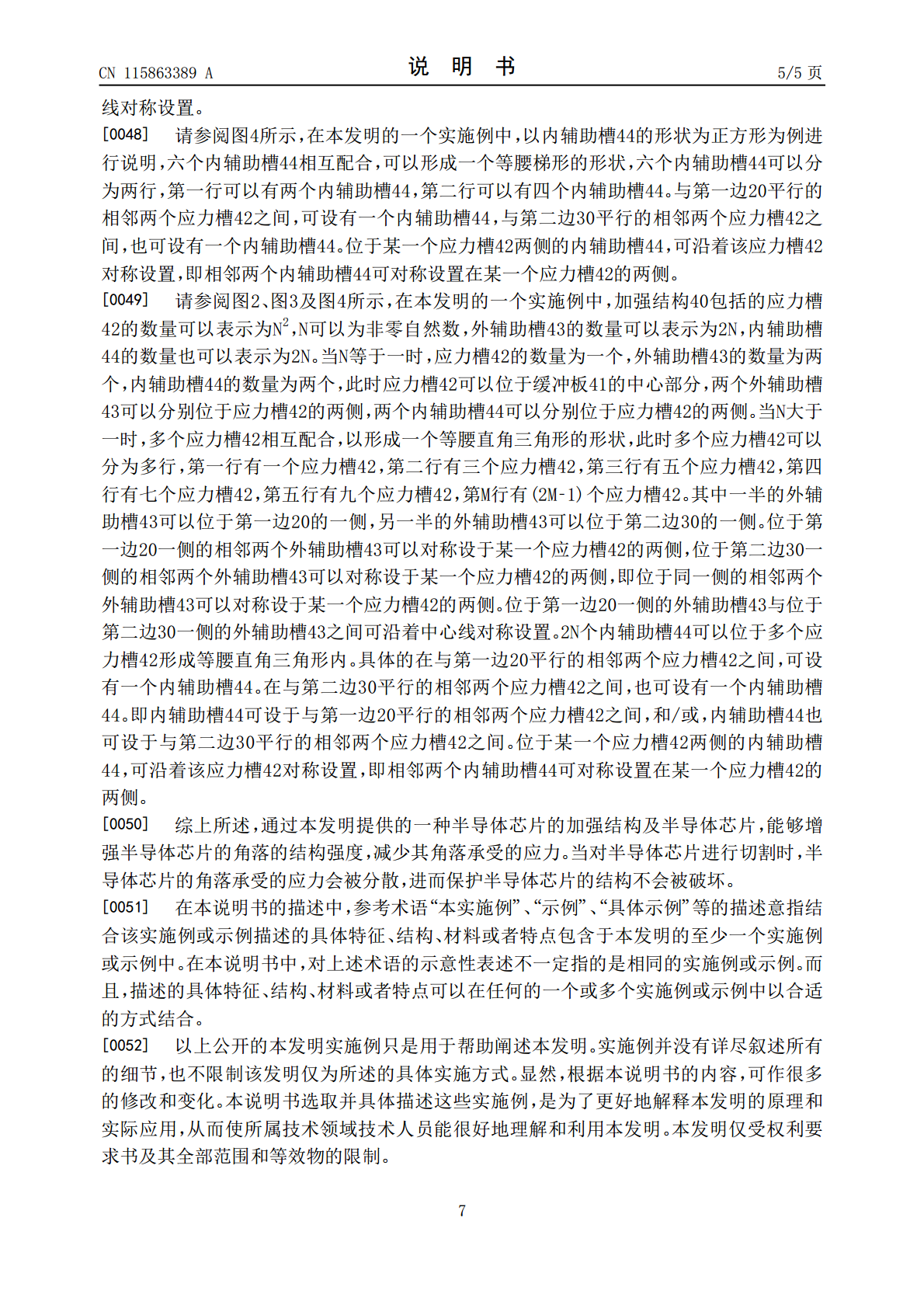

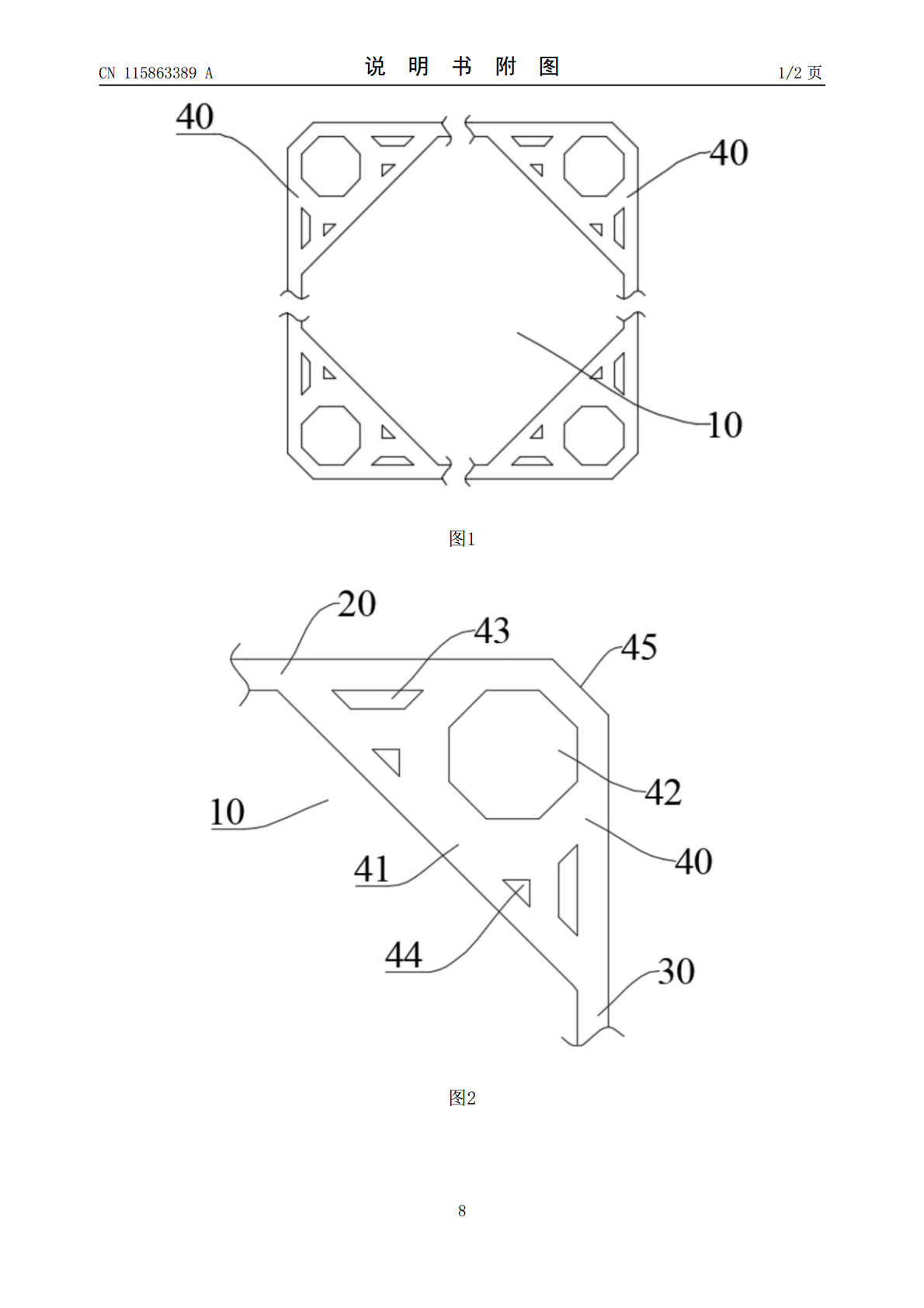

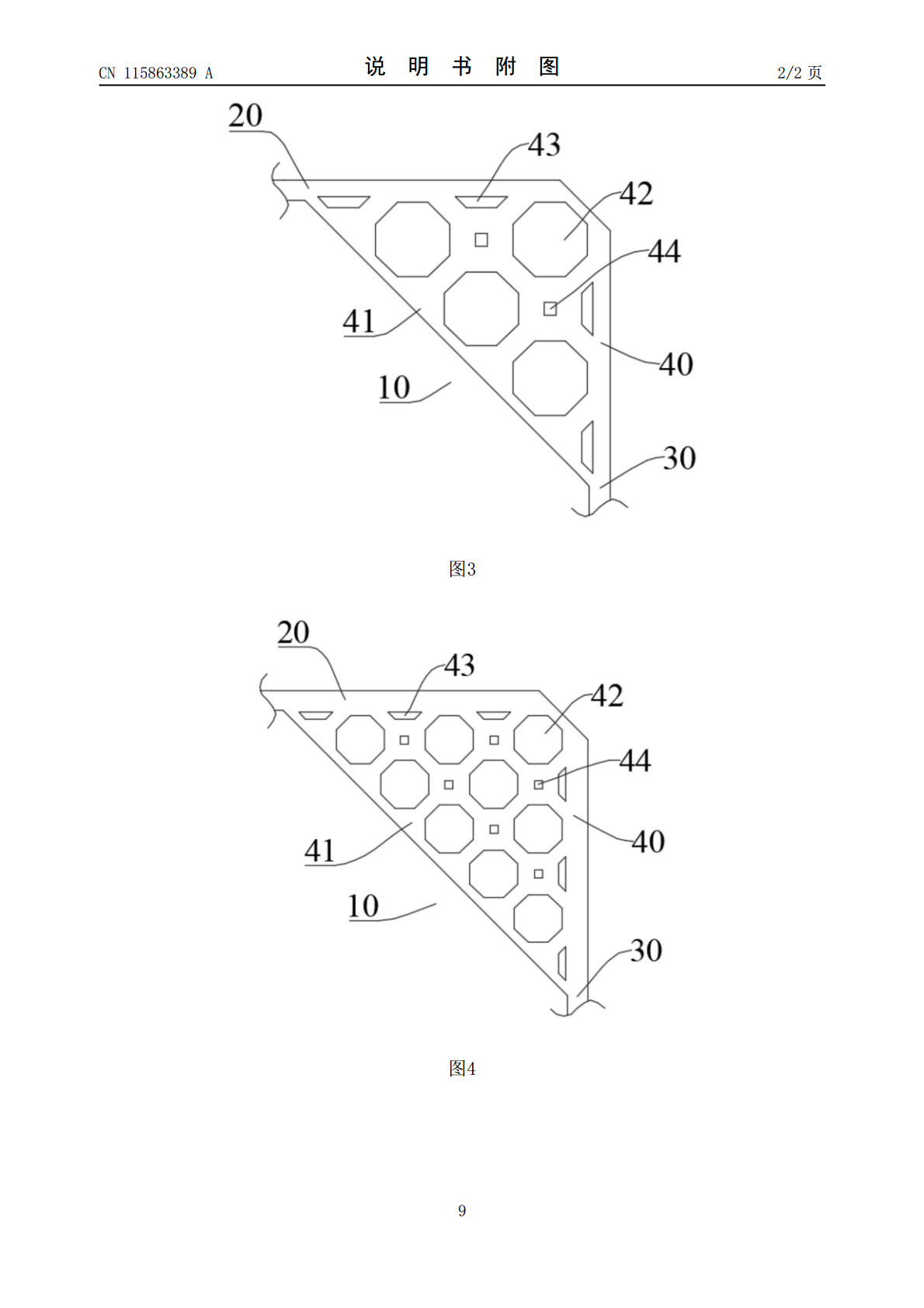

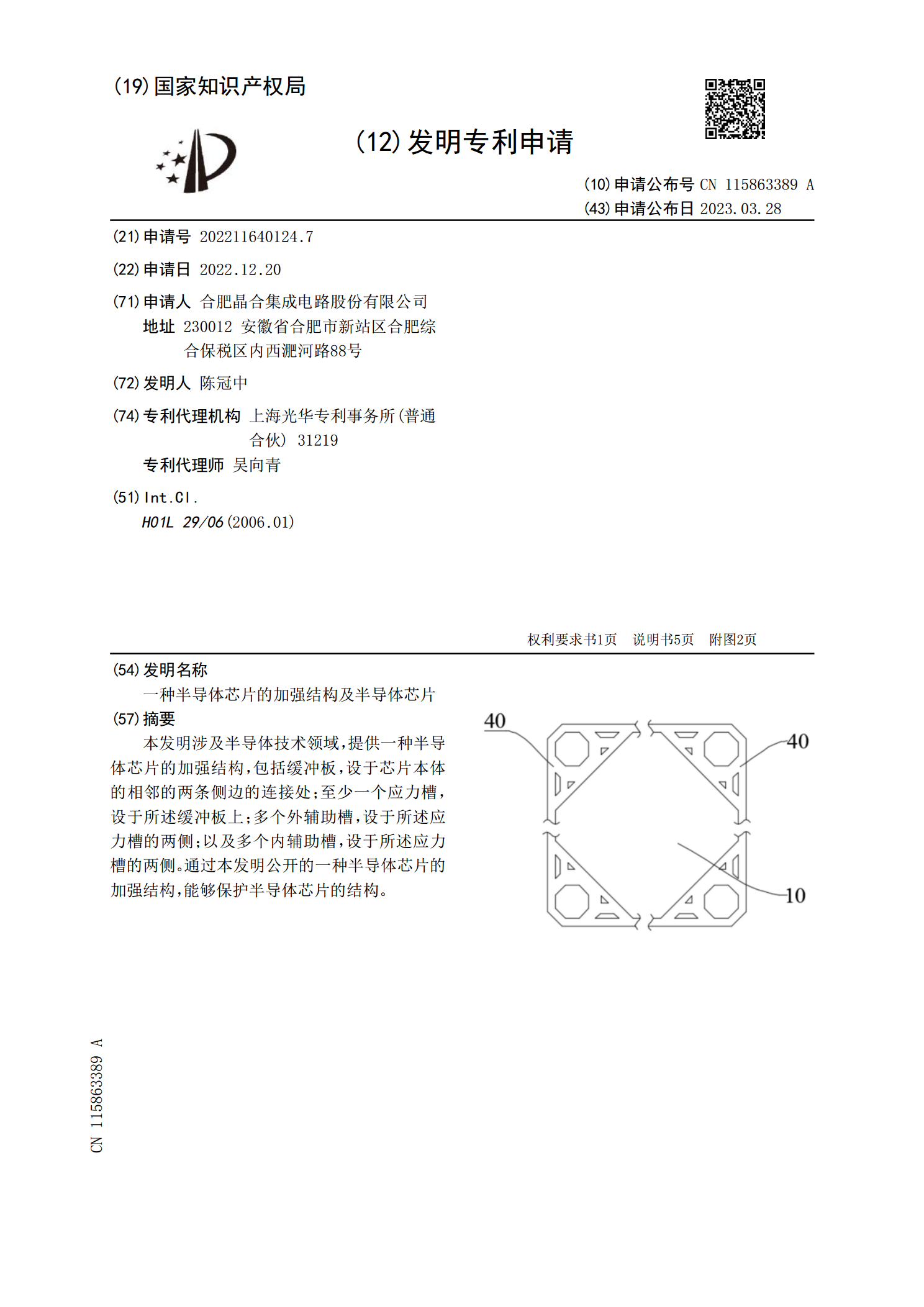

本发明涉及半导体技术领域,提供一种半导体芯片的加强结构,包括缓冲板,设于芯片本体的相邻的两条侧边的连接处;至少一个应力槽,设于所述缓冲板上;多个外辅助槽,设于所述应力槽的两侧;以及多个内辅助槽,设于所述应力槽的两侧。通过本发明公开的一种半导体芯片的加强结构,能够保护半导体芯片的结构。

一种半导体芯片的制造方法及半导体芯片.pdf

本发明公开了一种半导体芯片的制造方法,包括如下步骤:在半导体基片上生长硬掩模介质层,所述半导体基片包括浓掺杂的衬底和轻掺杂的外延层,衬底和外延层的掺杂类型为N型;以硬掩模介质层为阻挡层,采用光刻、刻蚀工艺,在半导体基片上形成沟槽;去除所述硬掩模介质层,生长第一氧化硅、氮化硅以及第二氧化硅;采用化学机械研磨工艺,去除高出所述氮化硅上表面的第二氧化硅,保留所述沟槽中的第二氧化硅;采用离子注入、退火工艺,在所述外延层之中形成第一P型掺杂区;采用腐蚀工艺,去除所述沟槽中的部分第二氧化硅;本发明提供一种半导体芯片,

芯片以及半导体结构.pdf

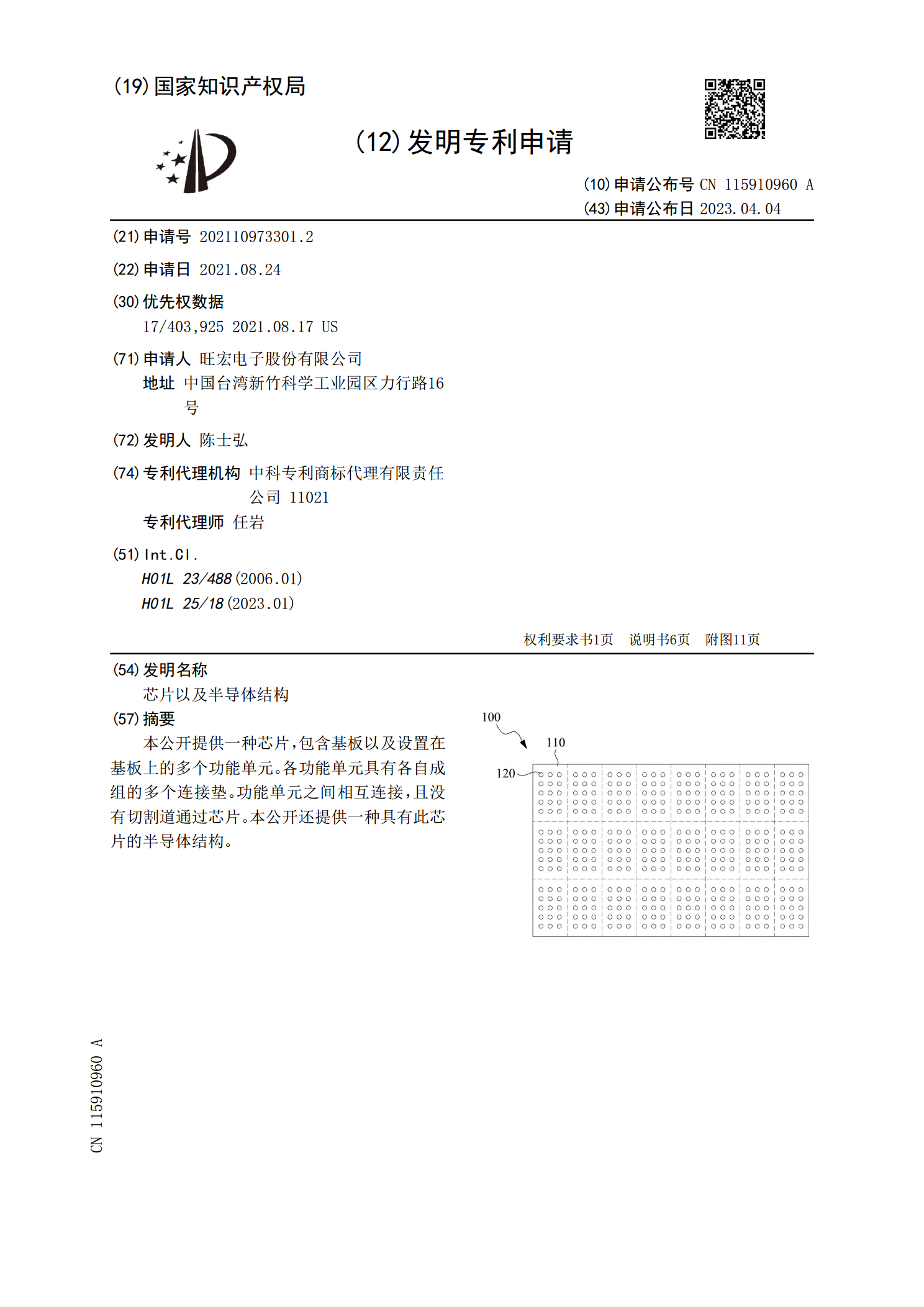

本公开提供一种芯片,包含基板以及设置在基板上的多个功能单元。各功能单元具有各自成组的多个连接垫。功能单元之间相互连接,且没有切割道通过芯片。本公开还提供一种具有此芯片的半导体结构。

半导体芯片的制造方法及半导体芯片.pdf

本发明公开了半导体芯片的制造方法,包括如下步骤:在半导体基片上生长硬掩模介质层,所述半导体基片包括浓掺杂的衬底和轻掺杂的外延层,衬底和外延层的掺杂类型为N型;以硬掩模介质层为阻挡层,采用光刻、刻蚀工艺,在半导体基片上形成沟槽;去除所述硬掩模介质层,生长第一氧化硅、氮化硅以及第二氧化硅;采用化学机械研磨工艺,去除高出所述氮化硅上表面的第二氧化硅,保留所述沟槽中的第二氧化硅;采用离子注入、退火工艺,在所述外延层之中形成第一P型掺杂区和第二P型掺杂区;本发明提供半导体芯片,本发明公开的半导体芯片的制造方法及半导

一种半导体芯片封装结构.pdf

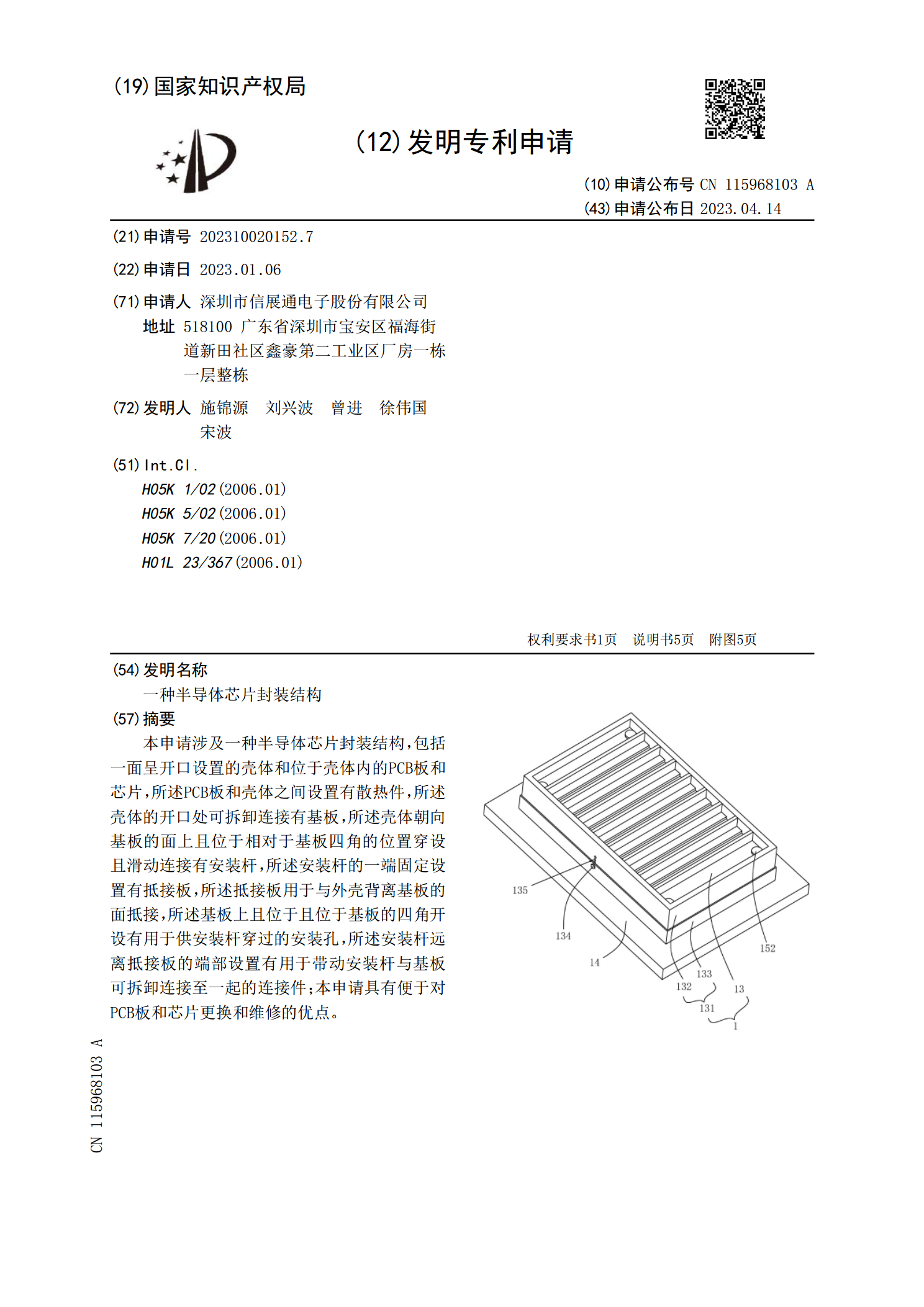

本申请涉及一种半导体芯片封装结构,包括一面呈开口设置的壳体和位于壳体内的PCB板和芯片,所述PCB板和壳体之间设置有散热件,所述壳体的开口处可拆卸连接有基板,所述壳体朝向基板的面上且位于相对于基板四角的位置穿设且滑动连接有安装杆,所述安装杆的一端固定设置有抵接板,所述抵接板用于与外壳背离基板的面抵接,所述基板上且位于且位于基板的四角开设有用于供安装杆穿过的安装孔,所述安装杆远离抵接板的端部设置有用于带动安装杆与基板可拆卸连接至一起的连接件;本申请具有便于对PCB板和芯片更换和维修的优点。