沟槽栅超结IGBT器件及其制造方法.pdf

努力****承悦

亲,该文档总共17页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

沟槽栅超结IGBT器件及其制造方法.pdf

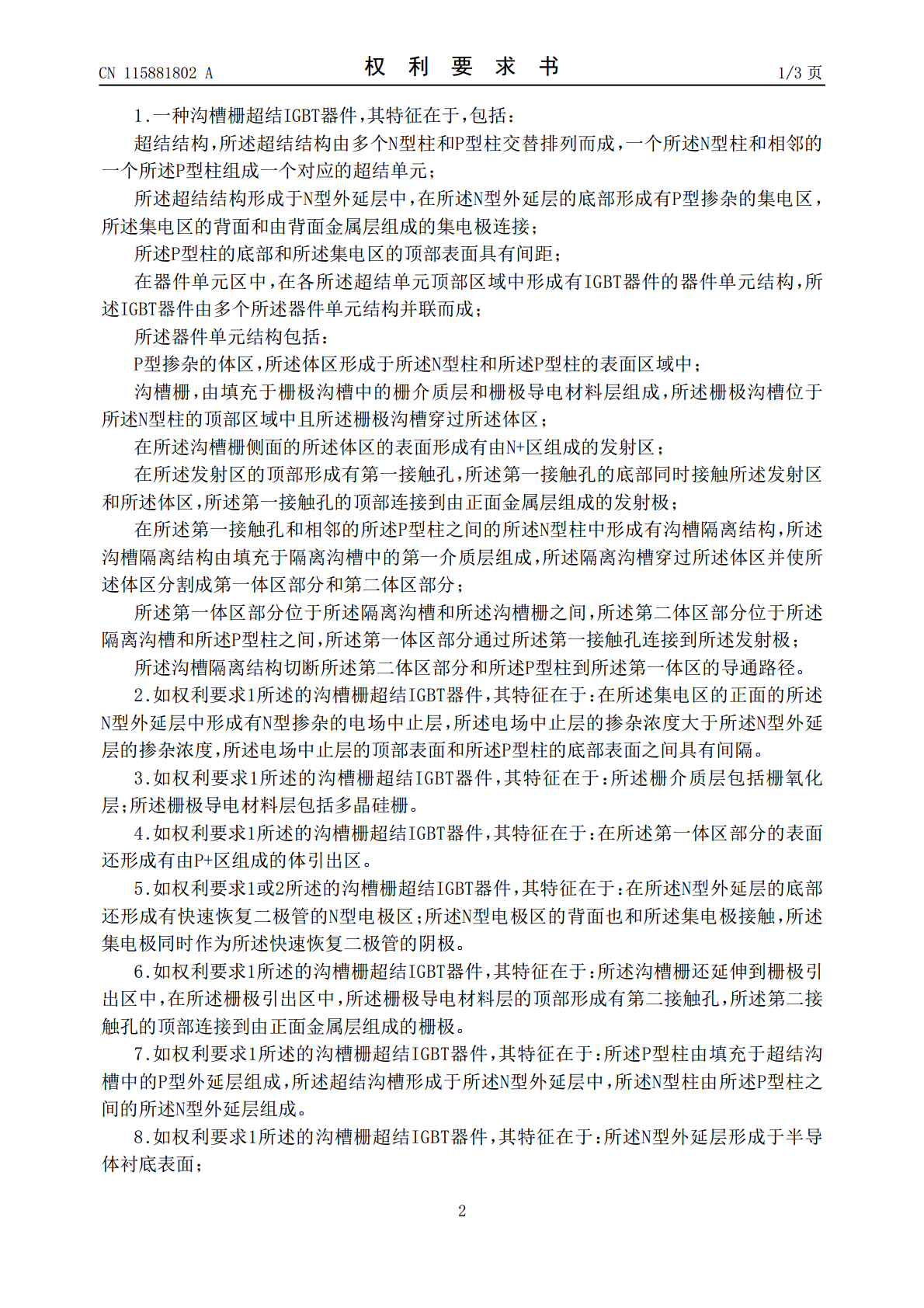

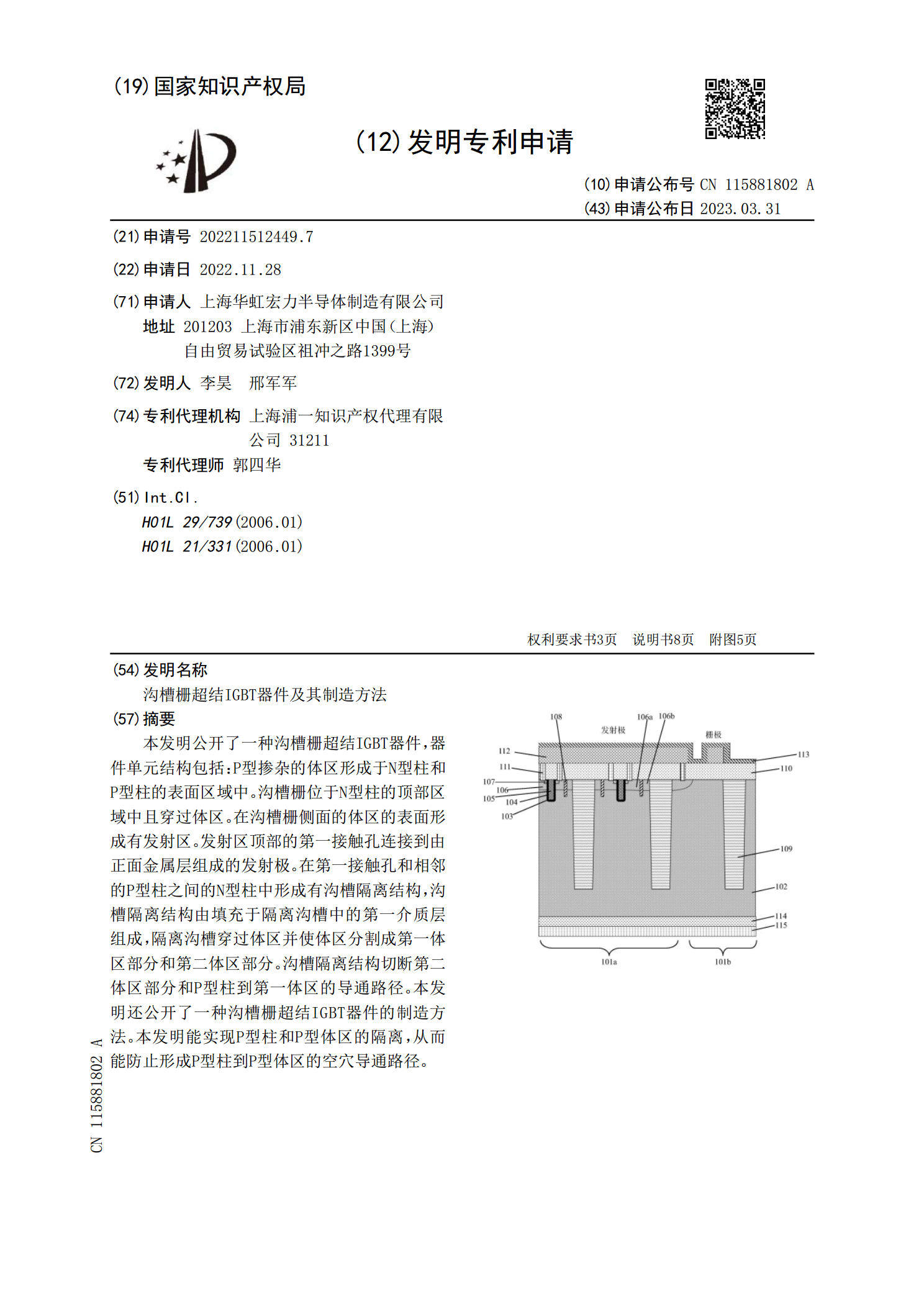

本发明公开了一种沟槽栅超结IGBT器件,器件单元结构包括:P型掺杂的体区形成于N型柱和P型柱的表面区域中。沟槽栅位于N型柱的顶部区域中且穿过体区。在沟槽栅侧面的体区的表面形成有发射区。发射区顶部的第一接触孔连接到由正面金属层组成的发射极。在第一接触孔和相邻的P型柱之间的N型柱中形成有沟槽隔离结构,沟槽隔离结构由填充于隔离沟槽中的第一介质层组成,隔离沟槽穿过体区并使体区分割成第一体区部分和第二体区部分。沟槽隔离结构切断第二体区部分和P型柱到第一体区的导通路径。本发明还公开了一种沟槽栅超结IGBT器件的制造方

一种沟槽栅IGBT器件及其制造方法.pdf

本发明公开了一种沟槽栅IGBT器件及其制造方法。该沟槽栅IGBT器件主要包括:P型基区;通过向P型基区注入N型离子而形成的两个第一N+掺杂区;两个沟槽,其宽度分别小于对应的两个第一N+掺杂区的宽度,使得两个沟槽在靠近彼此的一侧分别留有部分第一N+掺杂区;通过向位于两个部分第一N+掺杂区之间的P型基区注入N型离子而形成的第二N+掺杂区;接触孔,其底部的宽度小于第二N+掺杂区的宽度,使得接触孔两侧留有部分第二N+掺杂区;通过接触孔向P型基区的位于两个部分第一N+掺杂区之间的区域注入P型离子而形成的P+掺杂区;

平面栅沟槽型超级结器件及其制造方法.pdf

本发明公开了一种平面栅沟槽型超级结器件,包括:沟槽型超级结;形成于有源区外的沟槽型超级结的顶部场氧化层;形成于有源区中的沟槽型超级结的各N型薄层表面的多晶硅栅;各多晶硅栅还延伸到对应的场氧化层的表面并组成多晶硅延伸段;各多晶硅延伸段分别通过接触孔连接到同一个金属总线,由金属总线引出栅极衬垫;各多晶硅延伸段的宽度小于等于对应的N型薄层的宽度,使各多晶硅延伸段和各P型薄层的孔洞缺陷在位置上错开。本发明还公开了一种平面栅沟槽型超级结器件的制造方法。本发明防止各多晶硅延伸段跨越P型薄层时各孔洞缺陷中出现多晶硅残留

沟槽栅超结MOSFET的制造方法.pdf

本发明公开了一种沟槽栅超结MOSFET的制造方法,包括步骤:形成硬质掩模层;对硬质掩模层进行光刻刻蚀将沟槽形成区域打开;进行第一次刻蚀形成顶部沟槽;去除顶部沟槽底部的保护层,保留顶部沟槽侧面的保护层;进行第二次刻蚀形成底部沟槽;在底部沟槽中填充P型外延层并形成底部外延填充层;在底部外延填充层的顶部填充P型外延层并形成顶部外延填充层;去除硬质掩模层和保护层从而在P型柱的顶部的周侧形成栅极沟槽;在栅极沟槽中形成栅介质层和填充栅极导电材料。本发明能防止沟槽栅和P型柱之间出现套准偏差,能提高工艺稳定性以及使器件的

一种带有屏蔽栅的超结IGBT及其制造方法.pdf

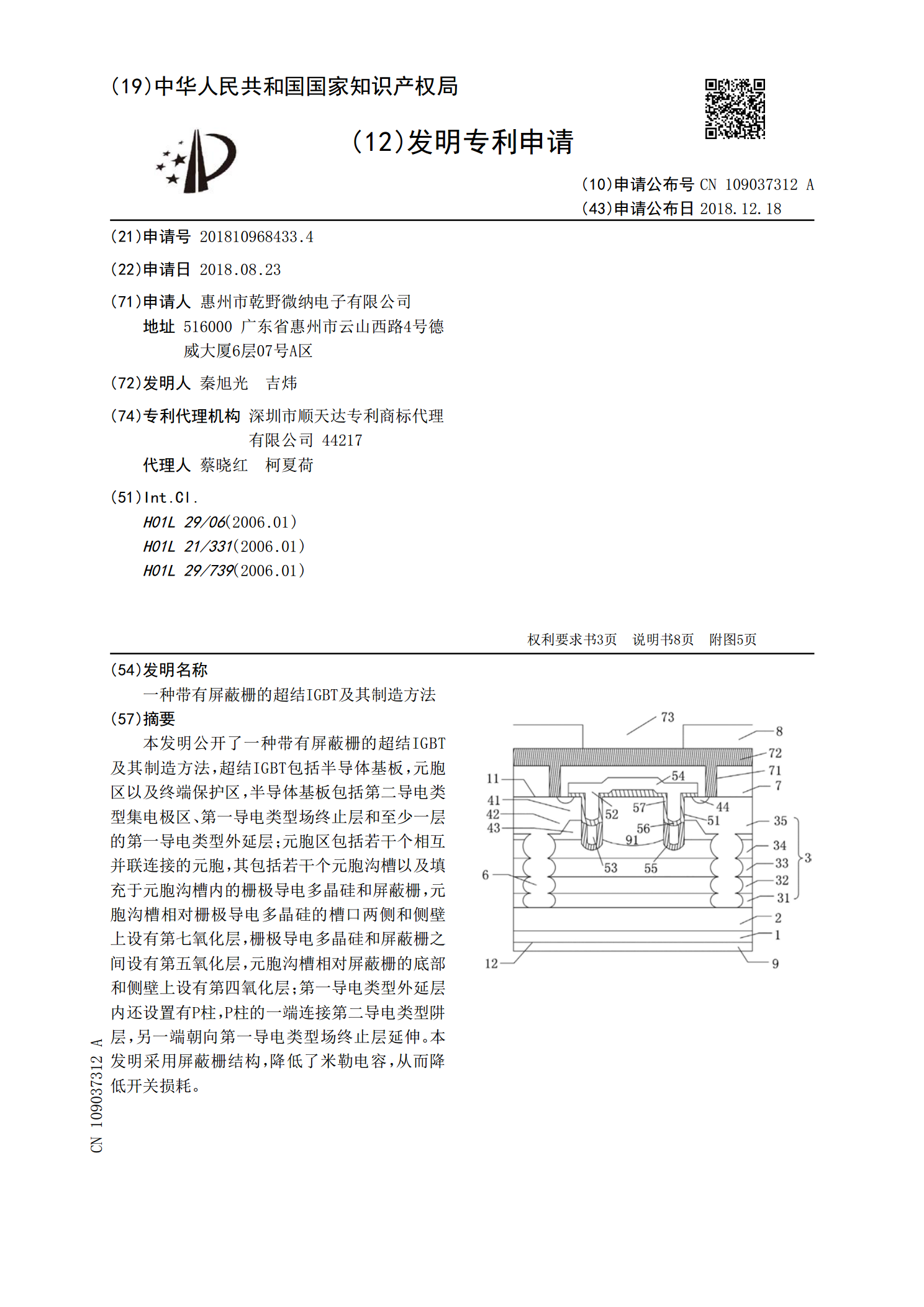

本发明公开了一种带有屏蔽栅的超结IGBT及其制造方法,超结IGBT包括半导体基板,元胞区以及终端保护区,半导体基板包括第二导电类型集电极区、第一导电类型场终止层和至少一层的第一导电类型外延层;元胞区包括若干个相互并联连接的元胞,其包括若干个元胞沟槽以及填充于元胞沟槽内的栅极导电多晶硅和屏蔽栅,元胞沟槽相对栅极导电多晶硅的槽口两侧和侧壁上设有第七氧化层,栅极导电多晶硅和屏蔽栅之间设有第五氧化层,元胞沟槽相对屏蔽栅的底部和侧壁上设有第四氧化层;第一导电类型外延层内还设置有P柱,P柱的一端连接第二导电类型阱层,