衬底结构的制造方法以及衬底结构.pdf

一条****涛k

亲,该文档总共17页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

衬底结构的制造方法以及衬底结构.pdf

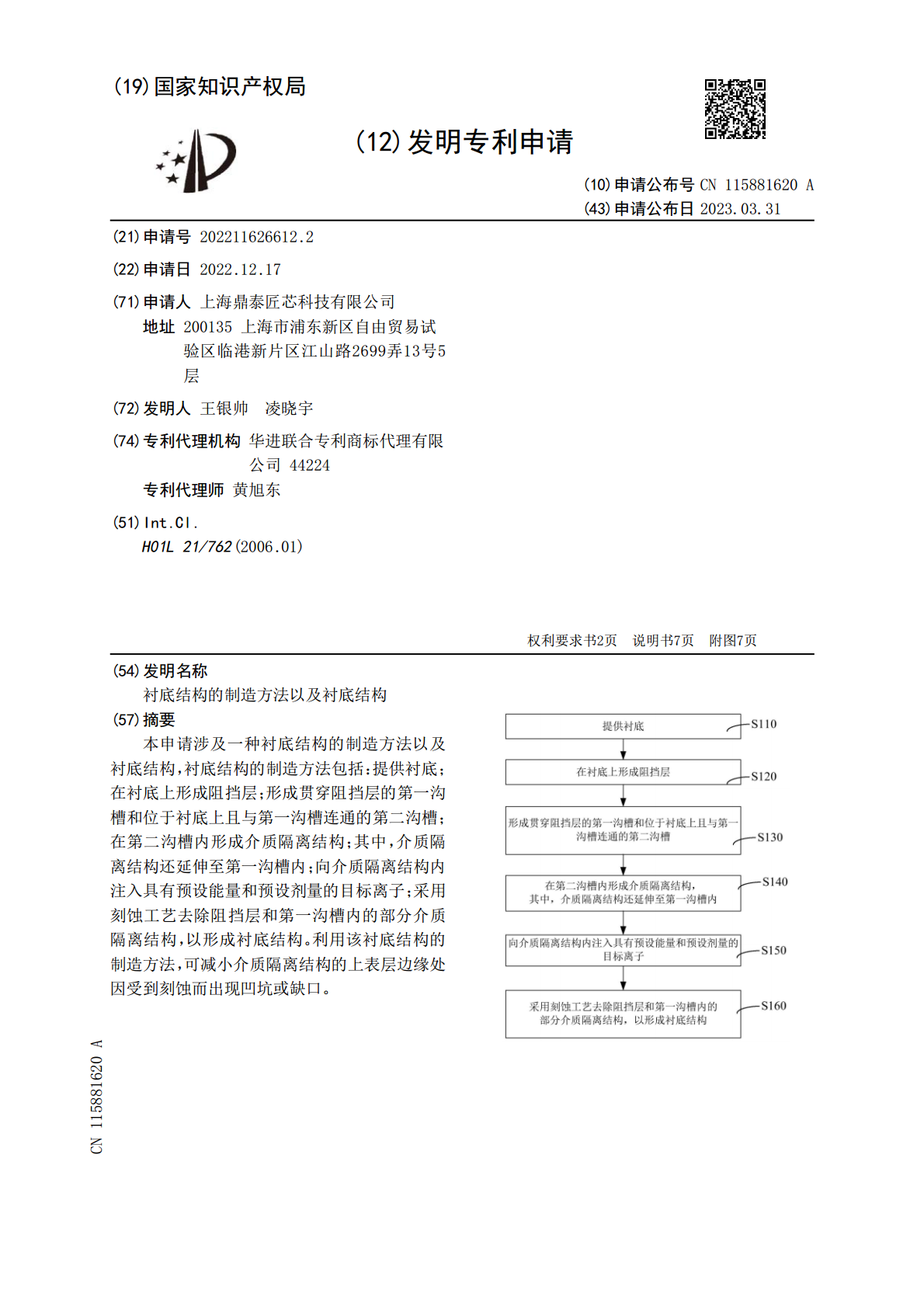

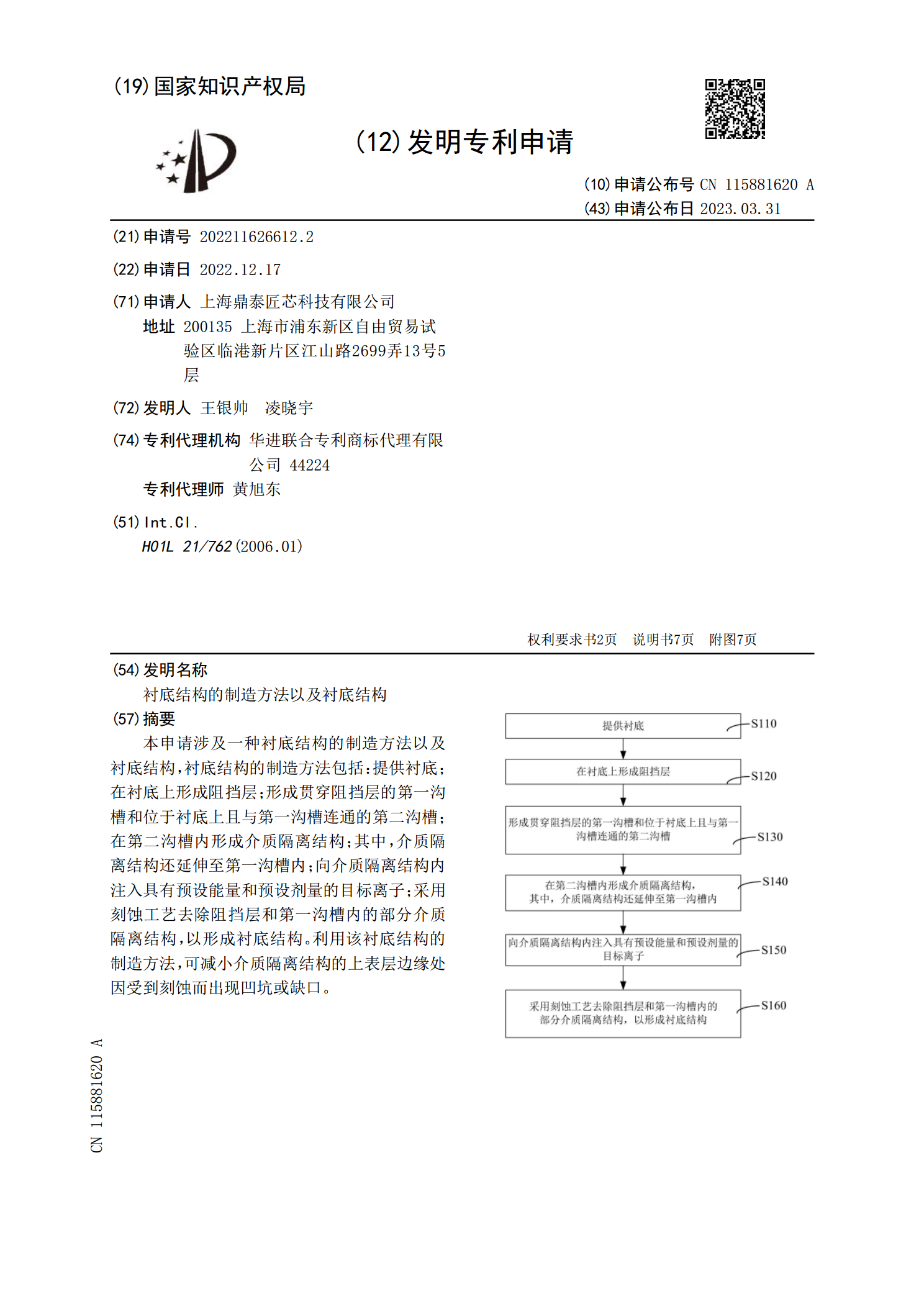

本申请涉及一种衬底结构的制造方法以及衬底结构,衬底结构的制造方法包括:提供衬底;在衬底上形成阻挡层;形成贯穿阻挡层的第一沟槽和位于衬底上且与第一沟槽连通的第二沟槽;在第二沟槽内形成介质隔离结构;其中,介质隔离结构还延伸至第一沟槽内;向介质隔离结构内注入具有预设能量和预设剂量的目标离子;采用刻蚀工艺去除阻挡层和第一沟槽内的部分介质隔离结构,以形成衬底结构。利用该衬底结构的制造方法,可减小介质隔离结构的上表层边缘处因受到刻蚀而出现凹坑或缺口。

衬底结构及制造工艺.pdf

一种衬底结构包括至少一个可拆卸第一衬底单元及衬底主体。所述可拆卸第一衬底单元包括多个角隅及多个第一啮合部分。每一个所述第一啮合部分设置在所述可拆卸第一衬底单元的每一个所述角隅。所述衬底主体包括多个第二衬底单元、至少一个开口及多个第二啮合部分。所述开口实质上由所述第二衬底单元的多个侧壁界定,且包括多个角隅。每一个所述第二啮合部分设置在所述开口的每一个所述角隅。所述可拆卸第一衬底单元设置在所述开口中,且所述第二啮合部分与所述第一啮合部分啮合。

衬底-产品衬底-组合以及用于制造衬底-产品衬底-组合的设备和方法.pdf

本发明涉及一种用于通过将平面衬底(2,2′)的接触侧(2o)与载体衬底(5,5′)的支撑面(5o)对准、接触和接合来制造衬底-产品衬底-组合的方法,其中,所述衬底(2,2′)在接触时具有比所述载体衬底(5,5′)的平均直径d2更大的平均直径d1。此外,本发明还涉及一种用于通过将平面衬底(2,2′)的接触侧(2o)与载体衬底(5,5′)的支撑面(5o)对准、接触和接合来制造衬底-产品衬底-组合的衬底(2,2′),其中,所述衬底(2,2′)具有直径d1,该直径在背面减薄时可通过所述衬底(2,2′)的横截面的形

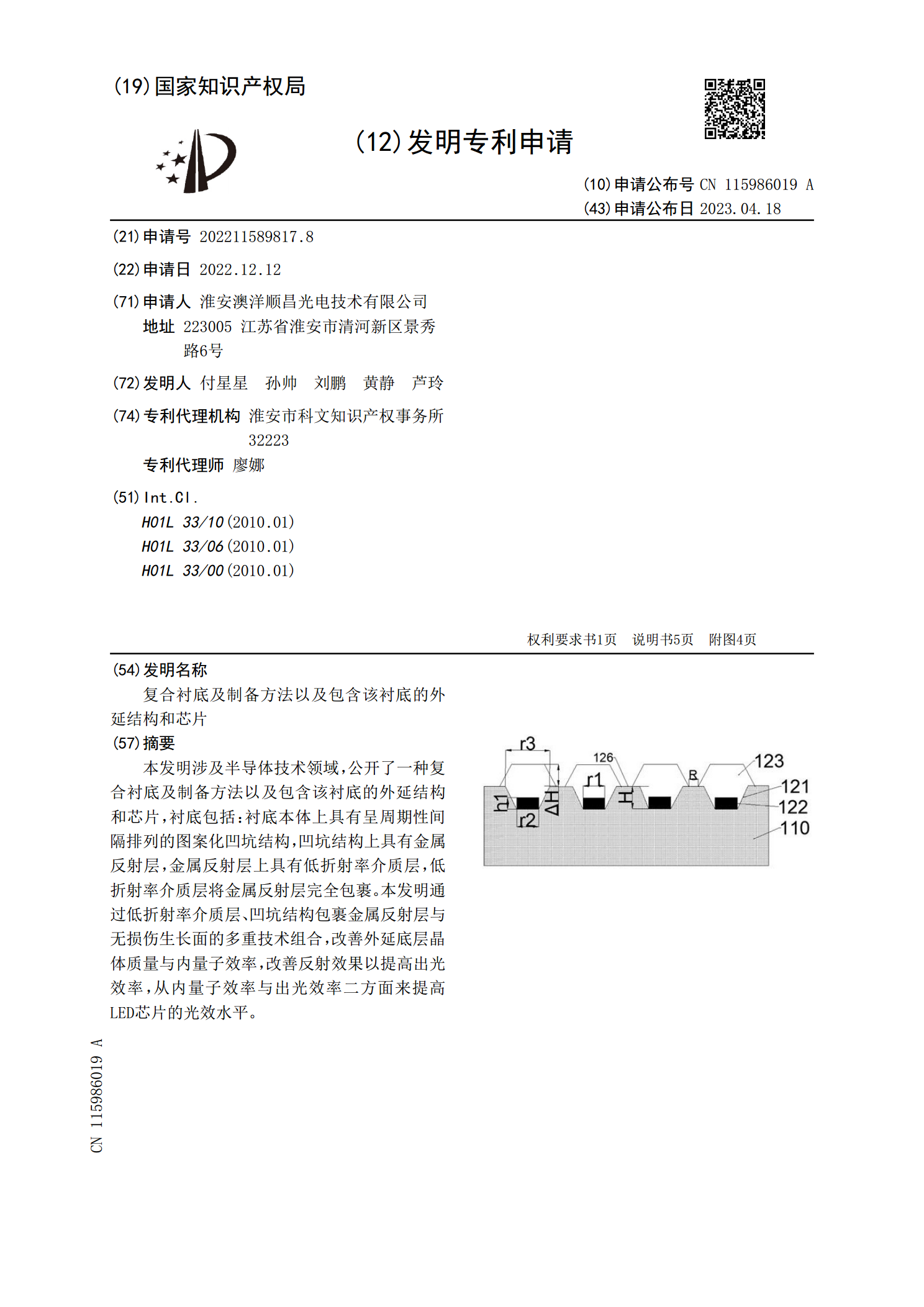

复合衬底及制备方法以及包含该衬底的外延结构和芯片.pdf

本发明涉及半导体技术领域,公开了一种复合衬底及制备方法以及包含该衬底的外延结构和芯片,衬底包括:衬底本体上具有呈周期性间隔排列的图案化凹坑结构,凹坑结构上具有金属反射层,金属反射层上具有低折射率介质层,低折射率介质层将金属反射层完全包裹。本发明通过低折射率介质层、凹坑结构包裹金属反射层与无损伤生长面的多重技术组合,改善外延底层晶体质量与内量子效率,改善反射效果以提高出光效率,从内量子效率与出光效率二方面来提高LED芯片的光效水平。

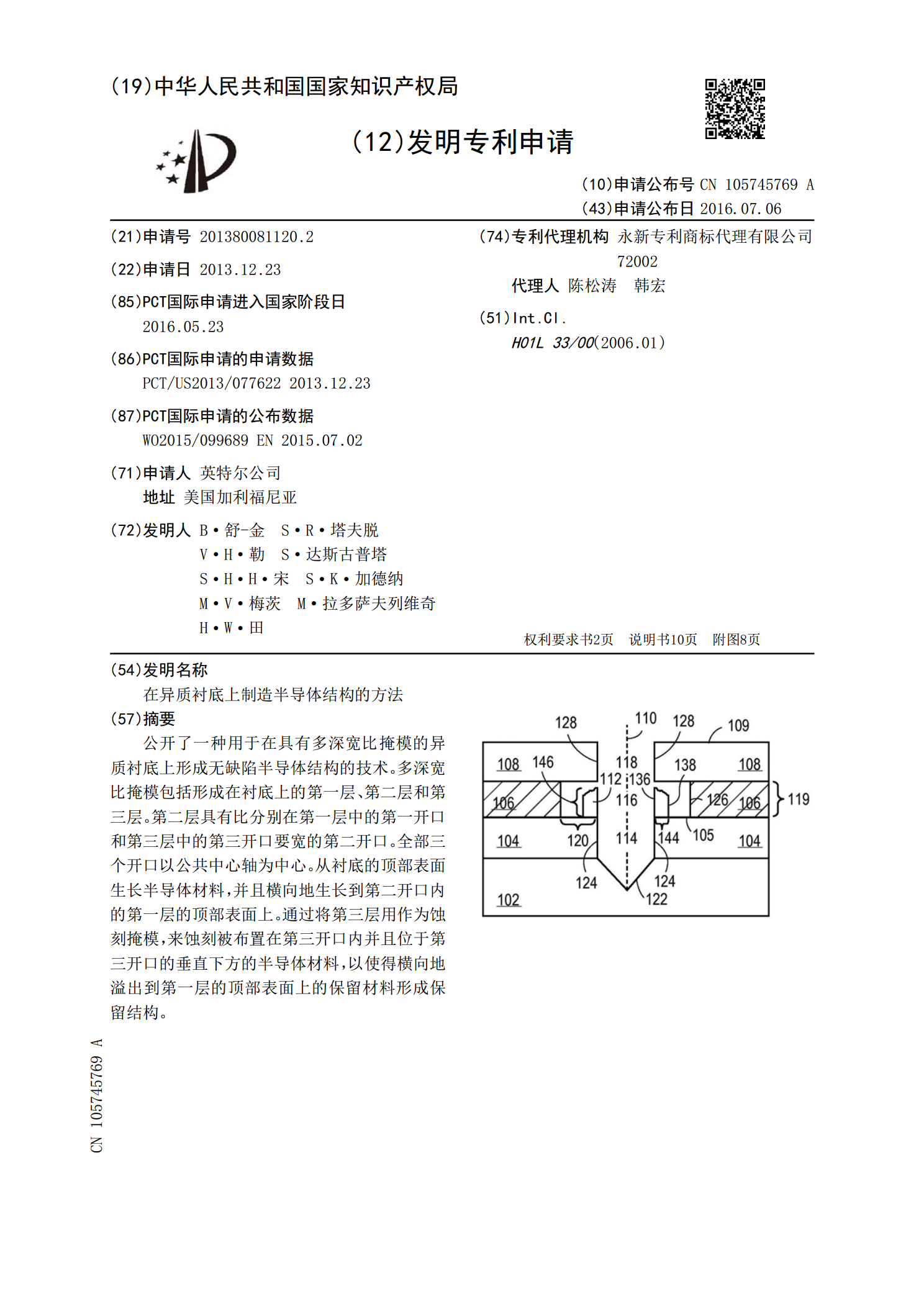

在异质衬底上制造半导体结构的方法.pdf

公开了一种用于在具有多深宽比掩模的异质衬底上形成无缺陷半导体结构的技术。多深宽比掩模包括形成在衬底上的第一层、第二层和第三层。第二层具有比分别在第一层中的第一开口和第三层中的第三开口要宽的第二开口。全部三个开口以公共中心轴为中心。从衬底的顶部表面生长半导体材料,并且横向地生长到第二开口内的第一层的顶部表面上。通过将第三层用作为蚀刻掩模,来蚀刻被布置在第三开口内并且位于第三开口的垂直下方的半导体材料,以使得横向地溢出到第一层的顶部表面上的保留材料形成保留结构。