晶体管结构、半导体结构及其制备方法.pdf

雨巷****珺琦

亲,该文档总共15页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

晶体管结构、半导体结构及其制备方法.pdf

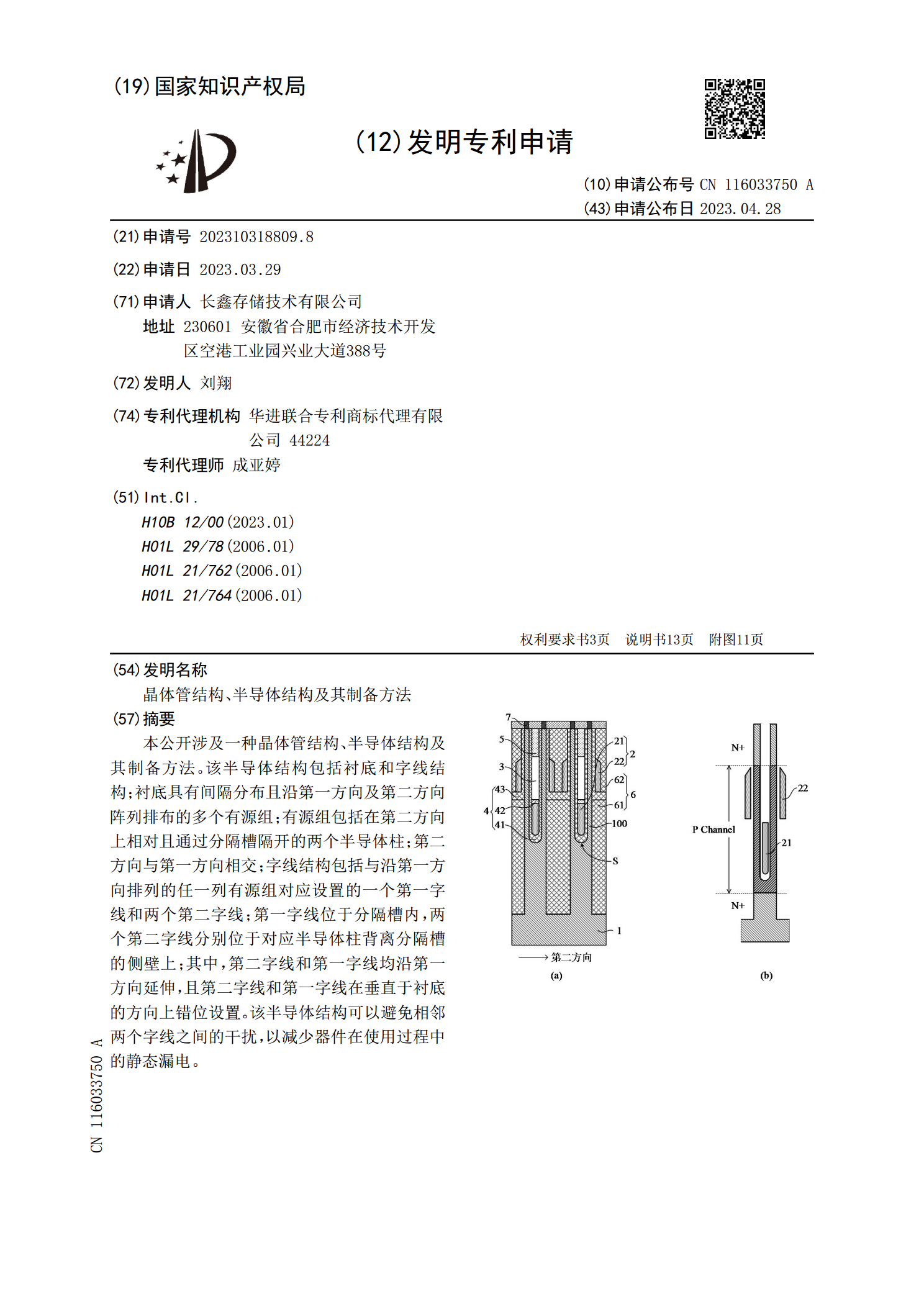

(19)国家知识产权局(12)发明专利申请(10)申请公布号CN116033750A(43)申请公布日2023.04.28(21)申请号202310318809.8(22)申请日2023.03.29(71)申请人长鑫存储技术有限公司地址230601安徽省合肥市经济技术开发区空港工业园兴业大道388号(72)发明人刘翔(74)专利代理机构华进联合专利商标代理有限公司44224专利代理师成亚婷(51)Int.Cl.H10B12/00(2023.01)H01L29/78(2006.01)H01L21/762(2

晶体管结构、半导体结构及其制备方法.pdf

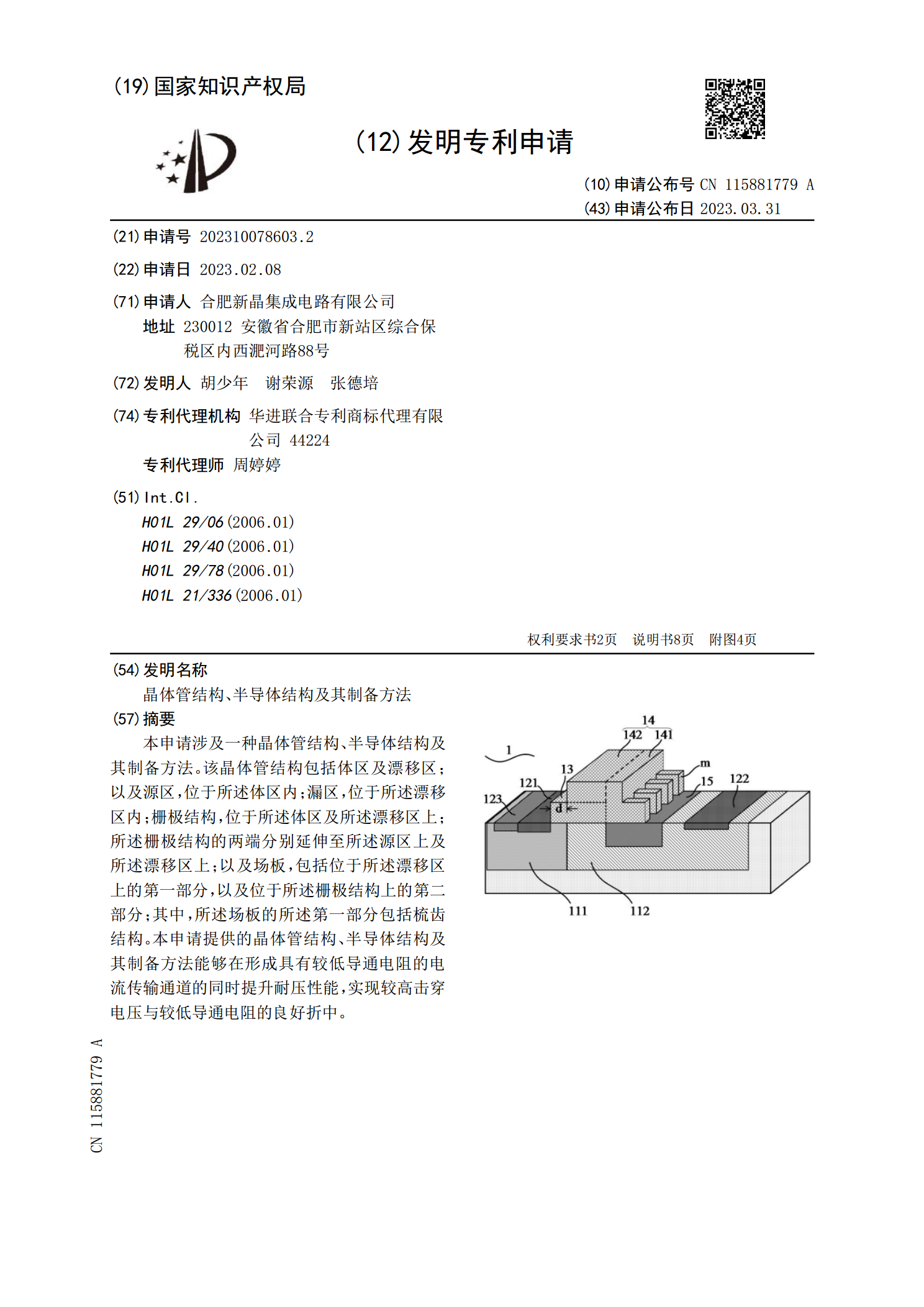

本申请涉及一种晶体管结构、半导体结构及其制备方法。该晶体管结构包括体区及漂移区;以及源区,位于所述体区内;漏区,位于所述漂移区内;栅极结构,位于所述体区及所述漂移区上;所述栅极结构的两端分别延伸至所述源区上及所述漂移区上;以及场板,包括位于所述漂移区上的第一部分,以及位于所述栅极结构上的第二部分;其中,所述场板的所述第一部分包括梳齿结构。本申请提供的晶体管结构、半导体结构及其制备方法能够在形成具有较低导通电阻的电流传输通道的同时提升耐压性能,实现较高击穿电压与较低导通电阻的良好折中。

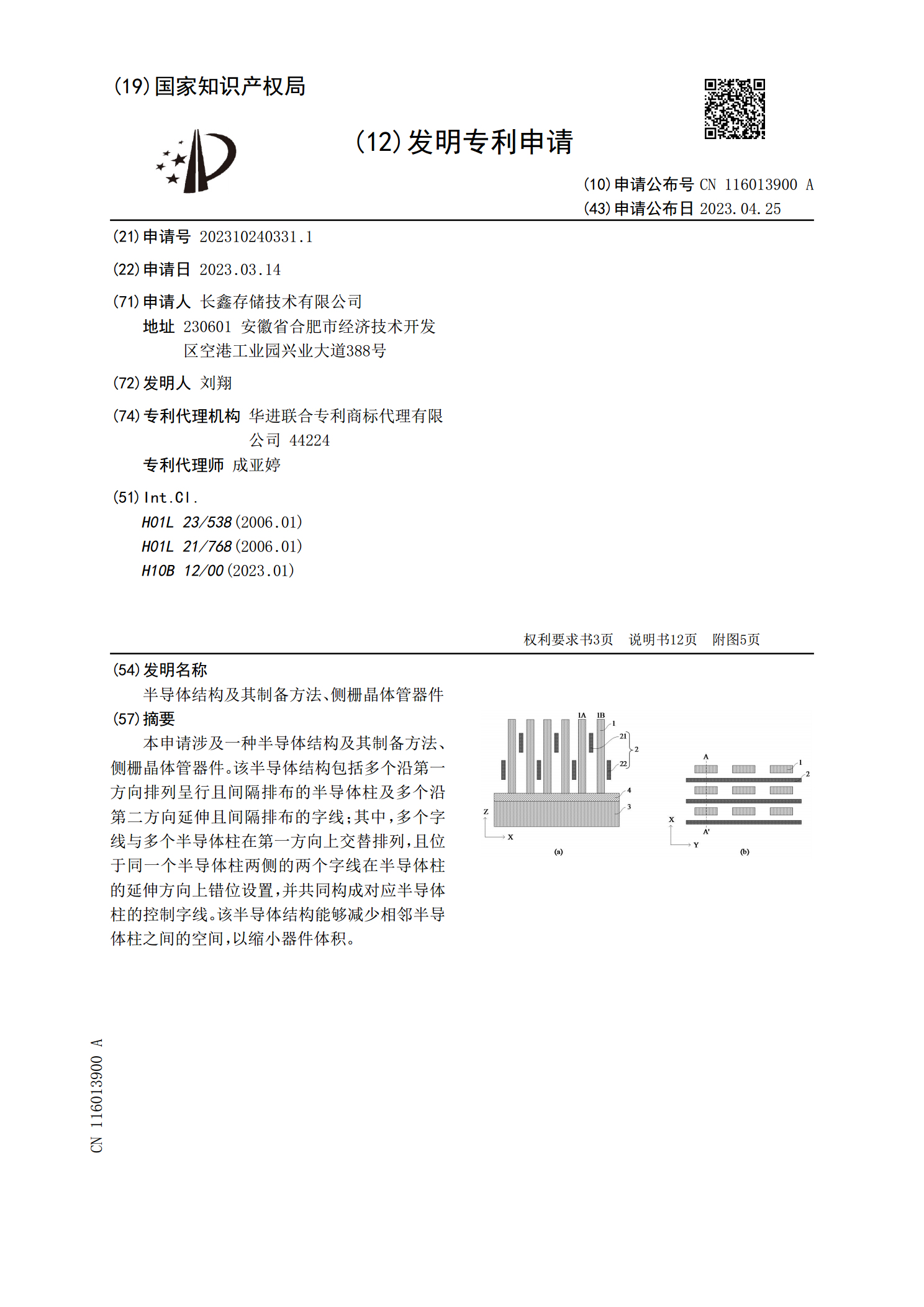

半导体结构及其制备方法、侧栅晶体管器件.pdf

本申请涉及一种半导体结构及其制备方法、侧栅晶体管器件。该半导体结构包括多个沿第一方向排列呈行且间隔排布的半导体柱及多个沿第二方向延伸且间隔排布的字线;其中,多个字线与多个半导体柱在第一方向上交替排列,且位于同一个半导体柱两侧的两个字线在半导体柱的延伸方向上错位设置,并共同构成对应半导体柱的控制字线。该半导体结构能够减少相邻半导体柱之间的空间,以缩小器件体积。

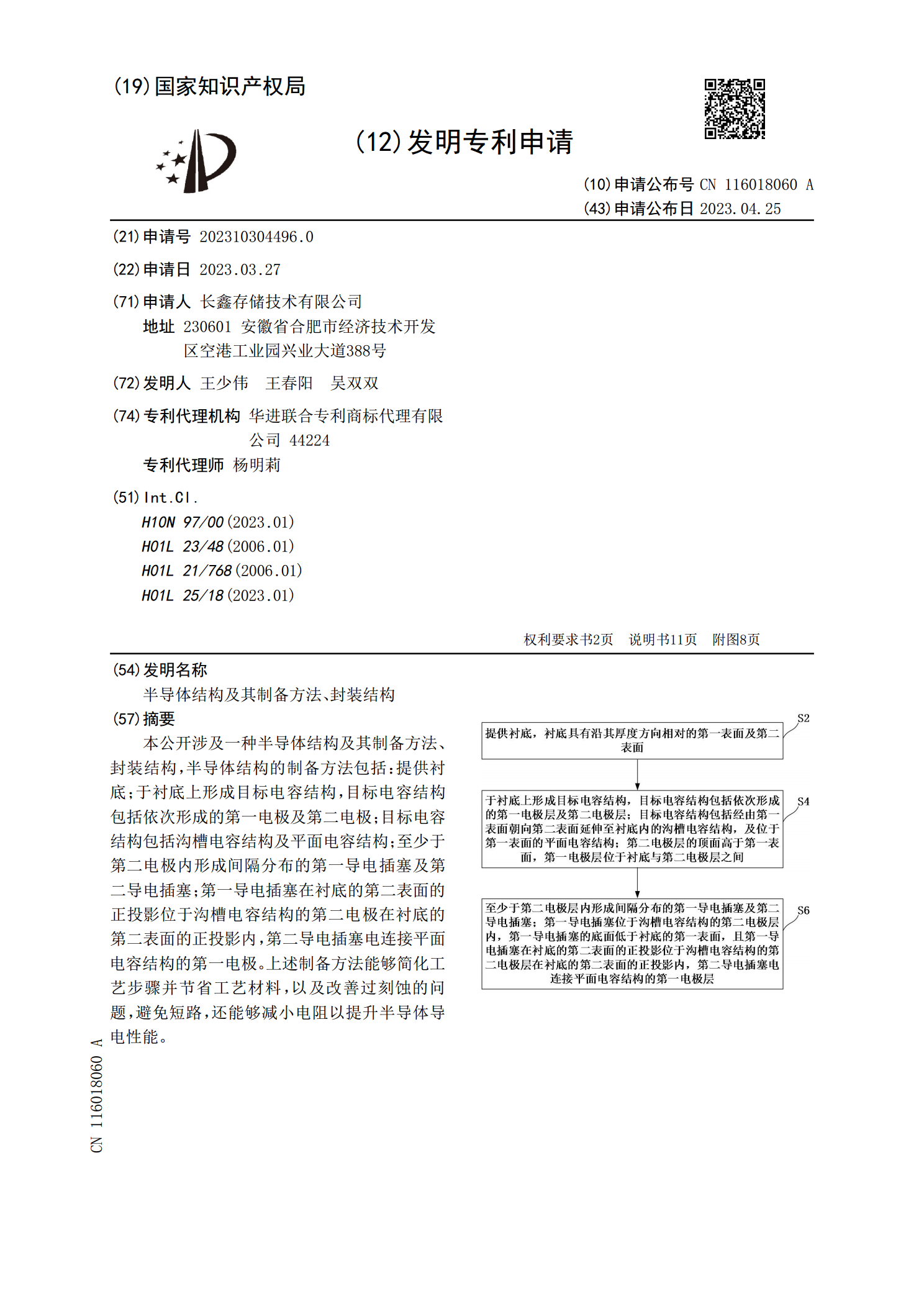

半导体结构及其制备方法、封装结构.pdf

本公开涉及一种半导体结构及其制备方法、封装结构,半导体结构的制备方法包括:提供衬底;于衬底上形成目标电容结构,目标电容结构包括依次形成的第一电极及第二电极;目标电容结构包括沟槽电容结构及平面电容结构;至少于第二电极内形成间隔分布的第一导电插塞及第二导电插塞;第一导电插塞在衬底的第二表面的正投影位于沟槽电容结构的第二电极在衬底的第二表面的正投影内,第二导电插塞电连接平面电容结构的第一电极。上述制备方法能够简化工艺步骤并节省工艺材料,以及改善过刻蚀的问题,避免短路,还能够减小电阻以提升半导体导电性能。

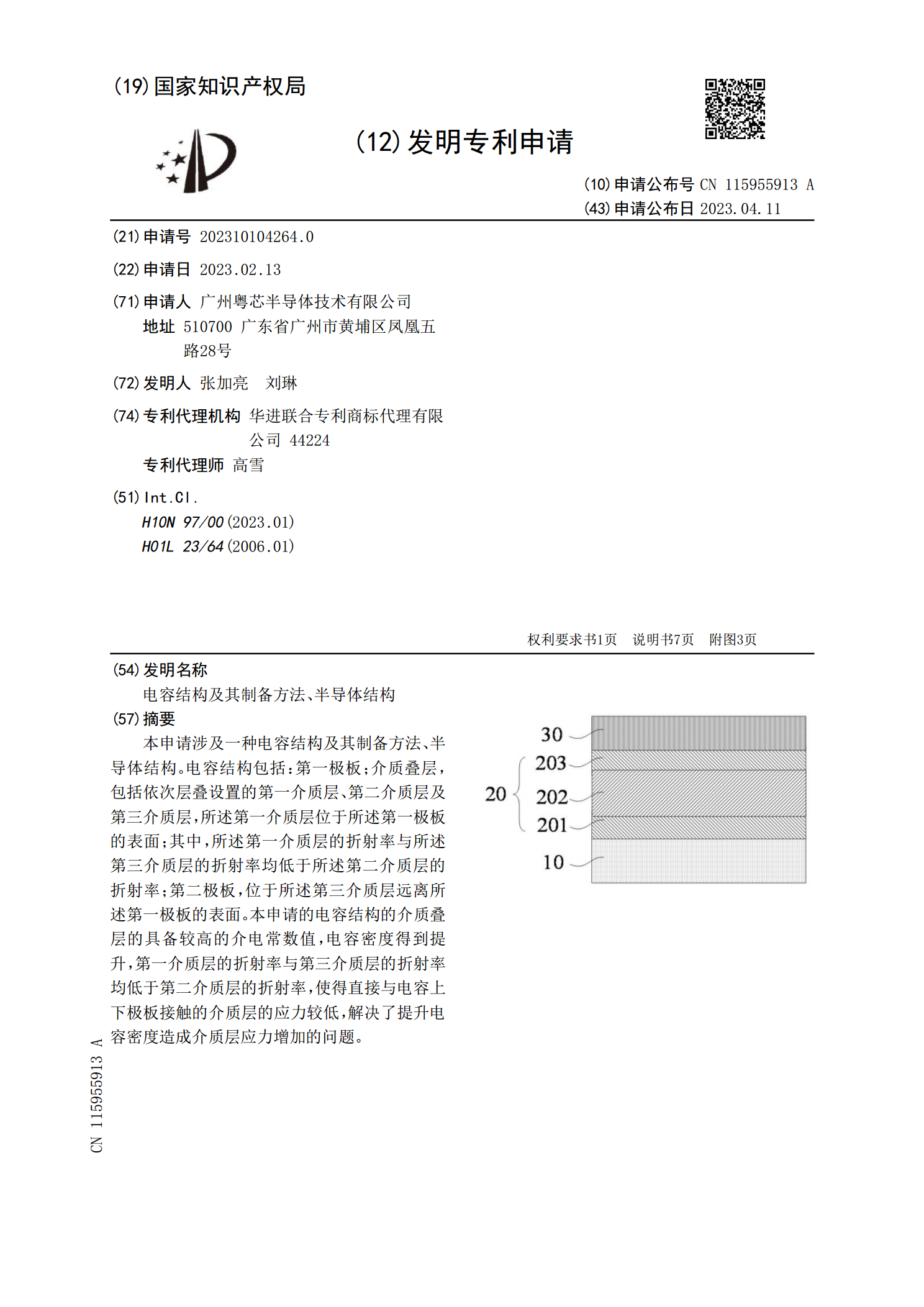

电容结构及其制备方法、半导体结构.pdf

本申请涉及一种电容结构及其制备方法、半导体结构。电容结构包括:第一极板;介质叠层,包括依次层叠设置的第一介质层、第二介质层及第三介质层,所述第一介质层位于所述第一极板的表面;其中,所述第一介质层的折射率与所述第三介质层的折射率均低于所述第二介质层的折射率;第二极板,位于所述第三介质层远离所述第一极板的表面。本申请的电容结构的介质叠层的具备较高的介电常数值,电容密度得到提升,第一介质层的折射率与第三介质层的折射率均低于第二介质层的折射率,使得直接与电容上下极板接触的介质层的应力较低,解决了提升电容密度造成介