屏蔽盾结构及其制造方法.pdf

一吃****仪凡

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

屏蔽盾结构及其制造方法.pdf

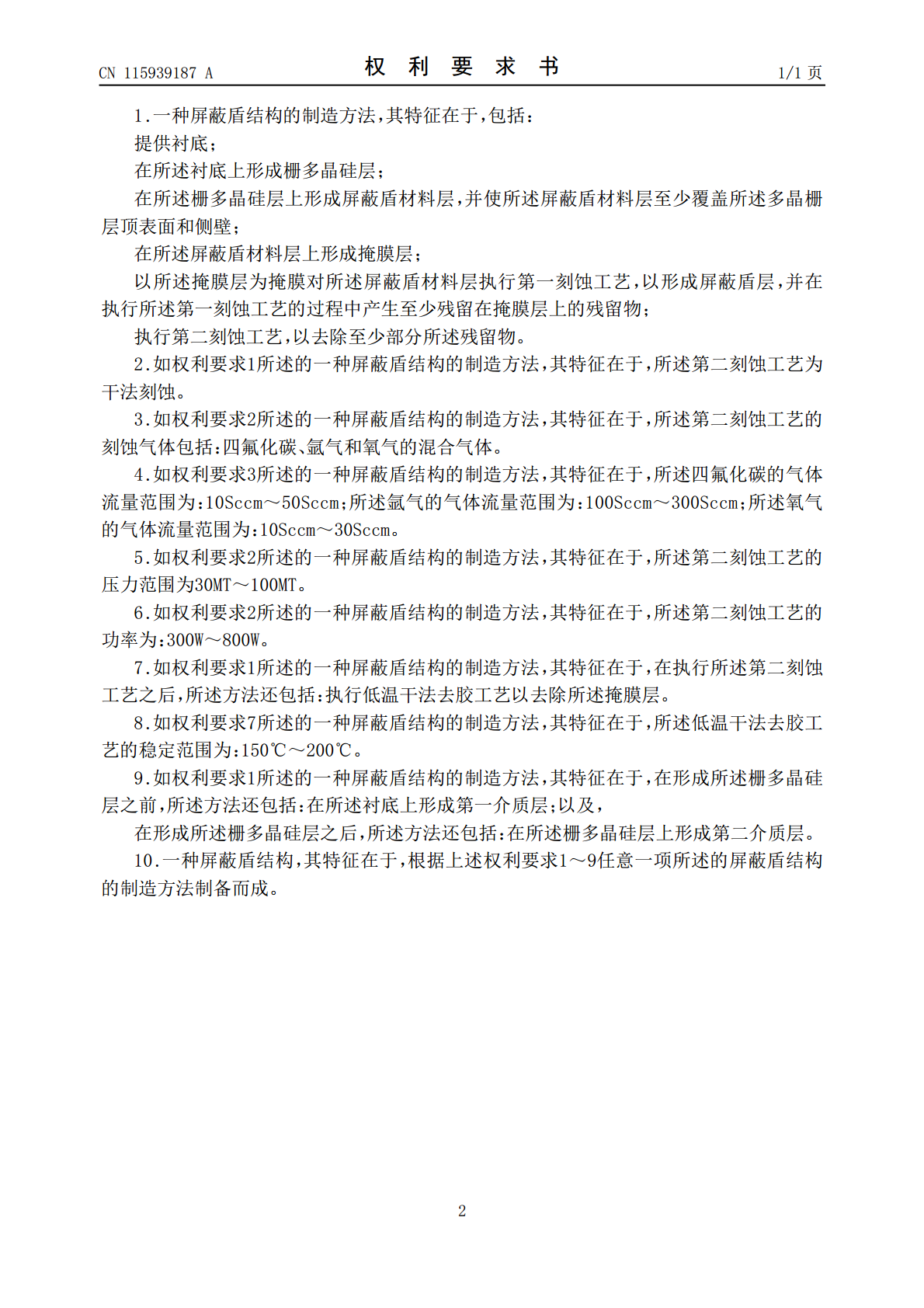

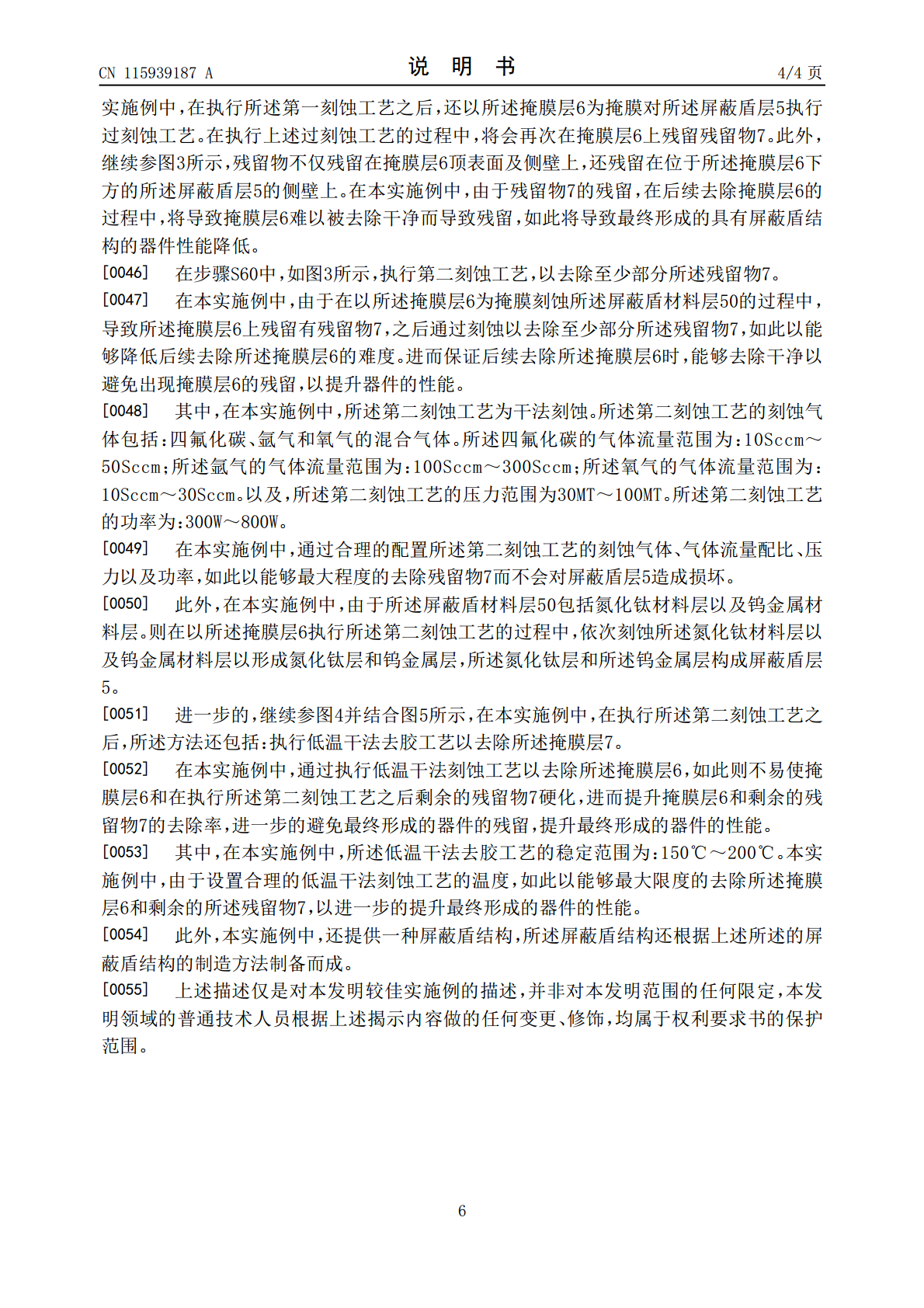

本发明提供一种屏蔽盾结构及其制造方法,由于在以所述掩膜层为掩膜刻蚀所述屏蔽盾材料层的过程中,导致所述掩膜层上残留有残留物,之后通过刻蚀以去除至少部分所述残留物,如此以能够降低后续去除所述掩膜层的难度。进而保证后续去除所述掩膜层时,能够去除干净以避免出现掩膜层的残留,以提升器件的性能。

ONO屏蔽栅的SGT结构及其制造方法.pdf

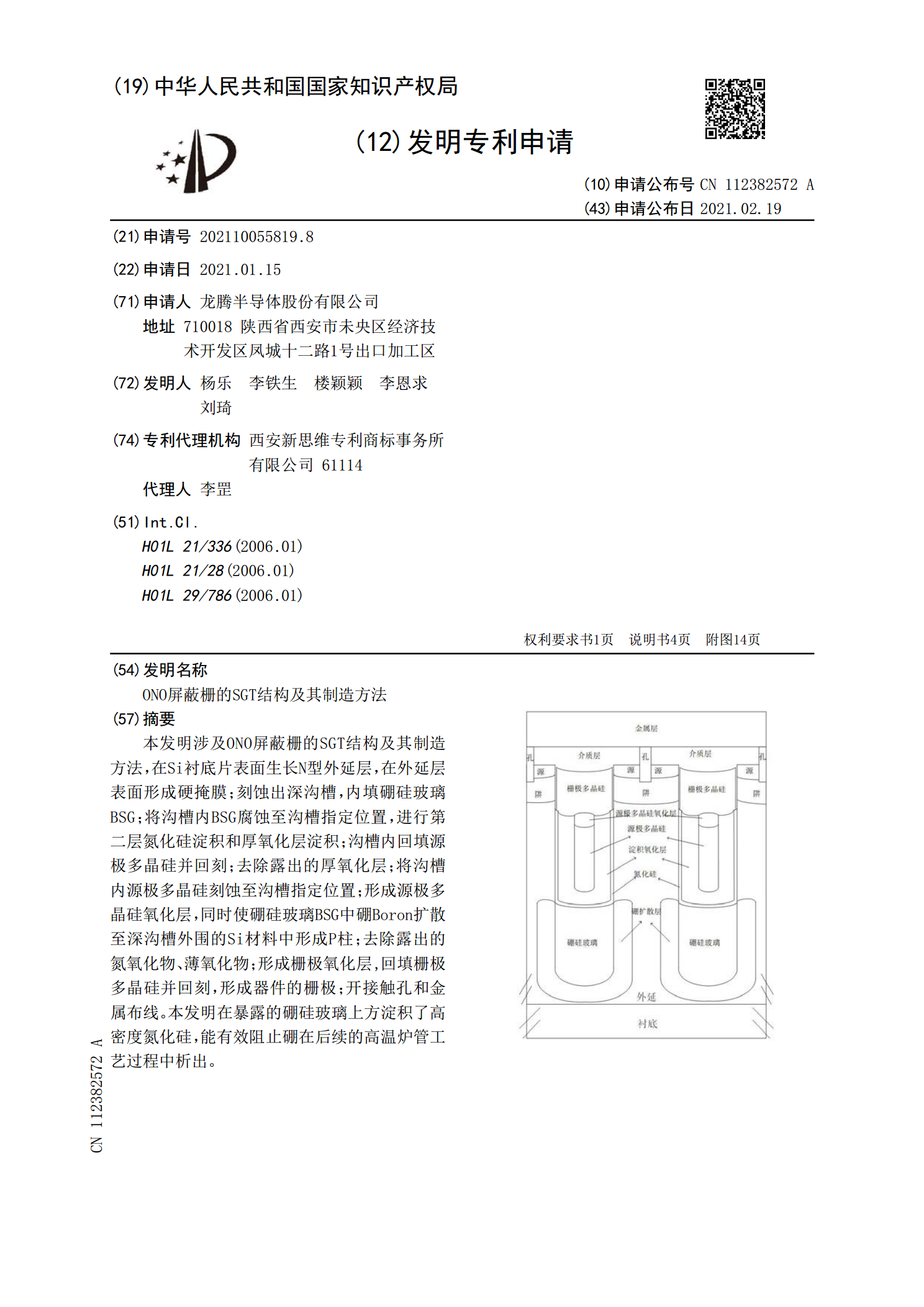

本发明涉及ONO屏蔽栅的SGT结构及其制造方法,在Si衬底片表面生长N型外延层,在外延层表面形成硬掩膜;刻蚀出深沟槽,内填硼硅玻璃BSG;将沟槽内BSG腐蚀至沟槽指定位置,进行第二层氮化硅淀积和厚氧化层淀积;沟槽内回填源极多晶硅并回刻;去除露出的厚氧化层;将沟槽内源极多晶硅刻蚀至沟槽指定位置;形成源极多晶硅氧化层,同时使硼硅玻璃BSG中硼Boron扩散至深沟槽外围的Si材料中形成P柱;去除露出的氮氧化物、薄氧化物;形成栅极氧化层,回填栅极多晶硅并回刻,形成器件的栅极;开接触孔和金属布线。本发明在暴露的硼硅

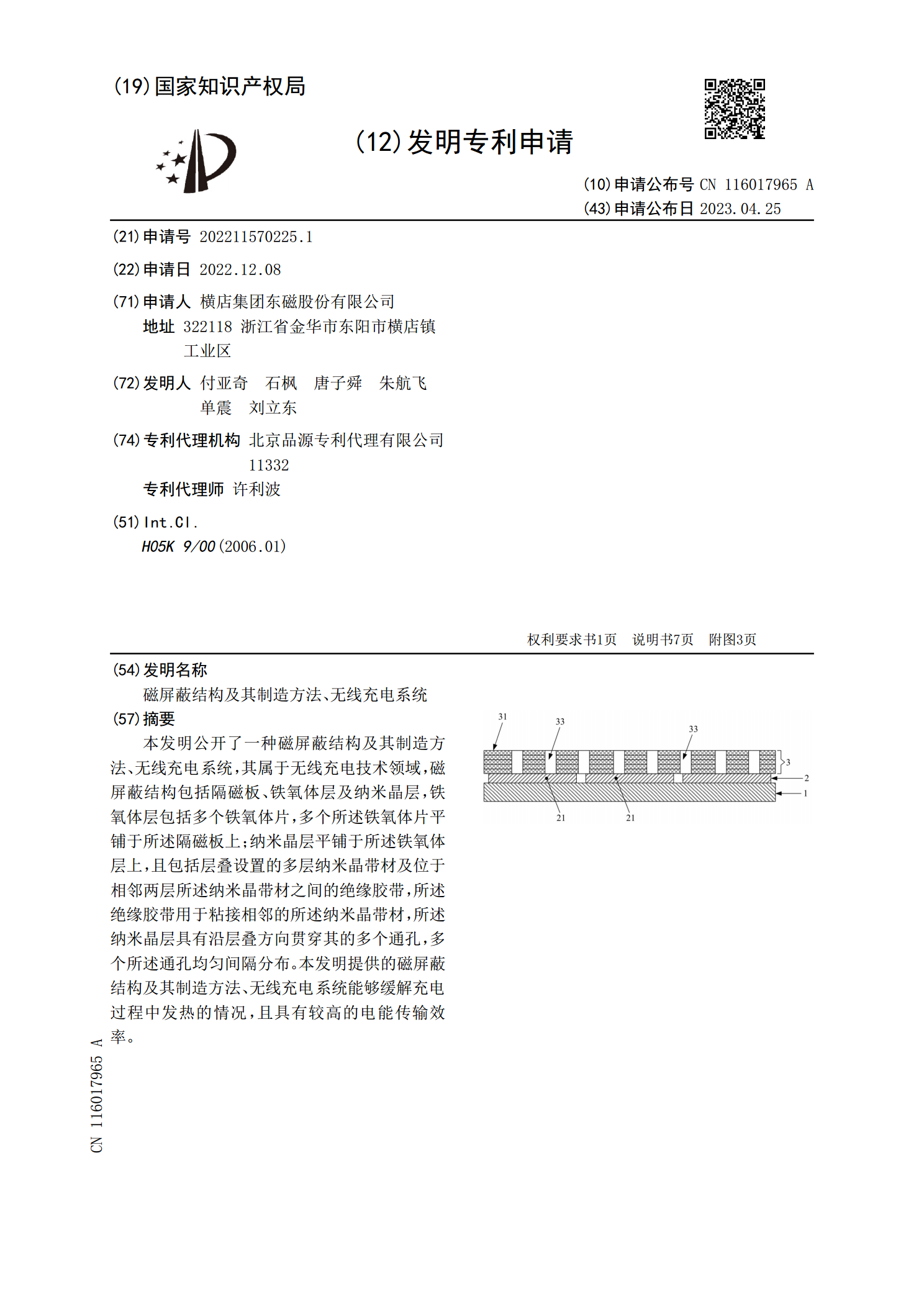

磁屏蔽结构及其制造方法、无线充电系统.pdf

本发明公开了一种磁屏蔽结构及其制造方法、无线充电系统,其属于无线充电技术领域,磁屏蔽结构包括隔磁板、铁氧体层及纳米晶层,铁氧体层包括多个铁氧体片,多个所述铁氧体片平铺于所述隔磁板上;纳米晶层平铺于所述铁氧体层上,且包括层叠设置的多层纳米晶带材及位于相邻两层所述纳米晶带材之间的绝缘胶带,所述绝缘胶带用于粘接相邻的所述纳米晶带材,所述纳米晶层具有沿层叠方向贯穿其的多个通孔,多个所述通孔均匀间隔分布。本发明提供的磁屏蔽结构及其制造方法、无线充电系统能够缓解充电过程中发热的情况,且具有较高的电能传输效率。

带有屏蔽结构的晶体管、封装器件及其制造方法.pdf

本公开涉及带有屏蔽结构的晶体管、封装器件及其制造方法。晶体管包括具有内部有源器件、第一端和第二端的半导体基板。所述晶体管还包括在所述半导体基板上由介电材料和导电材料的层形成的互连结构。所述互连结构包括由所述导电材料形成并且延伸通过所述介电材料的导柱、分接互连件和安置在所述导柱和所述分接互连件之间的屏蔽结构。所述导柱接触所述第一端并且连接到第一流道。所述分接互连件接触所述第二端并且连接到第二流道。所述屏蔽结构包括基部段、从所述基部段的相对末端延伸的第一支腿和第二支腿,其中所述第一和第二支腿在反向平行于所述基

具有屏蔽栅沟槽结构的半导体器件及其制造方法.pdf

本发明提供了一种具有屏蔽栅沟槽的半导体器件及其制造方法,在回刻蚀场氧化层以形成核心区的屏蔽氧化层之后,且在通过热氧化工艺一步形成核心区屏蔽栅上方的栅间氧化层和栅氧化层之前,先通过平坦化工艺或者回刻蚀工艺来降低终端区的沟槽中的缝隙深度,由此在后续形成核心区的多晶硅栅的工艺中能避免在终端区的沟槽中产生的多晶硅残留,有效解决终端区器件的CP参数失效问题,保证半导体器件的性能。