一种半导体元件的制备方法及半导体元件.pdf

森林****来了

亲,该文档总共22页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种半导体元件的制备方法及半导体元件.pdf

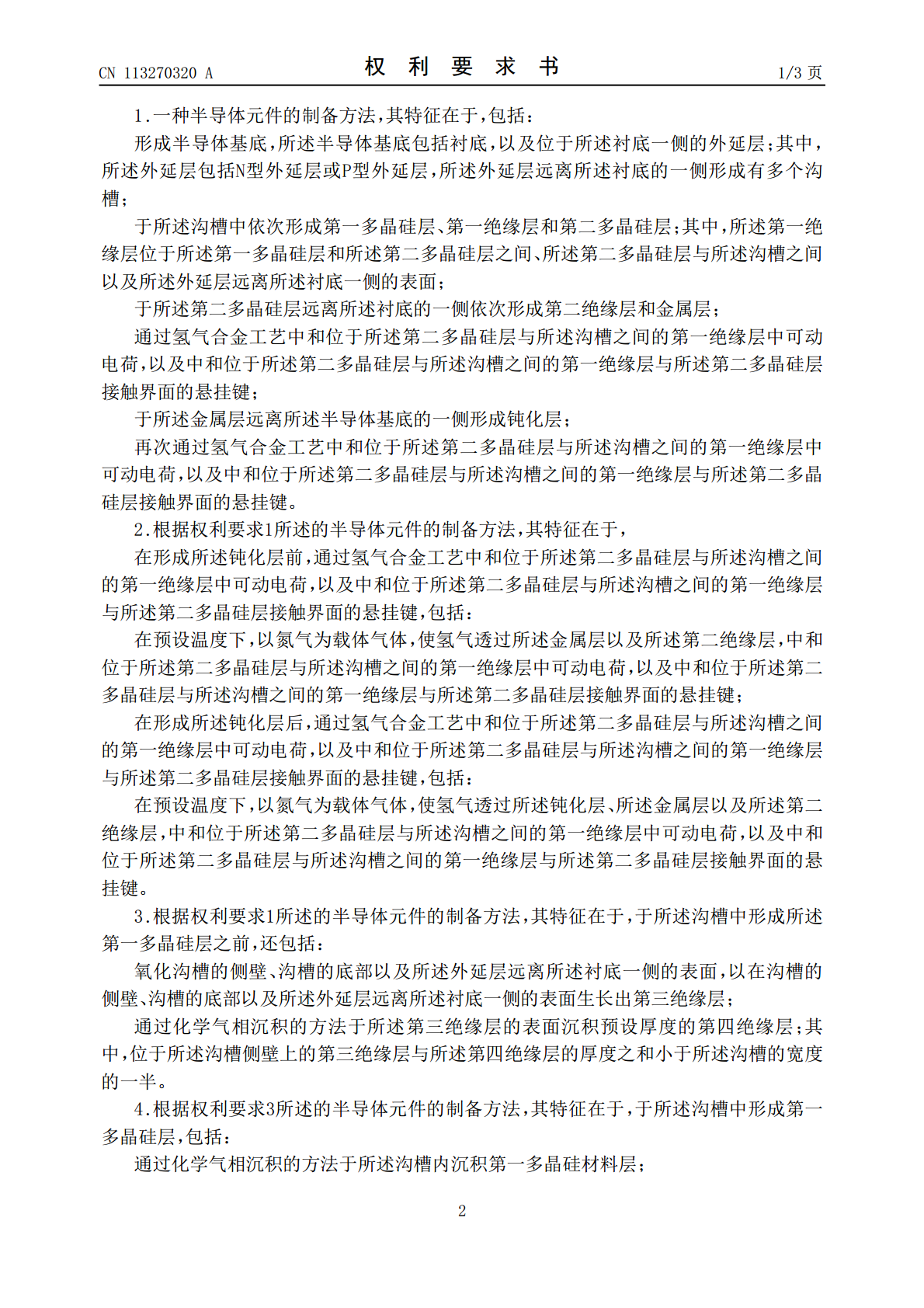

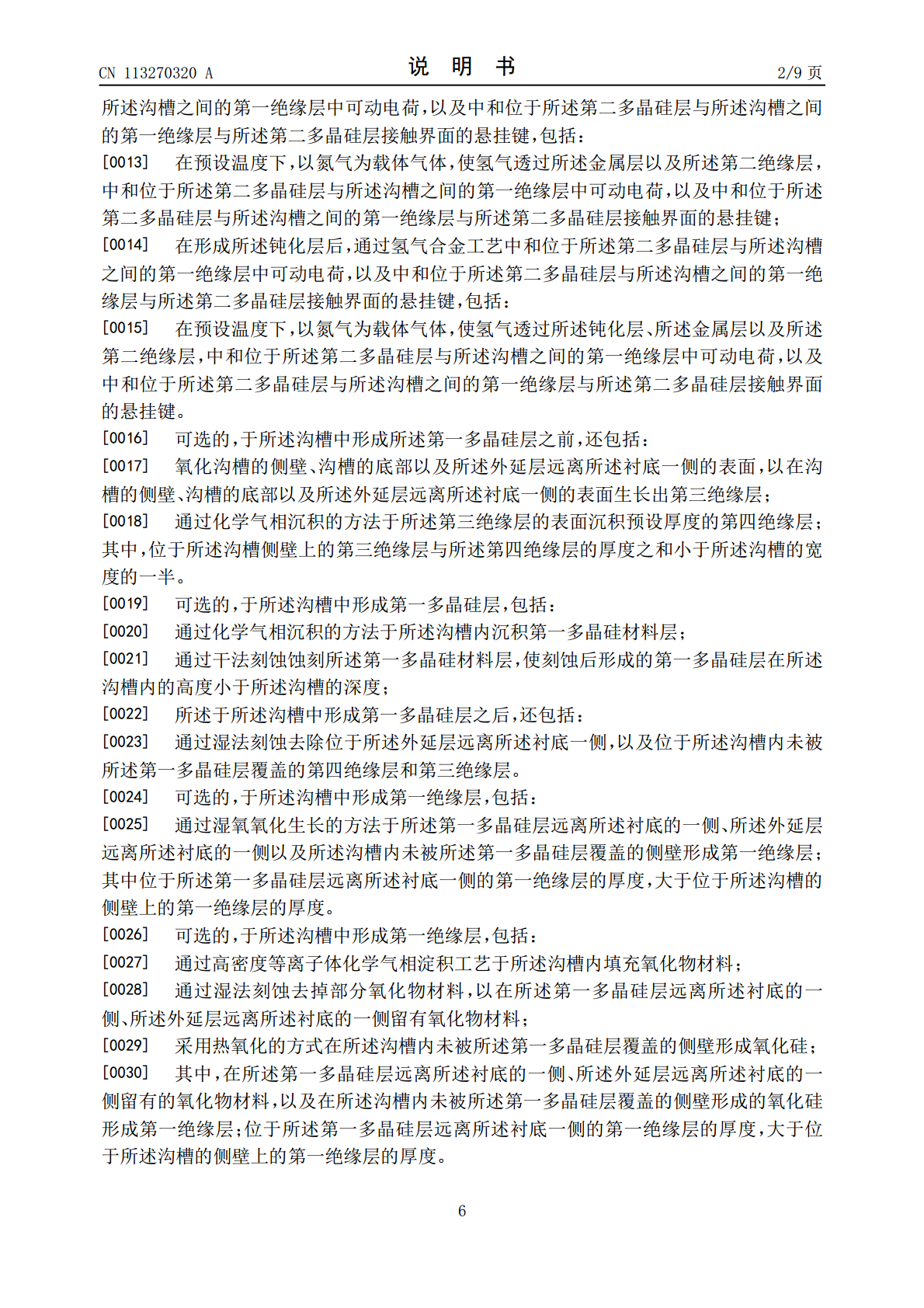

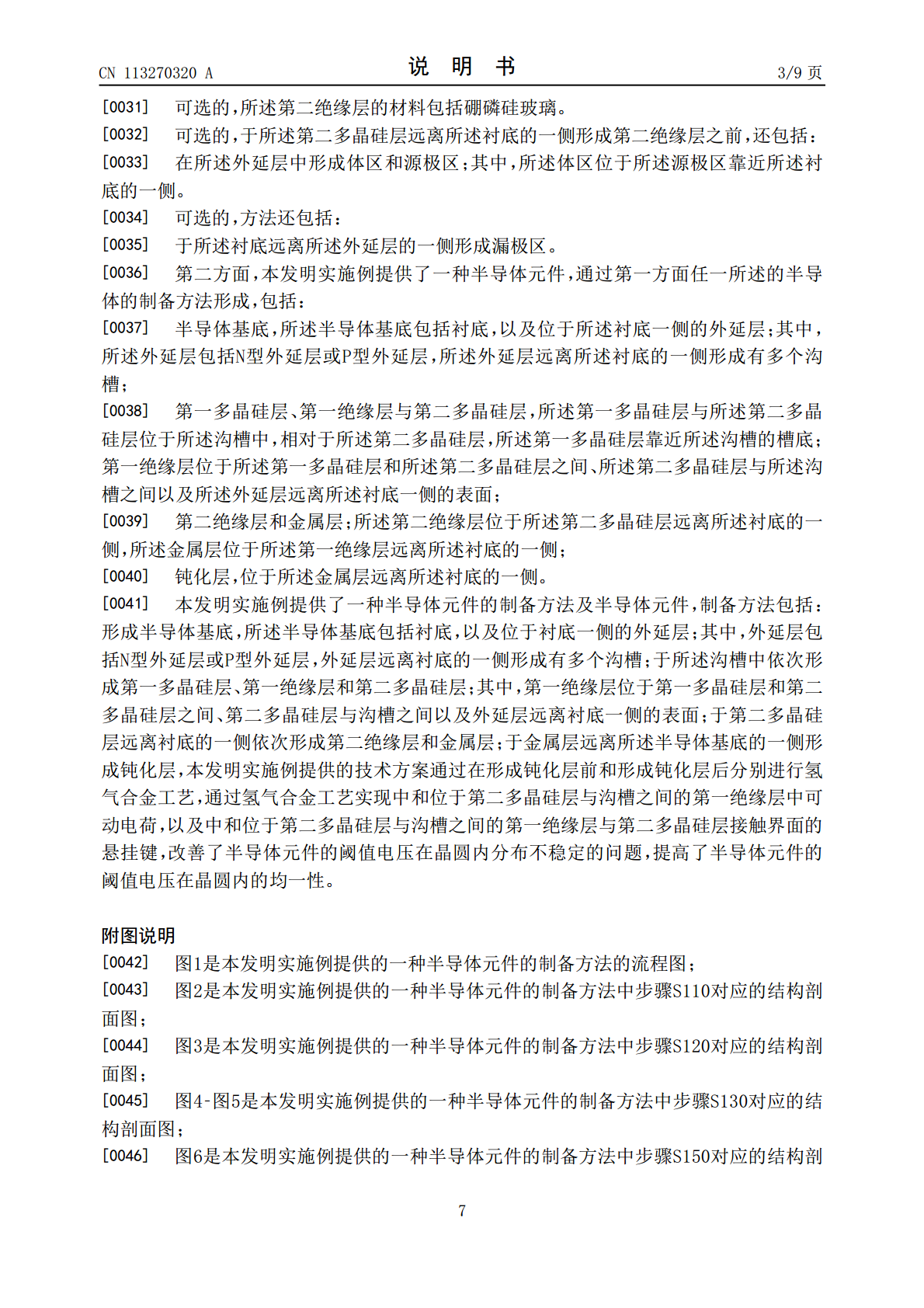

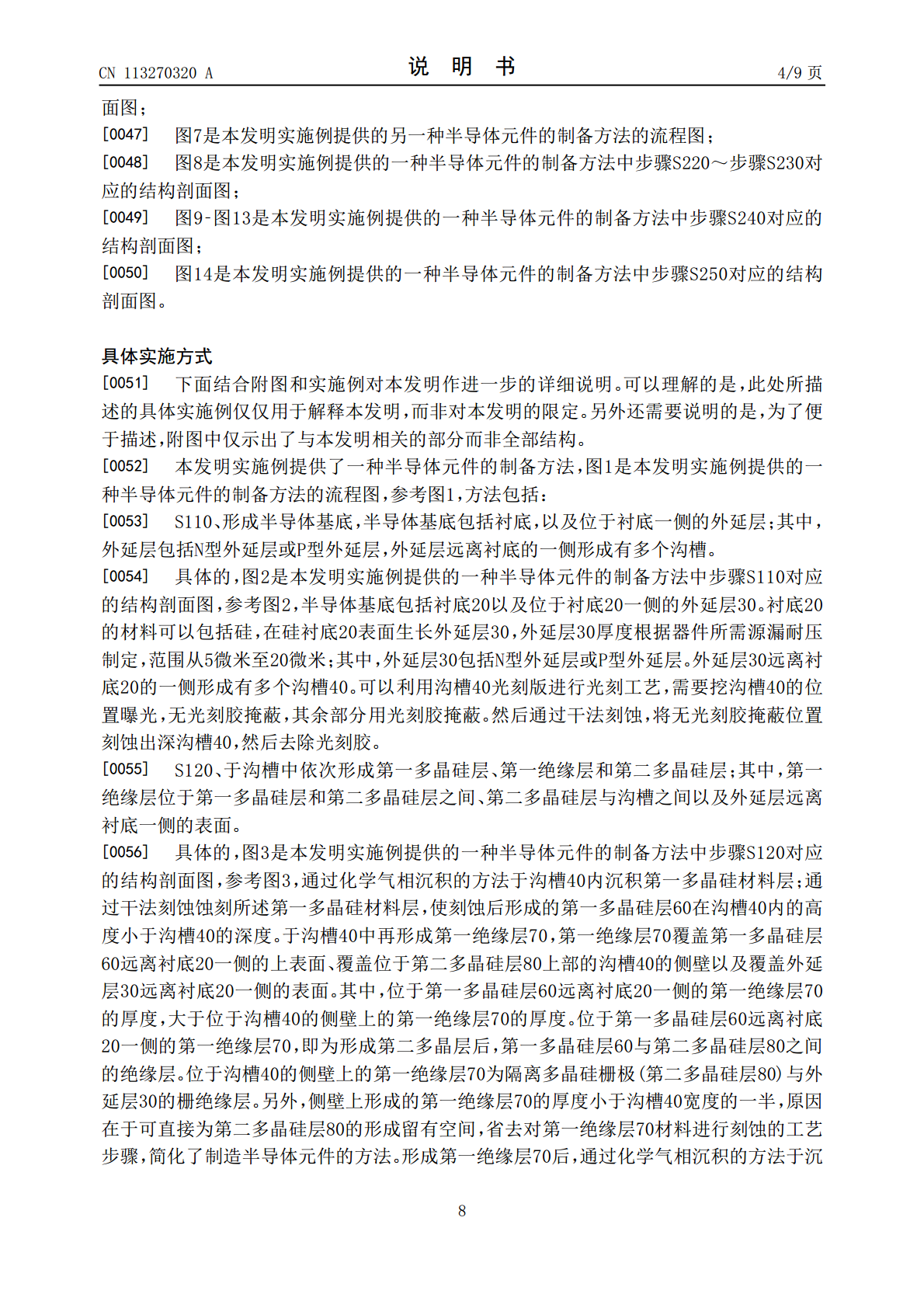

本发明实施例公开了一种半导体元件的制备方法及半导体元件,制备方法包括:形成半导体基底,半导体基底包括衬底,以及位于衬底一侧的外延层;外延层远离衬底的一侧形成有多个沟槽;于沟槽中依次形成第一多晶硅层、第一绝缘层和第二多晶硅层;其中,第一绝缘层位于第一多晶硅层和第二多晶硅层之间、第二多晶硅层与沟槽之间以及外延层远离衬底一侧的表面;于第二多晶硅层远离衬底的一侧依次形成第二绝缘层和金属层;于金属层远离所述半导体基底的一侧形成钝化层,并且在形成钝化层前后分别通过氢气合金工艺中和位于第二多晶硅层与沟槽之间的第一绝缘层

半导体元件的制备方法.pdf

本公开提供一种半导体元件的制备方法。该半导体元件的制备方法包括提供一目标层;形成一第一硬遮罩层在该目标层上;形成多个第二硬遮罩层在该第一硬遮罩层上;执行一第一倾斜蚀刻制程在该第一硬遮罩层上,以形成多个第一开口在沿着该第一硬遮罩并邻近所述第二硬遮罩层的各第一侧处;以及执行一第二倾斜蚀刻制程在该第一硬遮罩层上,以形成多个第二开口在沿着该第一硬遮罩层并邻近所述第二硬遮罩层的各第二侧处。该第一倾斜蚀刻制程与该第二倾斜蚀刻制程使用所述第二硬遮罩层当作图案引导件,且该第一硬遮罩层通过所述第一开口与所述第二开口而转变成

一种半导体元件及其制备方法.pdf

本发明提出了一种半导体元件,通过利用衬底上生长的金属保护层、金属氧化物保护层避免硅衬底表面非晶态层的形成;利用过渡层减小所述金属氧化物保护层与所述III-IV族缓冲层的晶格差异,提高所述III-IV族缓冲层的晶体质量。本发明同时提出一种制备方法,该方法可以避免在硅衬底界面附近非晶态层的形成,避免裂纹的产生。同时充分利用PVD法沉积的高质量多层缓冲结构,及在其上生长氮化镓或铟镓氮或铝镓氮外延层,制作成发光二极管元件或晶体管元件。

半导体元件及半导体元件的制造方法.pdf

本发明提供一种晶格匹配的HEMT元件,其是将二维电子气浓度确保在实用的范围内且反向耐压高的HEMT元件。通过在将AlN模板基板或Si单晶基体材料作为基底的基板等的基底基板上,形成由GaN而成的沟道层,并且在该沟道层上,形成由InxAlyGazN(x+y+z=1,0≦z≦0.3)组分的III族氮化物而成的势垒层,而且在该势垒层上形成源极电极、漏极电极、及栅极电极,从而制备半导体元件,此时,势垒层的In摩尔分数(x)和Ga摩尔分数(z)和厚度(d)满足规定的范围。

半导体元件的制备方法.pdf

本发明关于一种半导体元件的制备方法,其包括步骤:步骤一:应用传统的工艺流程制备多晶硅栅极并沉积适当厚度的层间介质层(ILD,Interlayer?Dielectric);该多晶硅栅极具有位于下层的浮栅(FG,Floating?Gate)、中间层的氧化物-氮化物-氧化物(ONO)及位于上层的控制栅(CG,Control?Gate);步骤二:利用化学机械抛光将层间介质层ILD磨平并停止在CG多晶硅表面;步骤三:使用对OXIDE选择比很高的湿法刻蚀方法将CG多晶硅完全去除;步骤四:在除去了CG多晶硅的晶圆上沉积