半导体元件及半导体元件的制造方法.pdf

一吃****仪凡

亲,该文档总共29页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体元件及半导体元件的制造方法.pdf

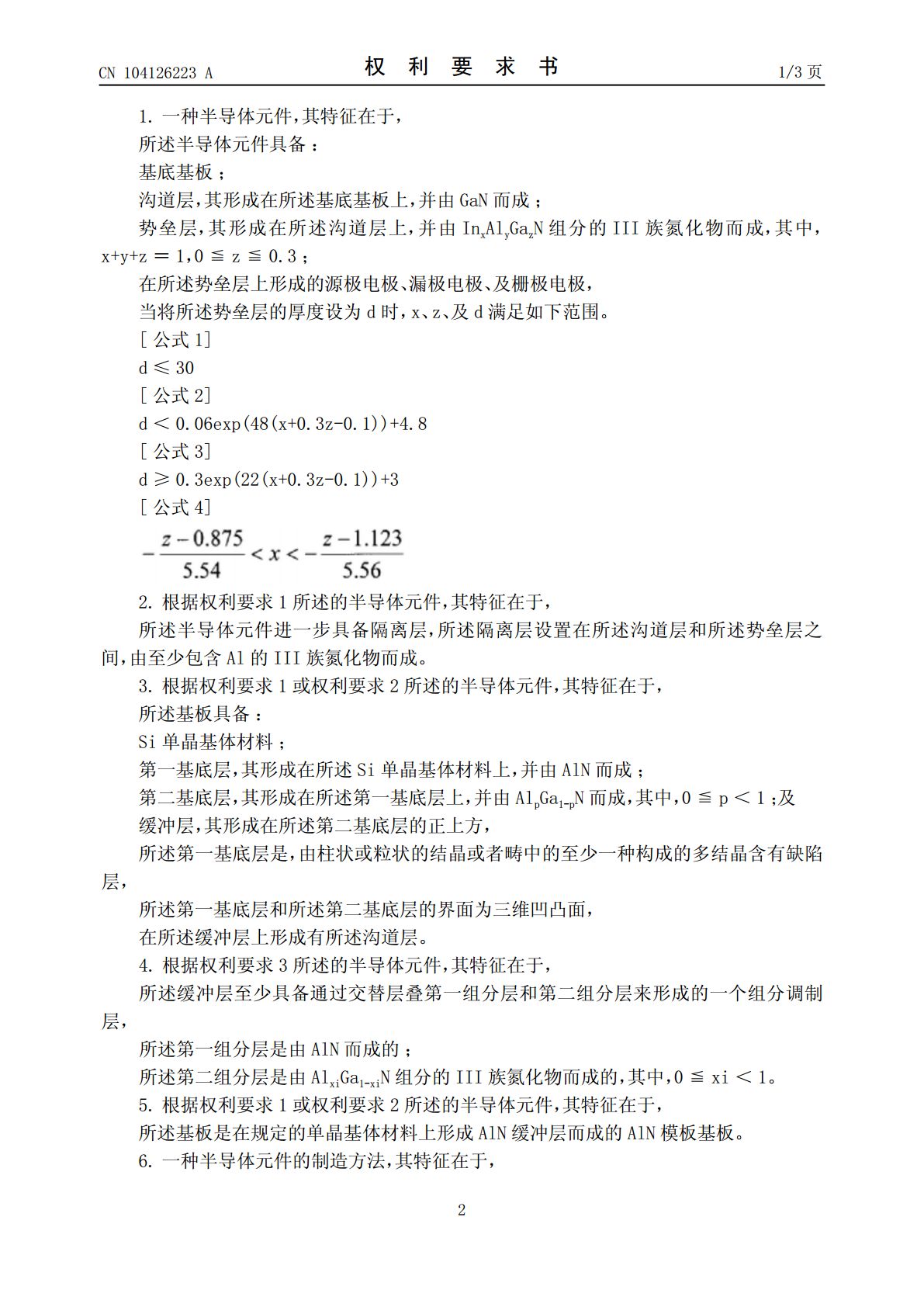

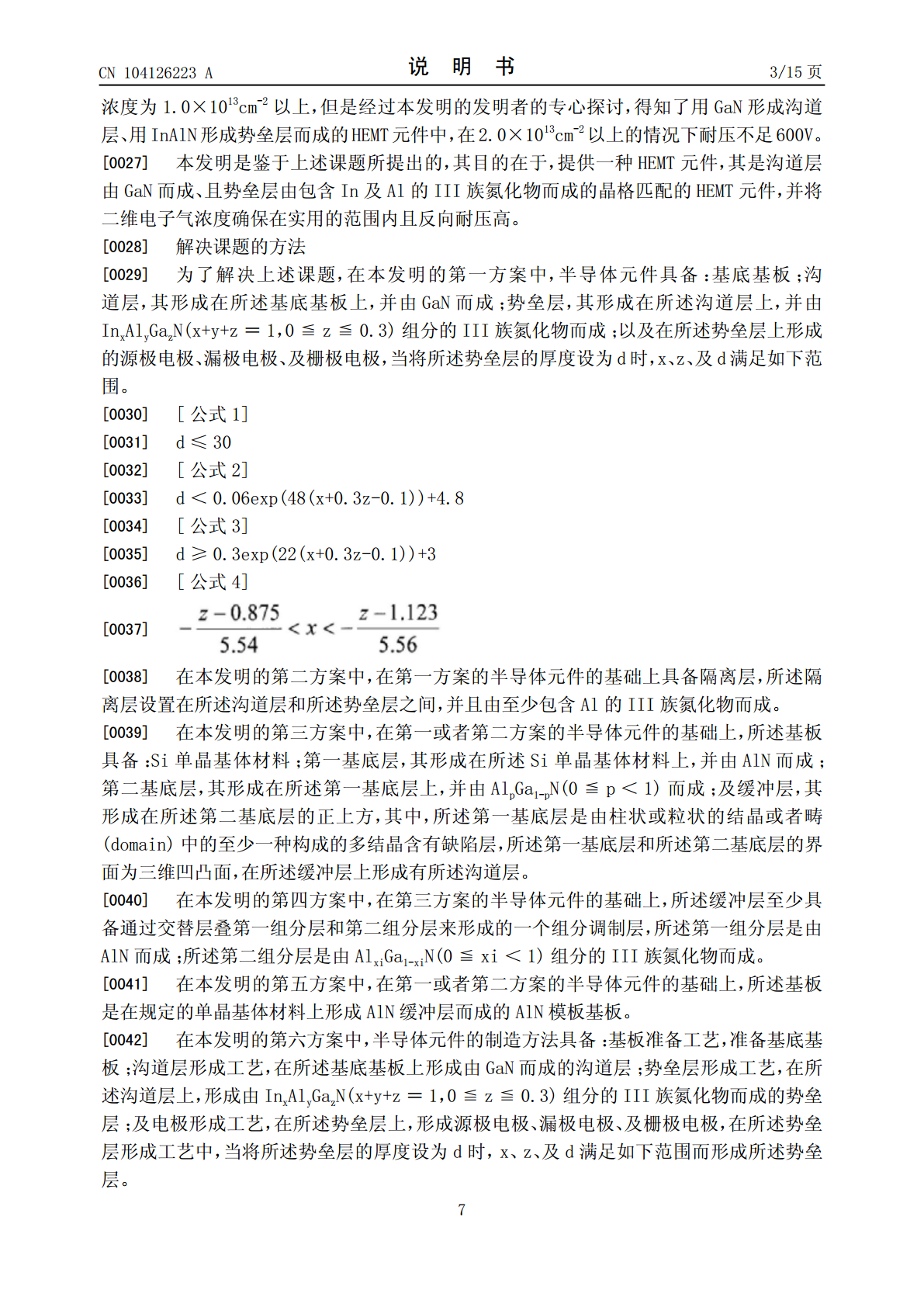

本发明提供一种晶格匹配的HEMT元件,其是将二维电子气浓度确保在实用的范围内且反向耐压高的HEMT元件。通过在将AlN模板基板或Si单晶基体材料作为基底的基板等的基底基板上,形成由GaN而成的沟道层,并且在该沟道层上,形成由InxAlyGazN(x+y+z=1,0≦z≦0.3)组分的III族氮化物而成的势垒层,而且在该势垒层上形成源极电极、漏极电极、及栅极电极,从而制备半导体元件,此时,势垒层的In摩尔分数(x)和Ga摩尔分数(z)和厚度(d)满足规定的范围。

半导体元件制造方法.pdf

本发明公开了一种半导体元件制造方法,其包含在基板上的第一区域形成第一图案层,在第一图案层与基板上形成旋涂材料层,在旋涂材料层上形成蚀刻停止层,以及在蚀刻停止层上形成第一遮罩层。在不同段的蚀刻程序中进行蚀刻时,蚀刻停止层可以调整遮罩图案层的侧边,提升了半导体元件上图案的精细度以及蚀刻轮廓的品质。

半导体元件制造方法.pdf

本发明公开一种半导体元件制造方法,首先,提供具有第一晶体管结构与第二晶体管结构的基板。其中,第一晶体管结构具有第一栅极沟槽,第二晶体管结构具有第二栅极沟槽。接着,在第一栅极沟槽与第二栅极沟槽中形成第一功函数金属层,并于第一功函数金属层上形成平坦层。之后,在平坦层上形成图案化光致抗蚀剂层,再蚀刻部分位于第二晶体管结构上的平坦层。接着,去除图案化光致抗蚀剂层之后,全面蚀刻平坦层直至完全去除位于第二晶体管结构上的平坦层,而保留图案化平坦层覆盖住第一晶体管结构。最后,去除位于第二栅极沟槽中的第一功函数金属层。

光半导体元件的制造方法及光半导体元件.pdf

包括:在半导体基板上依次堆积活性层、包层及接触层的工序;对所述层进行蚀刻而形成台面结构的工序;形成绝缘膜而将台面结构覆盖的工序;将绝缘膜的膜厚减少至接触层的上表面露出为止,将残留的绝缘膜作为侧壁的工序;形成电介质树脂层而埋入台面结构及侧壁的工序;对电介质树脂层选择性地进行蚀刻而形成开口部,使接触层的上表面露出的工序;在开口部内形成电极的工序。

半导体元件的制造方法及半导体元件.pdf

本发明的目的在于通过将半导体磊晶层接合于其他基板而使制造半导体元件的方法效率化。本发明的半导体元件的制造方法包括:形成作为薄膜的固定层的步骤,所述固定层将半导体薄膜层的与母材基板一侧为相反侧的主面的至少一部分与母材基板中的半导体薄膜层一侧的面的至少一部分结合;通过将半导体薄膜层或母材基板的一部分区域去除而形成空隙的步骤;在形成空隙后,在半导体薄膜层的主面将形成于拾取基板的有机材料层与固定层结合的步骤;在有机材料层结合于固定层的状态下将拾取基板沿与母材基板相离的方向移动,由此将半导体薄膜层自第一基板分离的步