组合逻辑电路与时序逻辑电路(课堂PPT).ppt

和蔼****娘子

亲,该文档总共94页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

组合逻辑电路与时序逻辑电路(课堂PPT).ppt

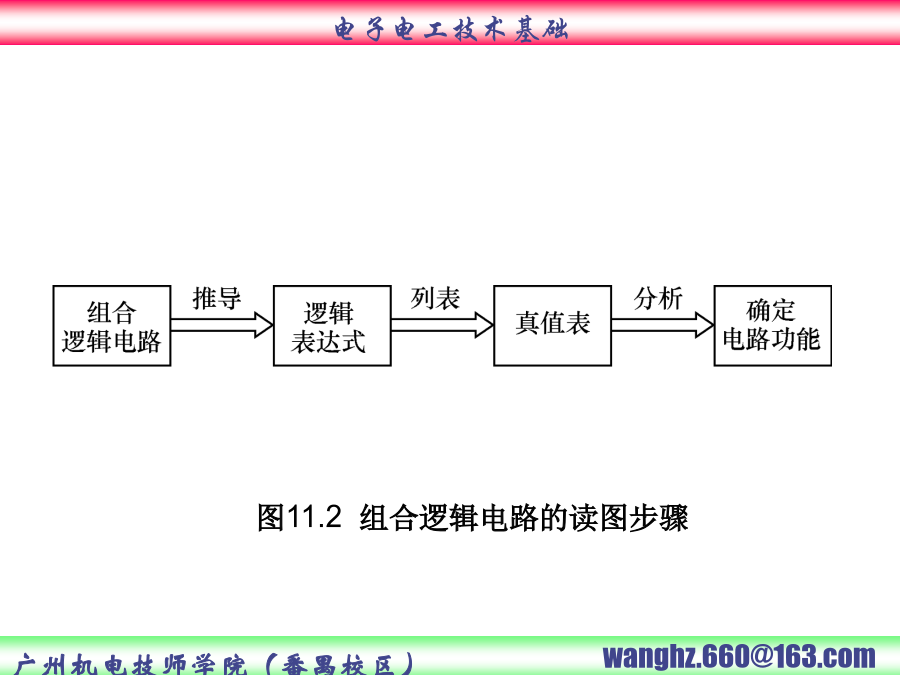

第11章组合逻辑电路与时序逻辑电路知识目标●理解组合逻辑电路的读图方法和步骤。●了解典型编码、译码集成电路的引脚功能,会根据功能表正确使用。●了解半导体数码管的基本结构和工作原理。●熟悉RS触发器、JK触发器、D触发器的逻辑功能。●了解集成移位寄存器的基本功能和应用。●掌握典型计数集成电路的引脚功能和应用常识。技能目标●会用编码、译码集成电路组装应用电路。●会对RS触发器、JK触发器、D触发器进行逻辑功能的检测。●能用典型计数集成电路装配计数功能电路。11.1组合逻辑电路11.1.1组合逻辑电路的读图方法

组合逻辑电路与时序逻辑电路.pptx

会计学知识目标●理解组合逻辑电路的读图方法和步骤。●了解典型编码、译码集成电路的引脚功能,会根据功能表正确使用。●了解半导体数码管的基本结构和工作原理。●熟悉RS触发器、JK触发器、D触发器的逻辑功能。●了解集成移位寄存器的基本功能和应用。●掌握典型计数集成电路的引脚功能和应用常识。技能目标●会用编码、译码集成电路组装应用电路。●会对RS触发器、JK触发器、D触发器进行逻辑功能的检测。●能用典型计数集成电路装配计数功能电路。11.1组合逻辑电路11.1.1组合逻辑电路的读图方法组合逻辑电路的读图步骤一般按

第十四章组合逻辑电路和时序逻辑电路.doc

个人收集整理勿做商业用途个人收集整理勿做商业用途个人收集整理勿做商业用途课 题第十四章 组合和时序逻辑电路第一节 集成门电路课型新课授课班级授课时数2教学目标1.了解TTL门电路的有关使用知识。2.了解CMOS门电路的有关使用知识。教学重点1.TTL门电路的有关使用知识。2.CMOS门电路的有关使用知识。教学难点TTL门电路和CMOS门电路的使用知识.学情分析教学效果教后记新课A、复习基本逻辑门电路的逻辑功能。B、新授课第一节 集成门电路用来实现基本逻辑关系的电子电路称为门电路.前一章介绍了与门、或门、

时序逻辑电路讲解ppt.pptx

时序逻辑电路讲解例置位二、同步RS触发器同步RS触发器的图形符号三、主从RS、JK触发器t110四、边沿JK、D触发器(1)SD–直接置位端,RD–直接清零端,通常用来设置触发器开始工作时得初始状态。不论J、K、C三端状态如何,只要SD=0、RD=1,就可使输出Q=1(置位);只要SD=1、RD=0,就可使输出Q=0(清零)。SD与RD均为低电平有效,在逻辑符号图中加‘o’表示。正常工作时SD=RD=1。由(1)与(2)得下降沿触发得JK触发器状态表如下。(1)JK触发器得特性方程D触发器状态表CPCP例

异步时序逻辑电路PPT资料.pptx

第六章异步时序(shíxù)逻辑电路异步时序逻辑电路中没有统一的时钟脉冲信号,电路状态的改变是外部输入信号变化直接作用的结果。根据电路结构和输入信号形式的不同,异步时序逻辑电路可分为(fēnwéi)脉冲异步时序逻辑电路和电平异步时序逻辑电路两种类型。两类电路均有Mealy型和Moore型两种结构模型。6.1.1概述二、输入(shūrù)信号的形式与约束三、输出(shūchū)信号的形式6.1.2脉冲异步时序(shíxù)逻辑电路的分析(4)用文字描述电路的逻辑功能(gōngnéng)(必要时画出时间图)。