异步时序逻辑电路PPT资料.pptx

天马****23

亲,该文档总共73页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

异步时序逻辑电路PPT资料.pptx

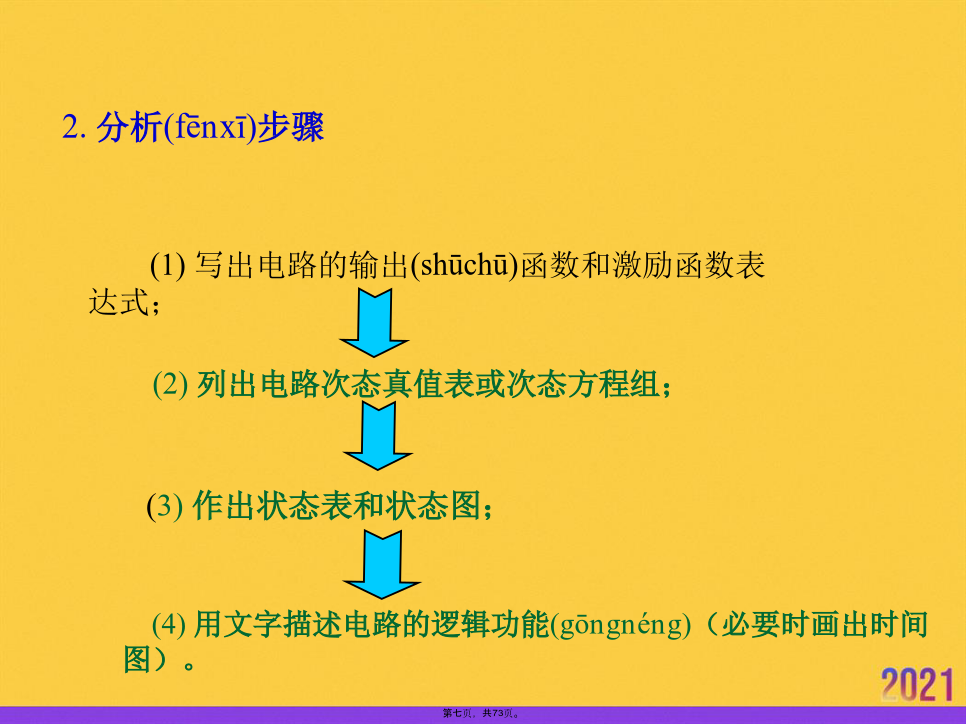

第六章异步时序(shíxù)逻辑电路异步时序逻辑电路中没有统一的时钟脉冲信号,电路状态的改变是外部输入信号变化直接作用的结果。根据电路结构和输入信号形式的不同,异步时序逻辑电路可分为(fēnwéi)脉冲异步时序逻辑电路和电平异步时序逻辑电路两种类型。两类电路均有Mealy型和Moore型两种结构模型。6.1.1概述二、输入(shūrù)信号的形式与约束三、输出(shūchū)信号的形式6.1.2脉冲异步时序(shíxù)逻辑电路的分析(4)用文字描述电路的逻辑功能(gōngnéng)(必要时画出时间图)。

异步时序逻辑电路.ppt

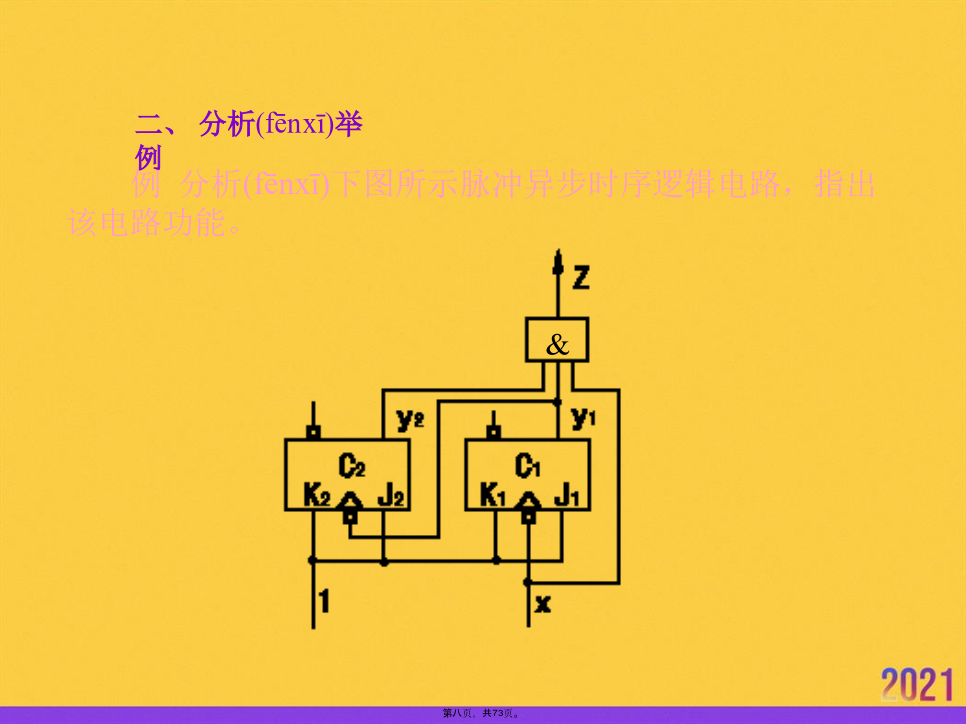

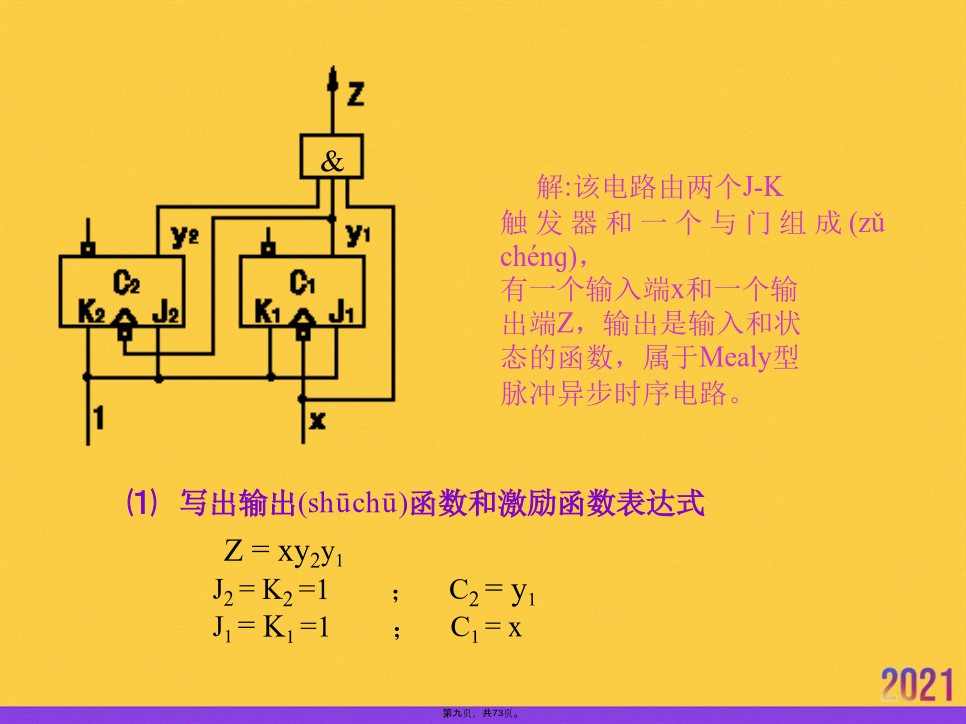

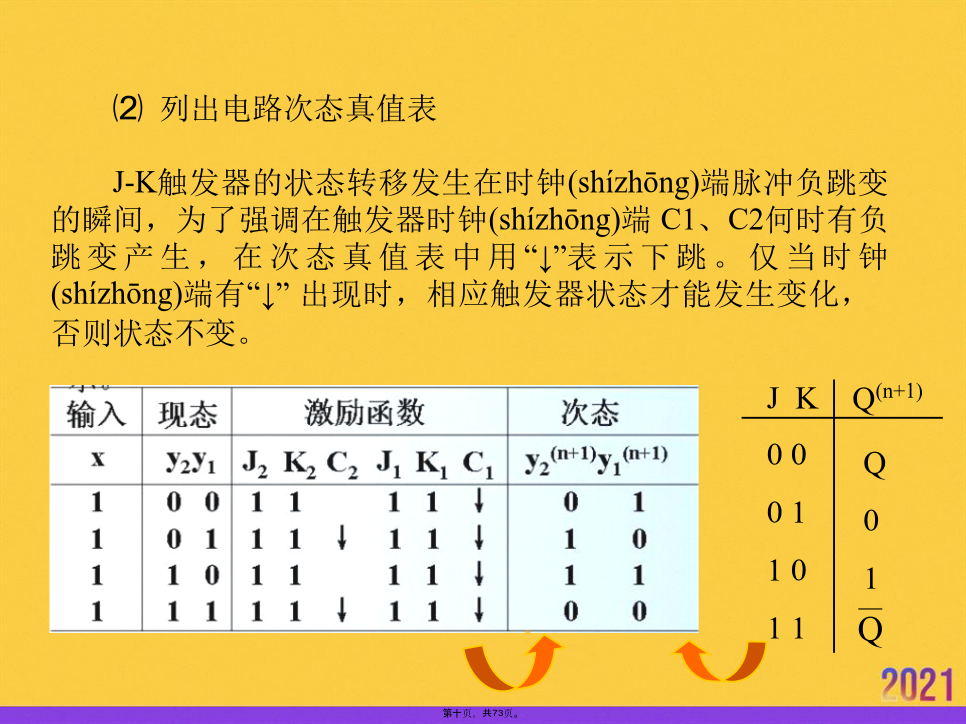

第五章异步时序逻辑电路5.1异步时序逻辑电路的特点及模型2.异步时序逻辑电路的特点组合逻辑5.2脉冲异步时序逻辑电路5.2.1脉冲异步时序逻辑电路的分析分析步骤如下:例:分析下图所示的脉冲异步时序逻辑电路解:现态y2y1作状态表和状态图:根据转移真值表可作出状态图.例:分析下图所示的脉冲异步时序逻辑电路作状态转移真值表现态y作状态表和状态图根据转移真值表可作出下列状态表和状态图画时间图和说明电路功能例:分析下图所示的脉冲异步时序电路解:该式表明当CP为逻辑1时,触发器的状态才能发生变化,而只有当时钟出现有

异步时序逻辑电路.ppt

异步时序逻辑电路脉冲异步时序逻辑电路脉冲异步时序逻辑电路的分析例分析图所示脉冲异步时序逻辑电路,指出电路功能。脉冲异步时序逻辑电路的设计D触发器激励表J-K触发器激励表T触发器R-S触发器激励表电平异步时序逻辑电路输入信号的约束电平异步时序电路的分析电平异步时序逻辑电路的竞争

53 异步时序逻辑电路的分析.docx

异步时序逻辑电路的分析一.分析的目的:得出时序电路的逻辑功能。二.分析的方法(步骤):1、写方程式:(1)时钟方程;(2)输出方程;(3)驱动方程;(4)状态方程。2、列状态表;3、画状态转换图;4、画时序图;5、逻辑功能说明;6、检查电路能否自启动。注意:异步时序电路的状态改变时,电路中要更新状态的触发器,有的先翻转,有的后翻转,是异步进行的。因为在这种时序电路中,有的触发器的信号就是输入时钟脉冲,有的触发器则不是,而是其他触发器的输出。异步时序电路的分析举例例1试分析图示的时序电路的逻辑功能。解:(1

物理异步时序逻辑电路学习教案.pptx

物理(wùlǐ)异步时序逻辑电路脉冲(màichōng)异步时序逻辑电路脉冲异步时序逻辑电路(luójídiànlù)的分析例分析图所示脉冲异步时序逻辑电路(luójídiànlù),指出电路功能。脉冲异步时序逻辑电路(luójídiànlù)的设计D触发器激励(jīlì)表J-K触发器激励(jīlì)表T触发器R-S触发器激励(jīlì)表电平异步时序(shíxù)逻辑电路输入(shūrù)信号的约束电平(diànpínɡ)异步时序电路的分析电平(diànpínɡ)异步时序逻辑电路的竞争