片内时钟网络延时测试方法和测试电路.pdf

慧红****ad

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

片内时钟网络延时测试方法和测试电路.pdf

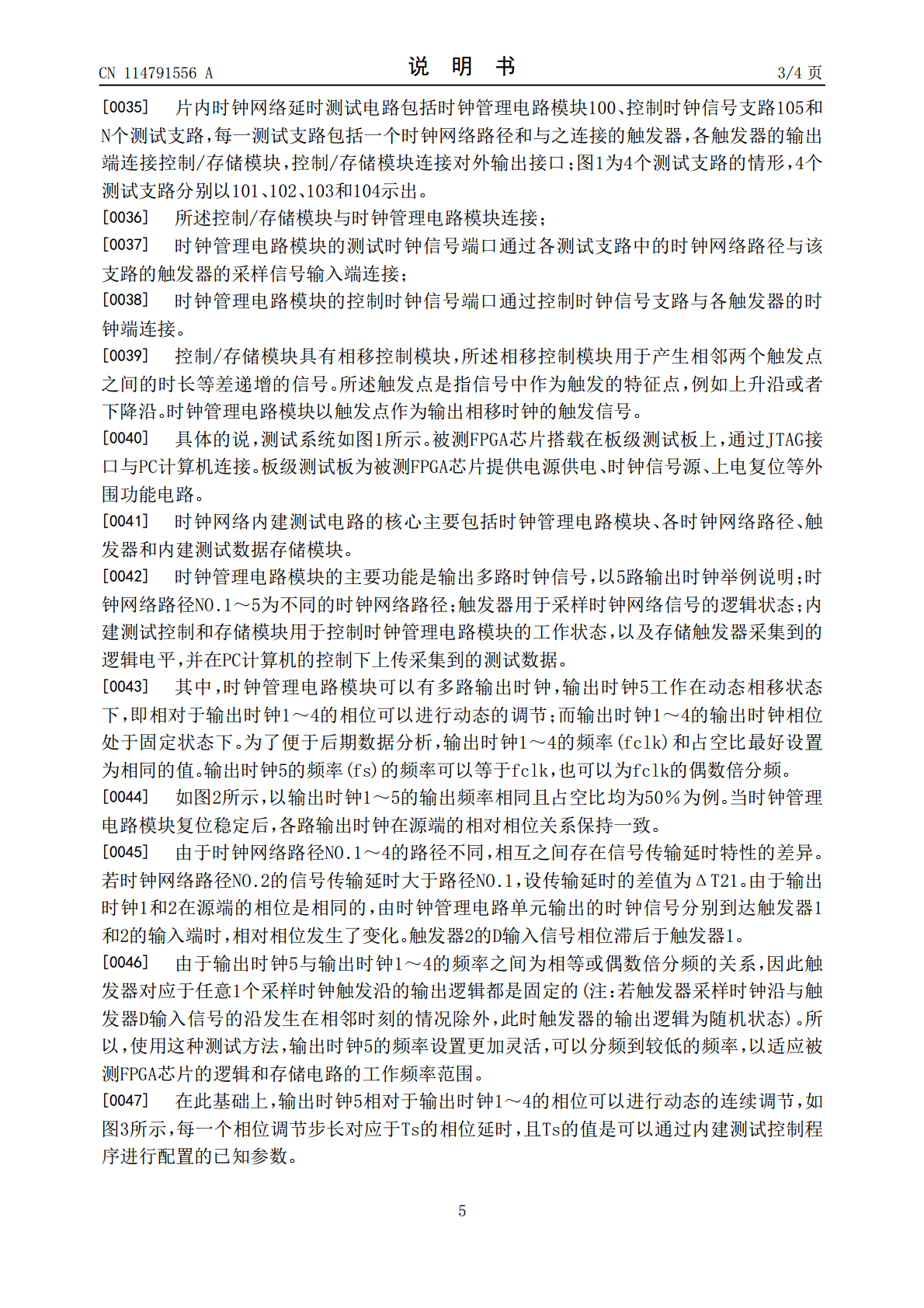

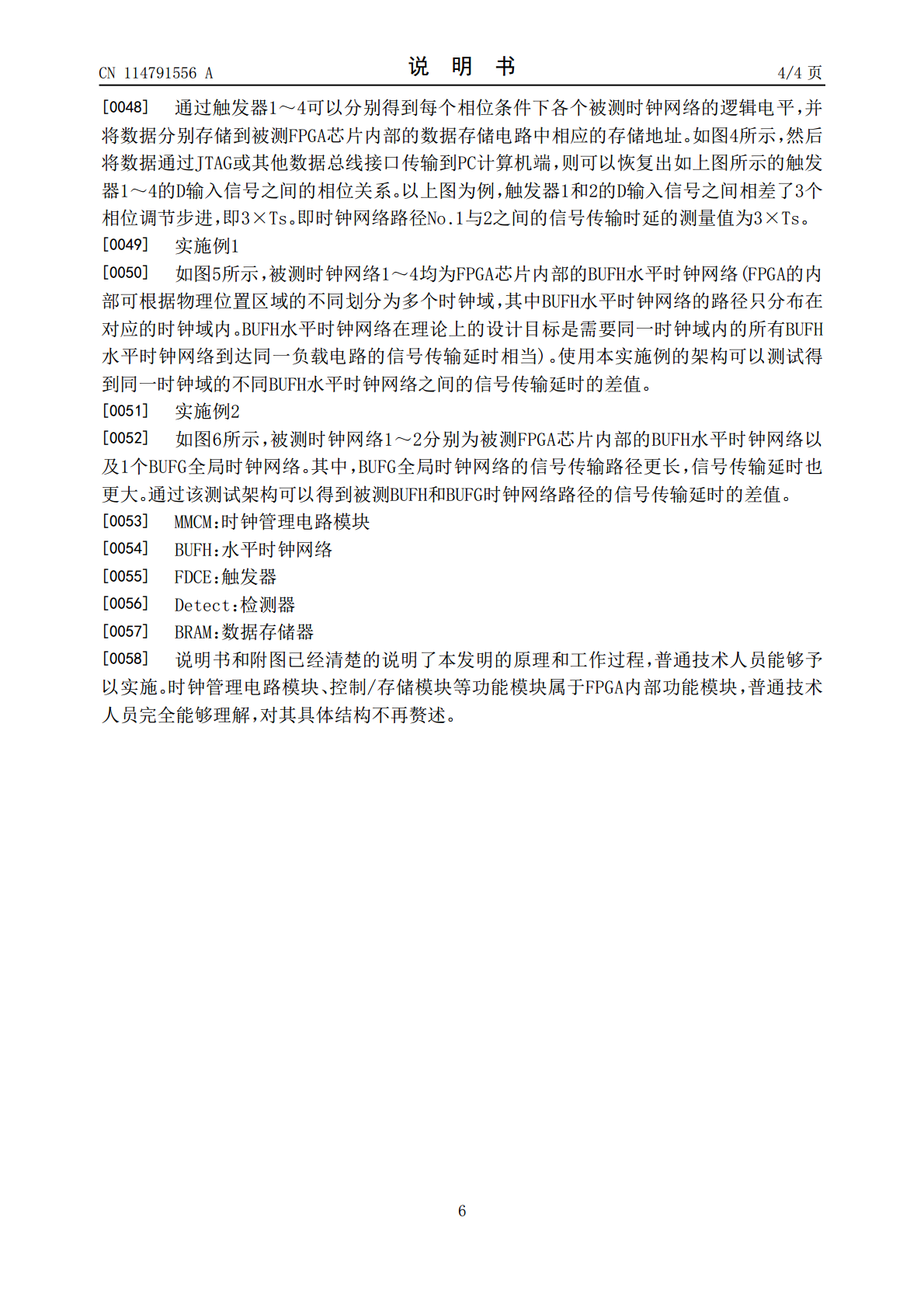

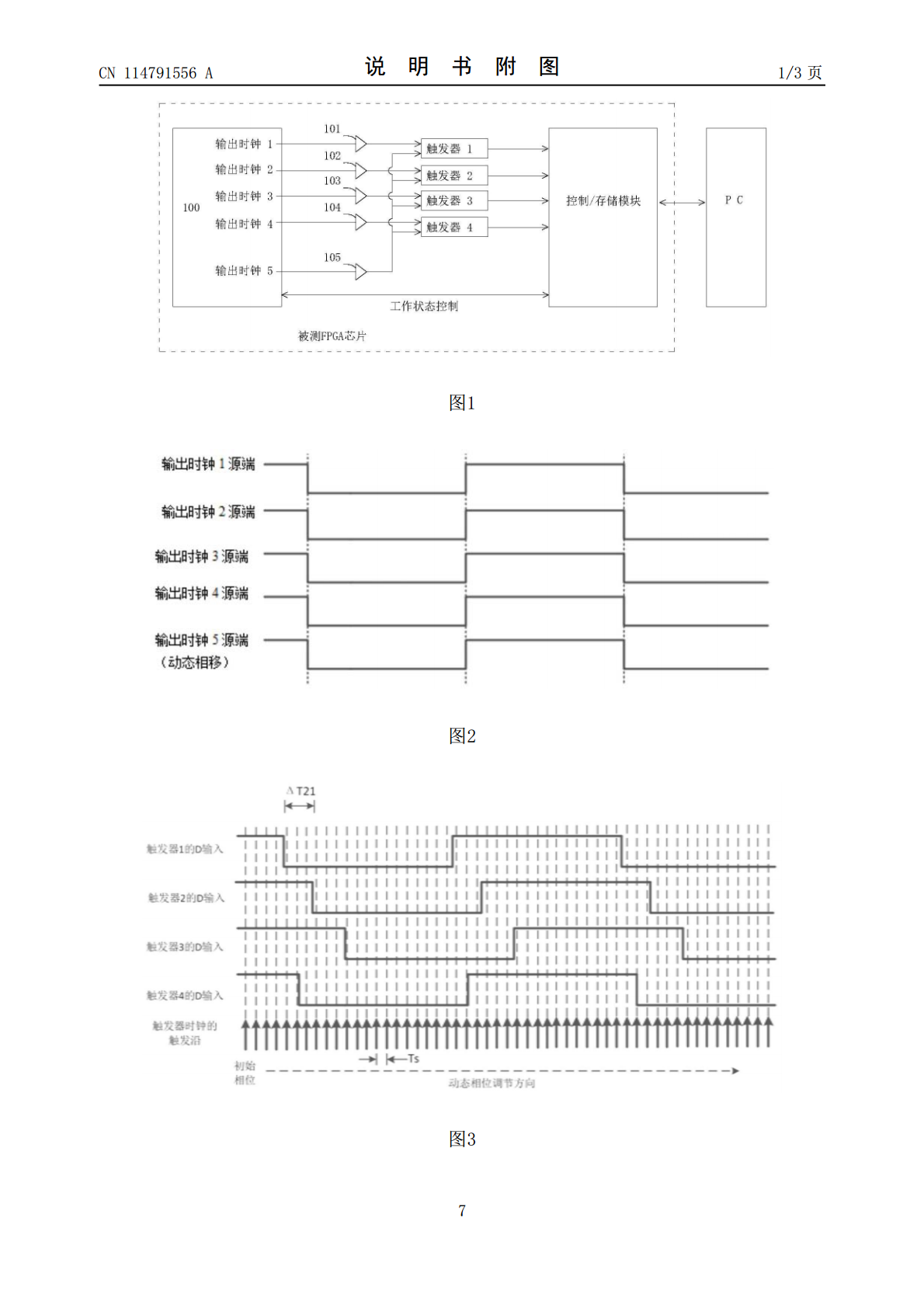

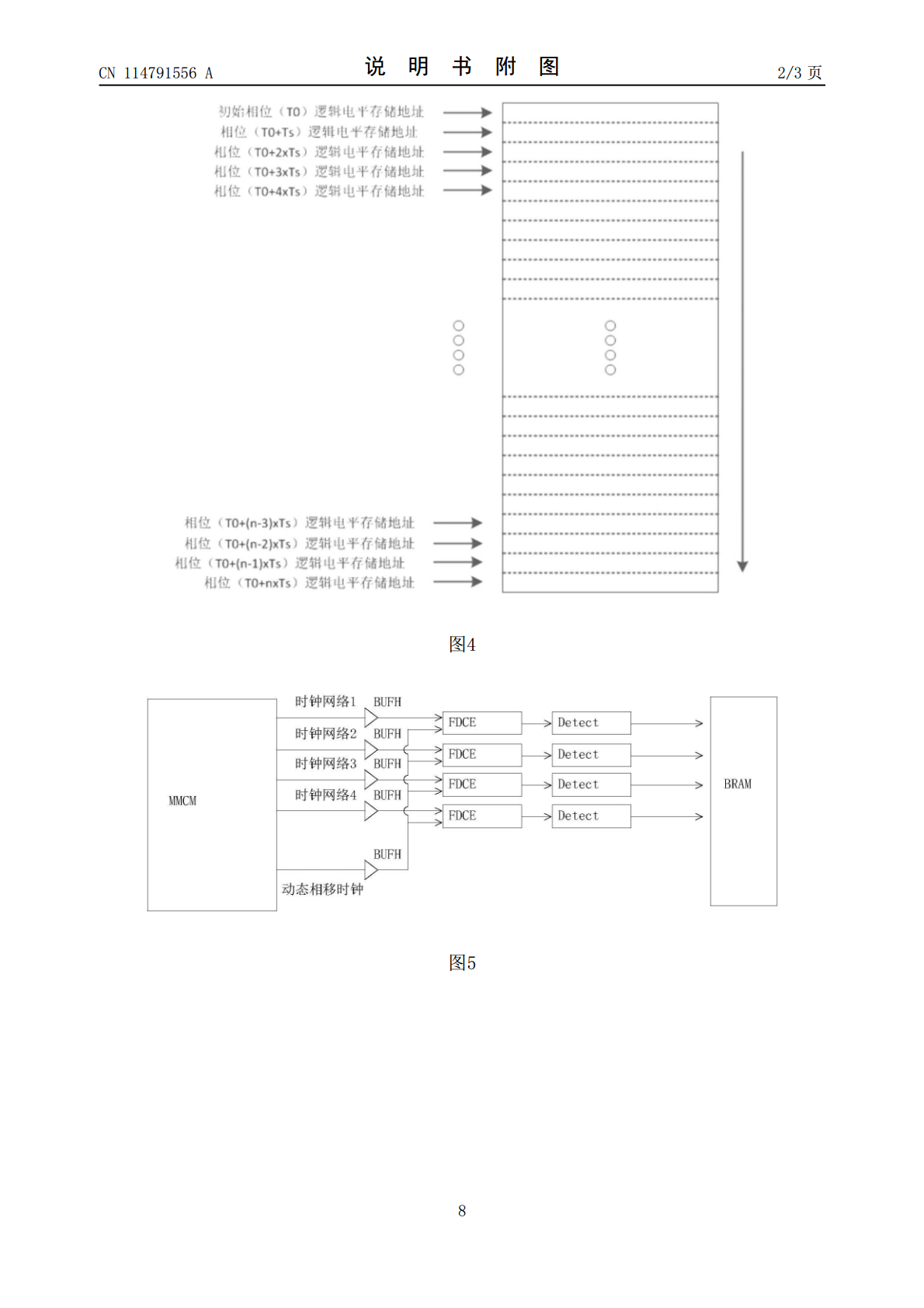

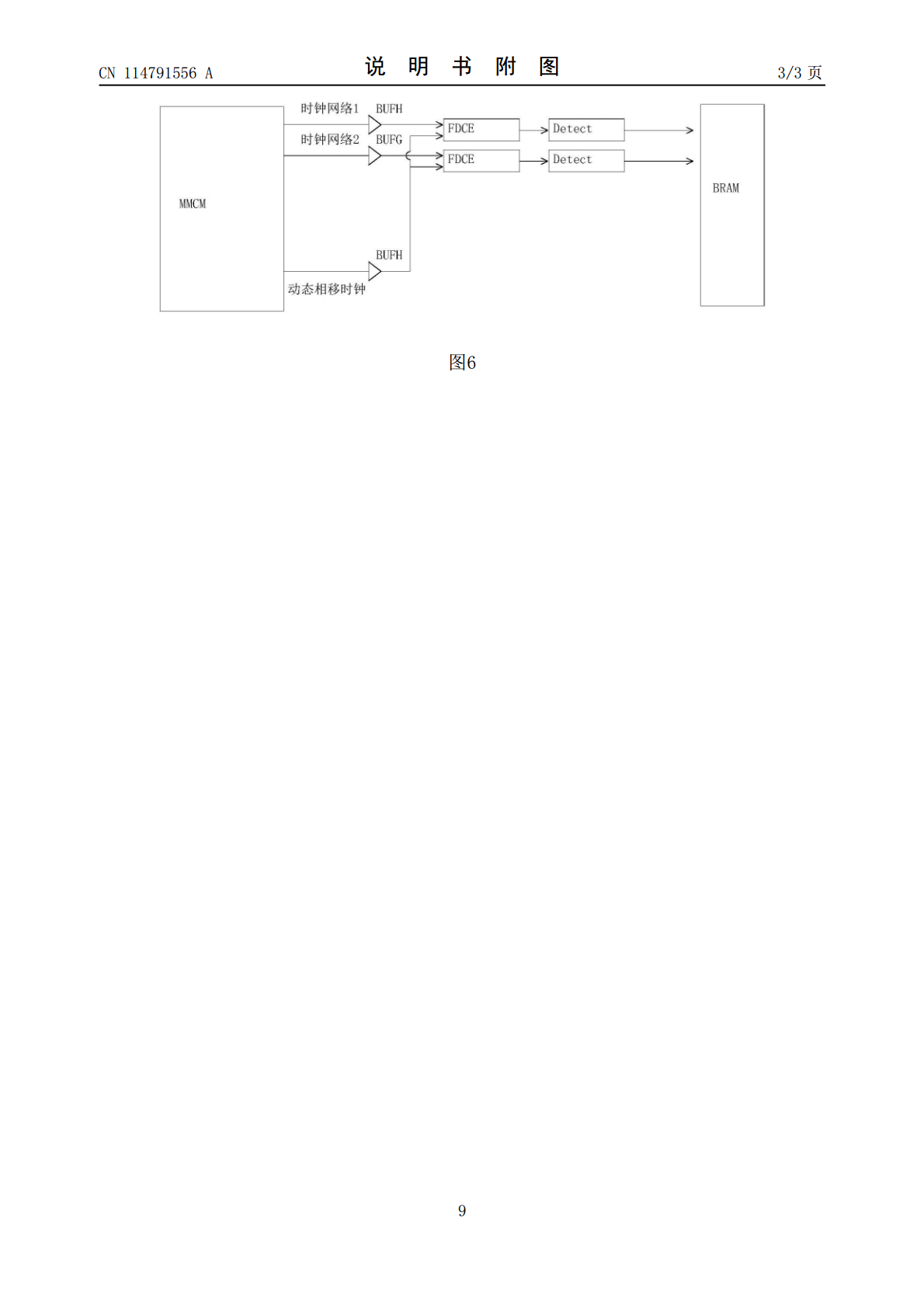

片内时钟网络延时测试方法和测试电路,涉及集成电路技术,本发明的测试方法包括下述步骤:1)芯片内部的时钟管理电路模块提供控制时钟信号和N路测试时钟信号,各测试时钟信号的相位相同,N为大于2的整数;2)构造N个测试支路,每一测试支路包括一个时钟网络路径和与之连接的触发器,测试支路和测试时钟信号一一对应接入;3)控制时钟信号经过同一路径接入片内触发器区域,然后分路至各触发器,以控制时钟信号作为各触发器的控制时钟;4)通过时钟管理电路模块,以波形滑动的方式调节控制时钟信号的相位,记录各触发器的输出;5)通过各触发

一种稳定的片内时钟产生电路.pdf

本发明属于集成电路技术领域,涉及一种稳定的片内时钟产生电路。本发明包括充放电电路、比较器和时序逻辑电路。所述充放电电路中使用四个开关共同控制充电电容C1的充电和放电,产生线性上升的三角波信号。所述充放电电路中补偿电容C2用于抵消电容翻转带来的负压突变,有效地稳定了充电节点VC处三角波的波形和频率。所述比较器将充电三角波信号VC与参考电压源VREF相比较,输出信号供给时序逻辑电路。所述时序逻辑电路与比较器的输出相连,用于产生第一时钟SW和第二时钟SW_B,且两者为非交叠时钟信号。本发明通过将电容C1上下极板

基于片上时钟的全速测试电路的设计的中期报告.docx

基于片上时钟的全速测试电路的设计的中期报告中期报告:基于片上时钟的全速测试电路的设计本项目是设计一个基于片上时钟(Oscillator)的全速测试电路,目的是为了测试芯片的稳定性和性能。在本项目的前期工作中,我们已经确定了电路的基本需求并完成了初步的电路设计。本中期报告将介绍我们在这个阶段所做的工作和取得的进展情况。电路设计:在前期工作的基础上,我们进一步优化了电路设计。为了减小电路的功耗和提高电路的性能,我们采用了新的方案来实现时钟双重注入。我们还重新设计了电路的中间放大器和可变频率调制器,以提高电路的

时钟调整电路和时钟电路的调整方法.pdf

本发明提供一种时钟调整电路和时钟电路的调整方法,包括:时钟缓冲放大器,用于接收外部差分时钟信号,将差分时钟信号整形为单端方波时钟信号,并将单端方波时钟信号输出;鉴相器,用于接收来自时钟缓冲放大器的单端方波时钟信号和来自占空比调整电路的反馈信号,将单端方波时钟信号的相位和反馈信号的相位进行比较,得到相位差值,并将相位差值输出;占空比调整电路,用于利用相位差值调整反馈信号的占空比,得到调整后的反馈信号。本发明将差分信号整形为单端方波时钟信号后与反馈信号进行比较得到相位差,根据相位差来调整占空比,能够有效减少占

用于像素阵列的片上测试的电路和方法.pdf

提供了用于像素阵列的片上测试的电路和方法。通过将信号跃迁施加到控制接线,并且基于在控制接线上检测到的电压信号来检测控制接线上的信号跃迁的至少一部分的持续时间,执行对图像传感器的像素阵列的控制接线的测试。基于检测到的持续时间与阈值的比较,指示控制接线中的电故障。