时钟调整电路和时钟电路的调整方法.pdf

一吃****春艳

亲,该文档总共17页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

时钟调整电路和时钟电路的调整方法.pdf

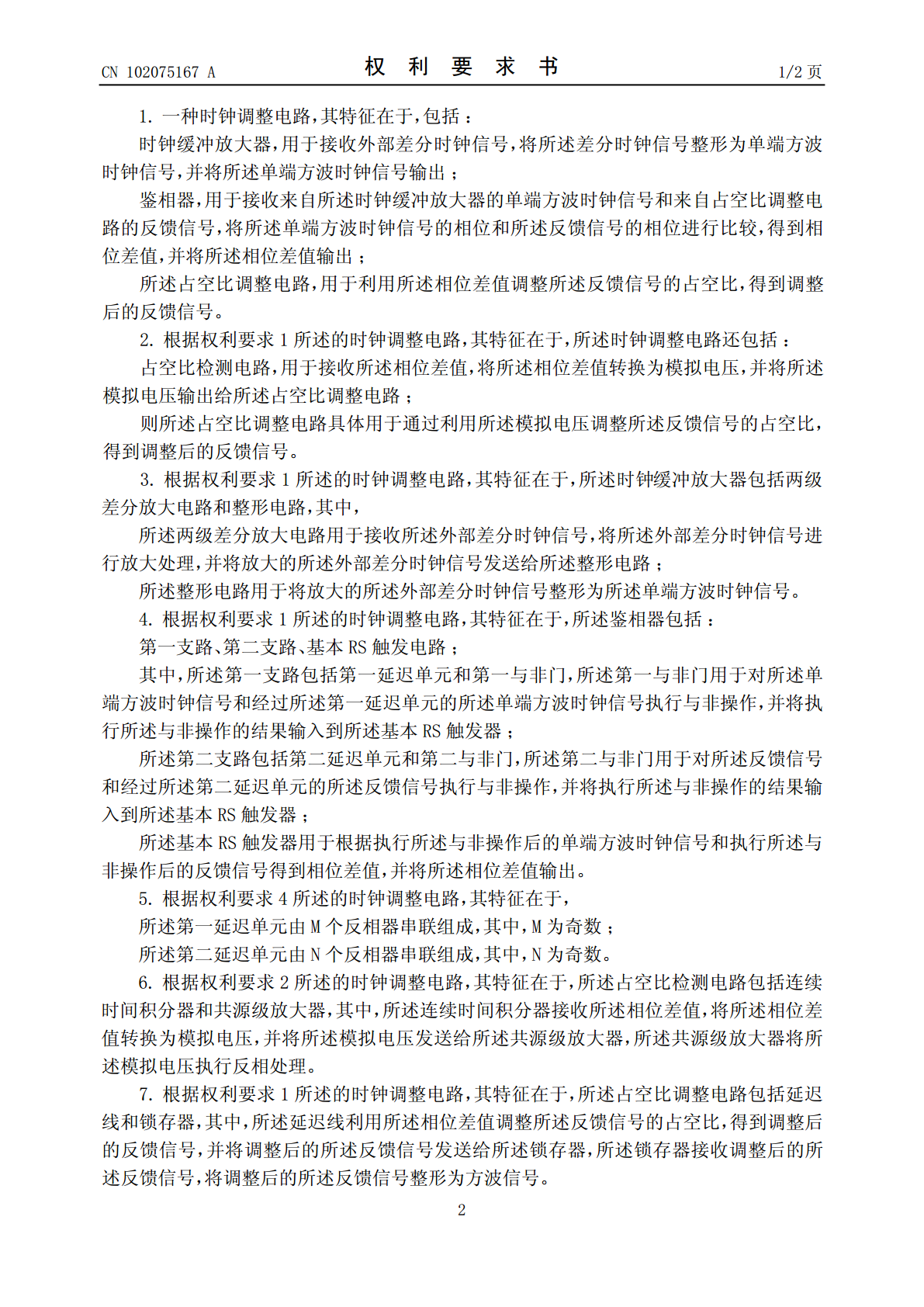

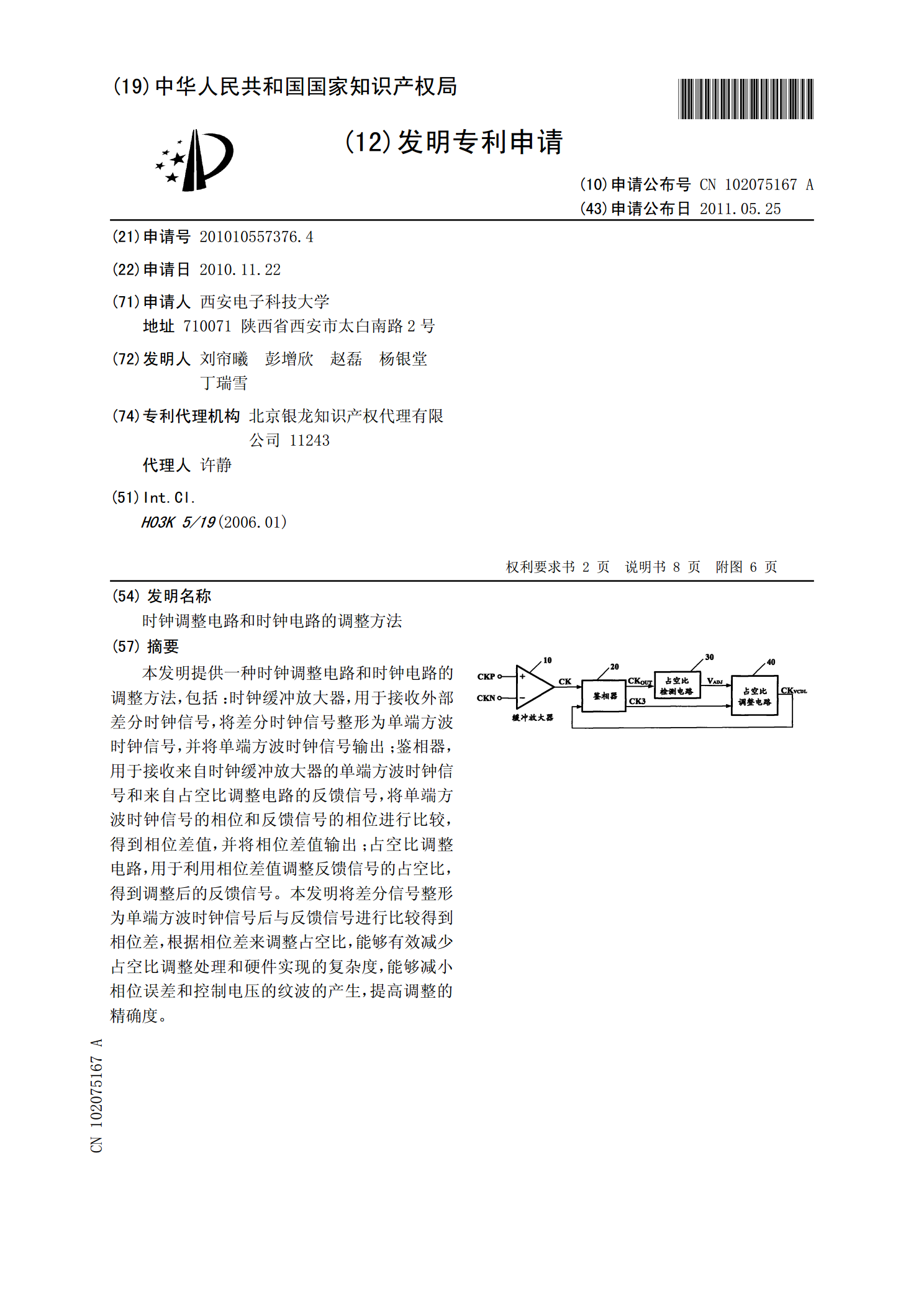

本发明提供一种时钟调整电路和时钟电路的调整方法,包括:时钟缓冲放大器,用于接收外部差分时钟信号,将差分时钟信号整形为单端方波时钟信号,并将单端方波时钟信号输出;鉴相器,用于接收来自时钟缓冲放大器的单端方波时钟信号和来自占空比调整电路的反馈信号,将单端方波时钟信号的相位和反馈信号的相位进行比较,得到相位差值,并将相位差值输出;占空比调整电路,用于利用相位差值调整反馈信号的占空比,得到调整后的反馈信号。本发明将差分信号整形为单端方波时钟信号后与反馈信号进行比较得到相位差,根据相位差来调整占空比,能够有效减少占

时钟信号传输调整方法及相关集成电路结构.pdf

(19)中华人民共和国国家知识产权局(12)发明专利说明书(10)申请公布号CN104573146A(43)申请公布日2015.04.29(21)申请号CN201310485341.8(22)申请日2013.10.16(71)申请人联华电子股份有限公司地址中国台湾新竹科学工业园区(72)发明人陈建宏(74)专利代理机构北京市柳沈律师事务所代理人史新宏(51)Int.CIG06F17/50权利要求说明书说明书幅图(54)发明名称时钟信号传输调整方法及相关集成电路结构(57)摘要一种时钟信号传输调整方法,应用

时钟分相方法、时钟分相电路及多相开关电路.pdf

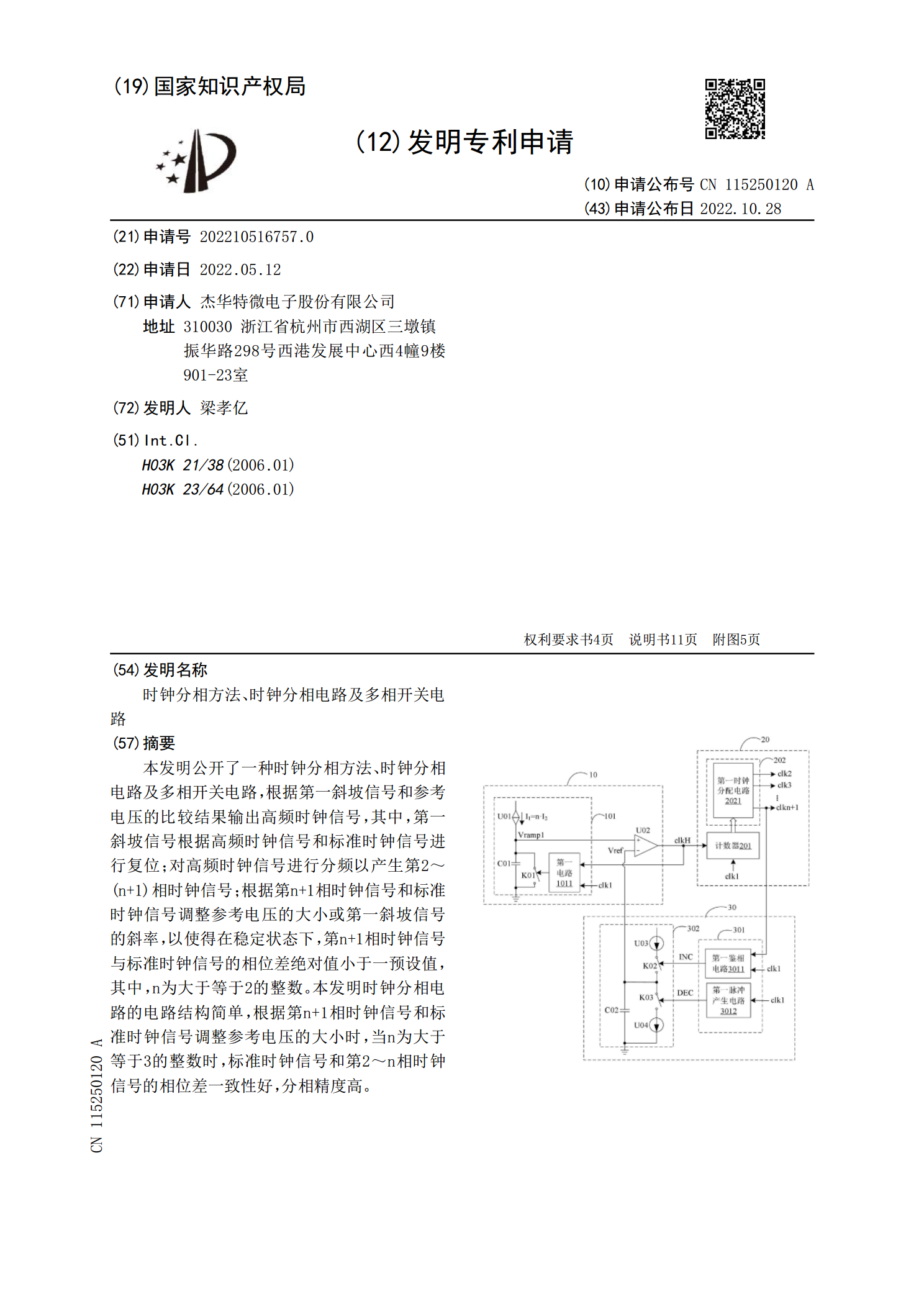

本发明公开了一种时钟分相方法、时钟分相电路及多相开关电路,根据第一斜坡信号和参考电压的比较结果输出高频时钟信号,其中,第一斜坡信号根据高频时钟信号和标准时钟信号进行复位;对高频时钟信号进行分频以产生第2~(n+1)相时钟信号;根据第n+1相时钟信号和标准时钟信号调整参考电压的大小或第一斜坡信号的斜率,以使得在稳定状态下,第n+1相时钟信号与标准时钟信号的相位差绝对值小于一预设值,其中,n为大于等于2的整数。本发明时钟分相电路的电路结构简单,根据第n+1相时钟信号和标准时钟信号调整参考电压的大小时,当n为大

时钟信号处理电路及方法.pdf

本发明实施例提供了一种液晶电视的时钟信号处理电路和方法,属于电路技术领域,处理电路包括时钟信号电路,传输线路和同向比例运算电路,时钟信号电路将液晶电视主板发出的第一时钟信号通过传输线路传输;传输线路的一端连接时钟信号电路的输出端,另一端连接同向比例运算电路的输入端;同向比例运算电路接收从输入端输入的时钟信号并进行处理,将处理后的时钟信号从输出端输出。本发明实施例通过同向比例运算电路对经过传输线路或者被干扰的时钟信号进行整形,从而能够恢复原始的时钟信号,从而更加准确的控制液晶电视的背光显示,提高屏幕的显示质

一种时钟调整、时钟偏差计算方法、设备及系统.pdf

本申请实施例提供一种时钟调整、时钟偏差计算方法、设备及系统,涉及通信技术领域,能够提高终端与接入网设备间的同步精度。具体方案为:终端向接入网设备发送第一信号;接收接入网设备发送的第一时刻值和信号时偏,第一时刻值指示接入网设备接收第一信号的时刻,信号时偏包括残留时偏Δt,Δt的绝对值小于定时提前TA调整粒度;根据第一时刻值、信号时偏和第二时刻值,计算时钟偏差,第二时刻值指示终端发送第一信号的时刻,时钟偏差为终端中配置的第一时钟与接入网设备中配置的第二时钟之间的时间差值;根据时钟偏差调整第一时钟。本申请实施例