具有电磁屏蔽功能的多芯片三维堆叠结构及其制备方法.pdf

猫巷****觅蓉

亲,该文档总共13页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

具有电磁屏蔽功能的多芯片三维堆叠结构及其制备方法.pdf

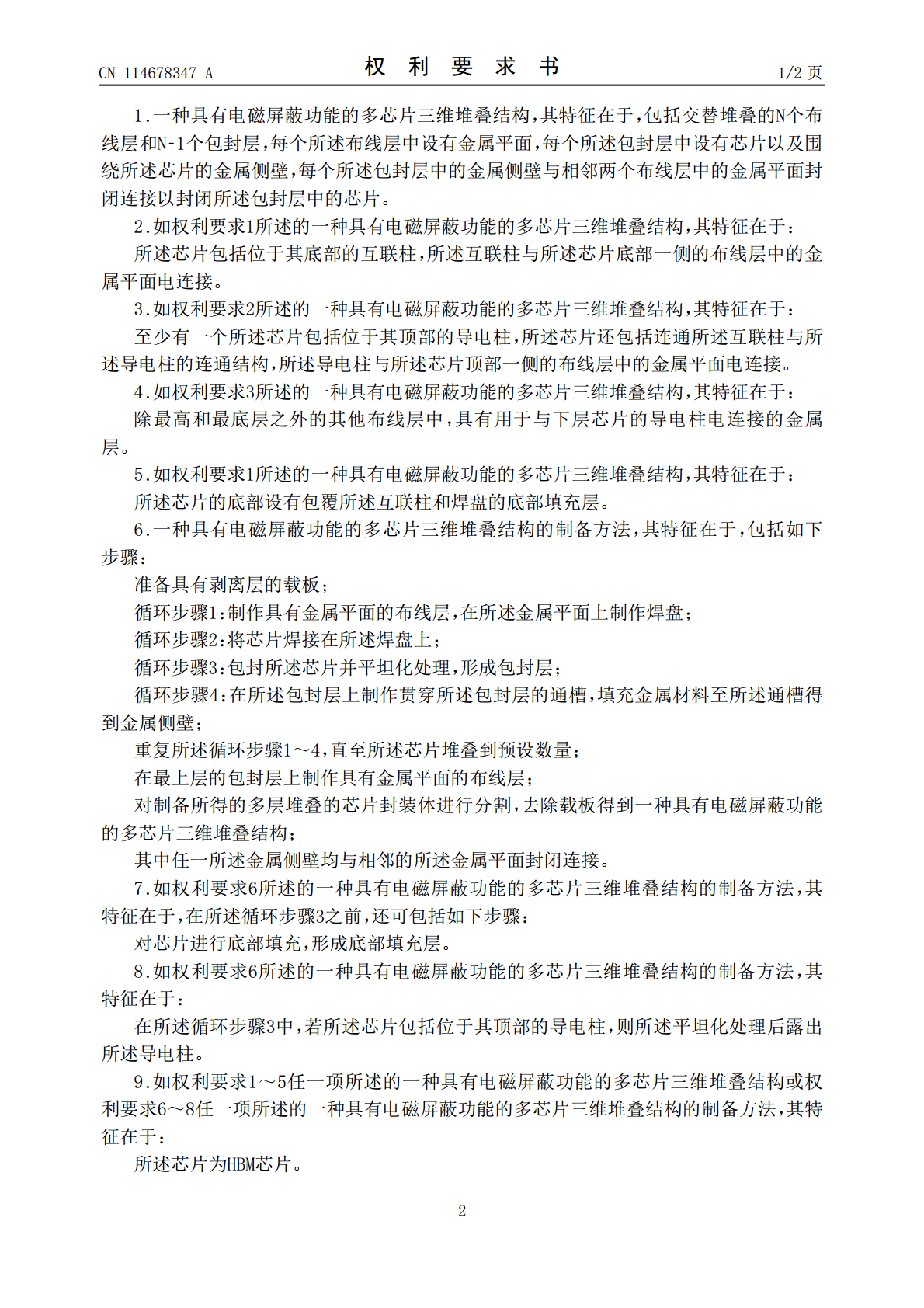

本发明公开了一种具有电磁屏蔽功能的多芯片三维堆叠结构,包括交替堆叠的N个布线层和N?1个包封层,每个所述布线层中设有金属平面,每个所述包封层中设有芯片以及围绕所述芯片的金属侧壁,每个所述包封层中的金属侧壁与相邻两个布线层中的金属平面封闭连接以封闭所述包封层中的芯片。本发明还公开了一种具有电磁屏蔽功能的多芯片三维堆叠结构的制备方法。本发明解决了三维堆叠结构中芯片的电磁干扰问题和信号串扰问题,还提升了三维堆叠结构的散热效果。

具有复合功能的IGBT芯片结构的制备方法.pdf

本发明提供了一种具有复合功能的IGBT芯片结构的制备方法,涉及半导体器件制造领域。包括在半导体衬底中形成沟槽,在沟槽内形成独立成段的分离栅多晶硅层,在分离栅多晶硅层上淀积并刻蚀金属层,使分离栅多晶硅层与金属层相连接、组成热敏电阻结构;也就是说,可以在沟槽内部形成独立成段的分离栅多晶硅层,并能够将其作为IGBT芯片的内置温度传感器。因此,本发明解决了现有在IGBT芯片上集成温度传感器的方案中所存在的准确性低和灵敏度差的问题;同时,可以在一定程度上降低IGBT芯片中的米勒电容,从而能够有效提高芯片的性能、保证

多芯片堆叠封装方法及多芯片堆叠封装体.pdf

本发明提供一种多芯片堆叠封装方法及多芯片堆叠封装体,本发明的优点在于采用重布线层与导电柱的联合的方式实现叠层芯片之间的互联,取代传统堆叠芯片封装常用的打线工艺和基板倒装的工艺,相比传统芯片叠层BGA封装,整体封装厚度更薄,相同芯片数量下封装尺寸小,具有良好的导电性、导热性和可靠性。

一种晶圆级芯片结构、多芯片堆叠互连结构及制备方法.pdf

本发明公开了一种晶圆级芯片结构、多芯片堆叠互连结构及制备方法,其中晶圆级芯片结构,包括:硅通孔,所述硅通孔位于晶圆的第一表面至第二表面的预设距离;晶圆的第一表面包括:有源区、多层再分布线层以及凸点;所述晶圆的第二表面包括:凸点下金属化层及凹形绝缘介质层,所述凹形绝缘介质层的凹形结构数量与所述硅通孔的数量一致,且所述凹形绝缘介质层的底部被所述硅通孔的底部隔断,所述凸点下金属化层填充所述凹形绝缘介质层内与所述硅通孔电连接。本申请提供的实施例对TSV盲孔刻蚀片内深度均匀性不敏感,避免了现有技术中的超高选择比Si

抗反射电磁屏蔽结构及其制备方法.pdf

本发明涉及一种电磁屏蔽结构及其制备方法,尤其是一种抗反射电磁屏蔽结构及其制备方法。按照本发明提供的技术方案,所述抗反射电磁屏蔽结构,包括衬底以及设置于所述衬底上的纳米森林结构,在所述纳米森林结构上设置金属薄膜,且纳米森林结构上所有的金属薄膜相互连接呈一体。本发明得到的电磁屏蔽结构具有较大的电导率以及低反射率,有效实现电磁屏蔽,与现有工艺兼容。