清华数字电路时序逻辑电路.pptx

胜利****实阿

亲,该文档总共155页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

清华数字电路时序逻辑电路.pptx

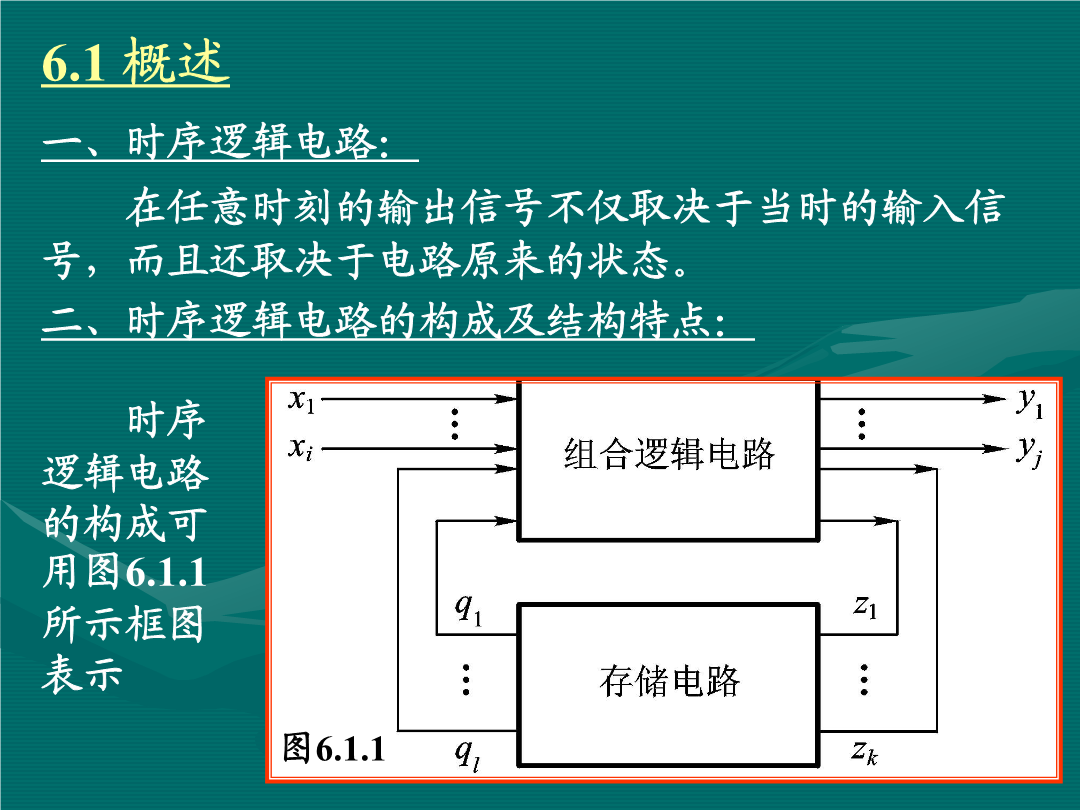

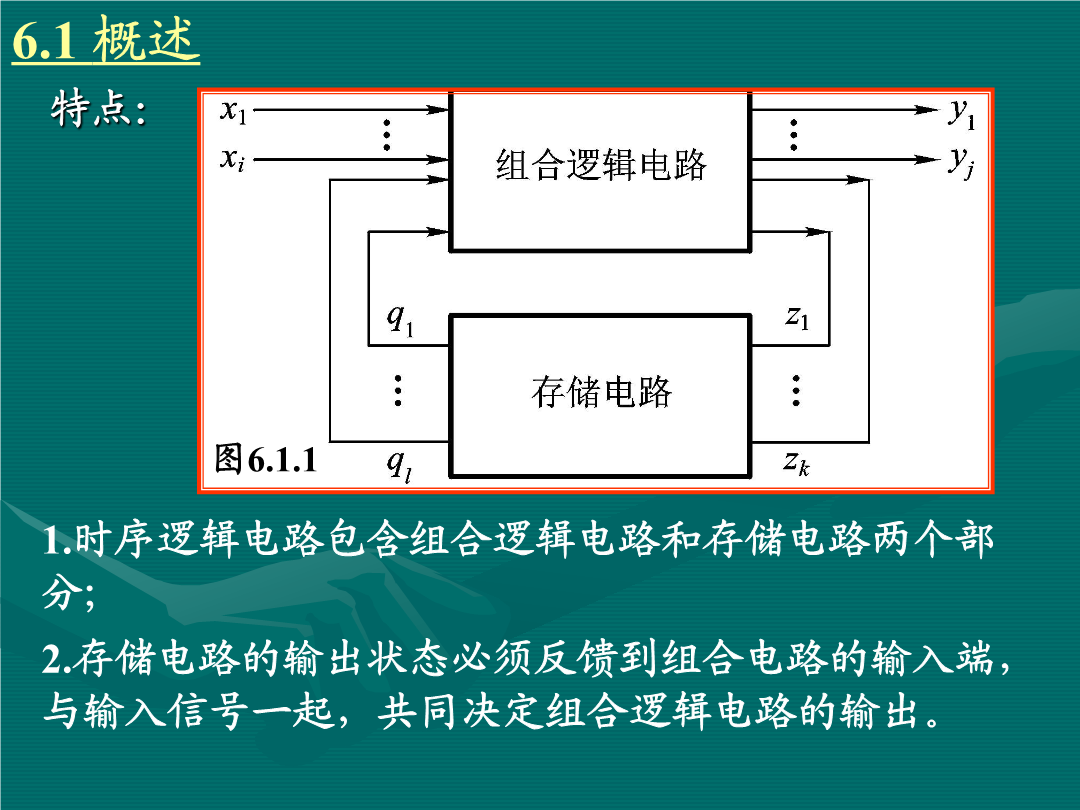

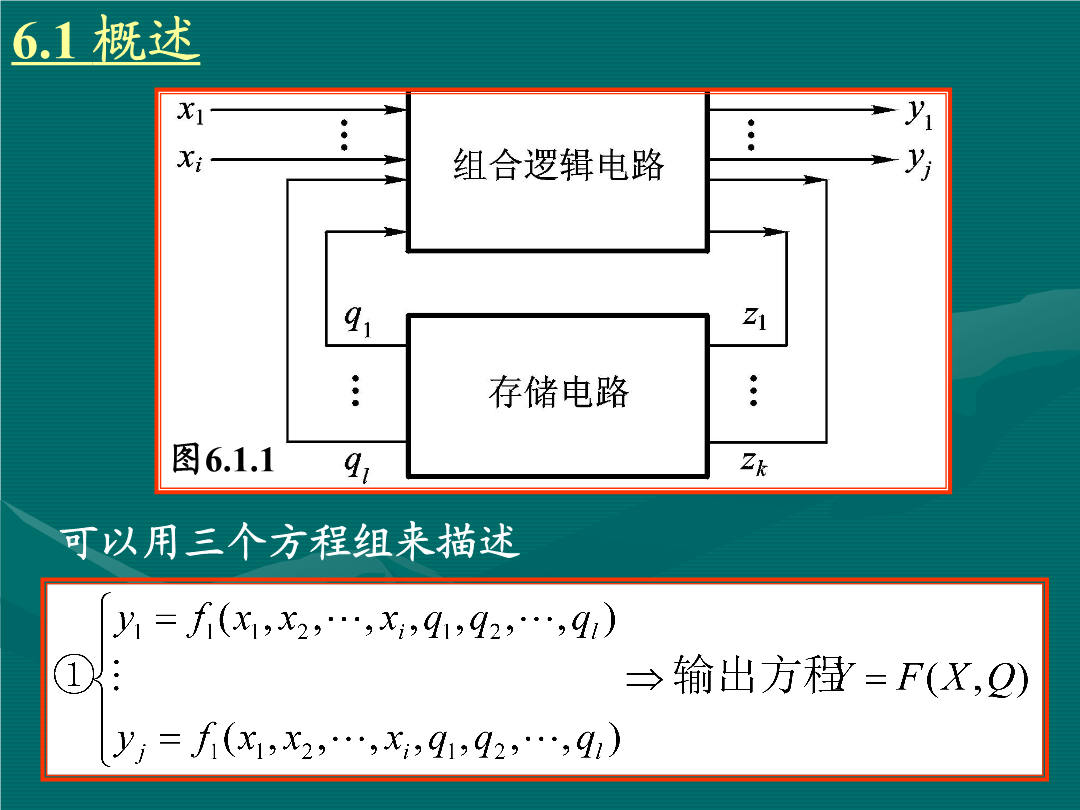

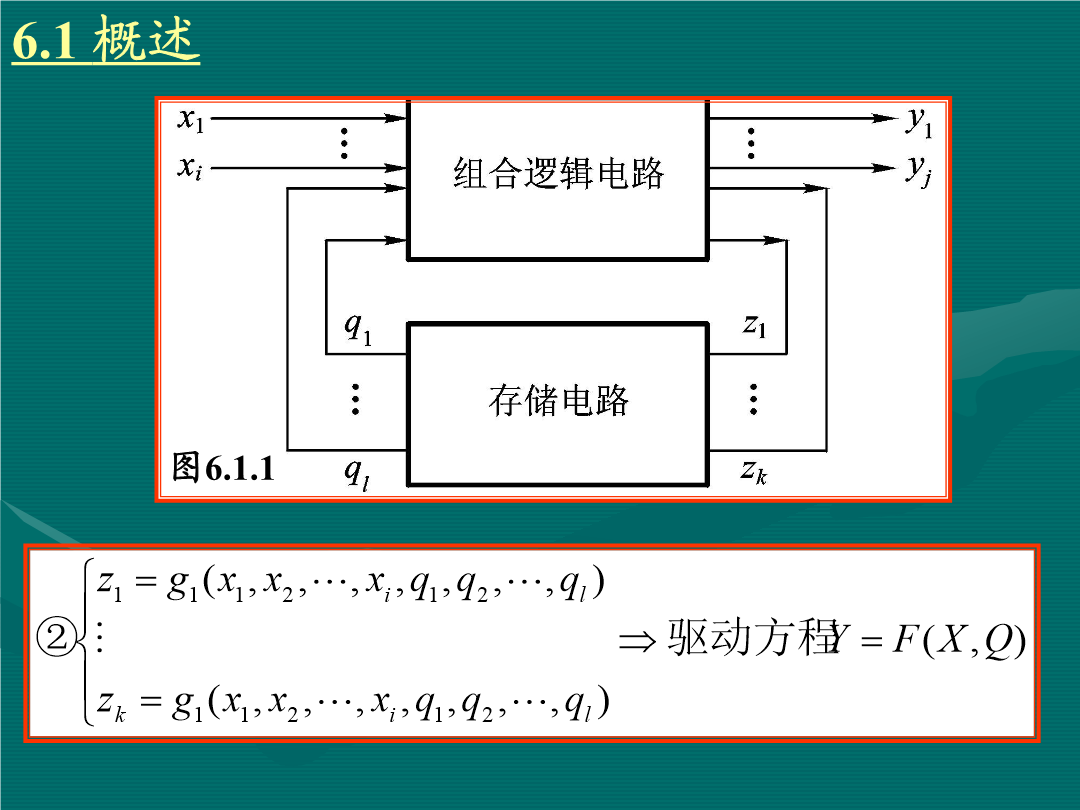

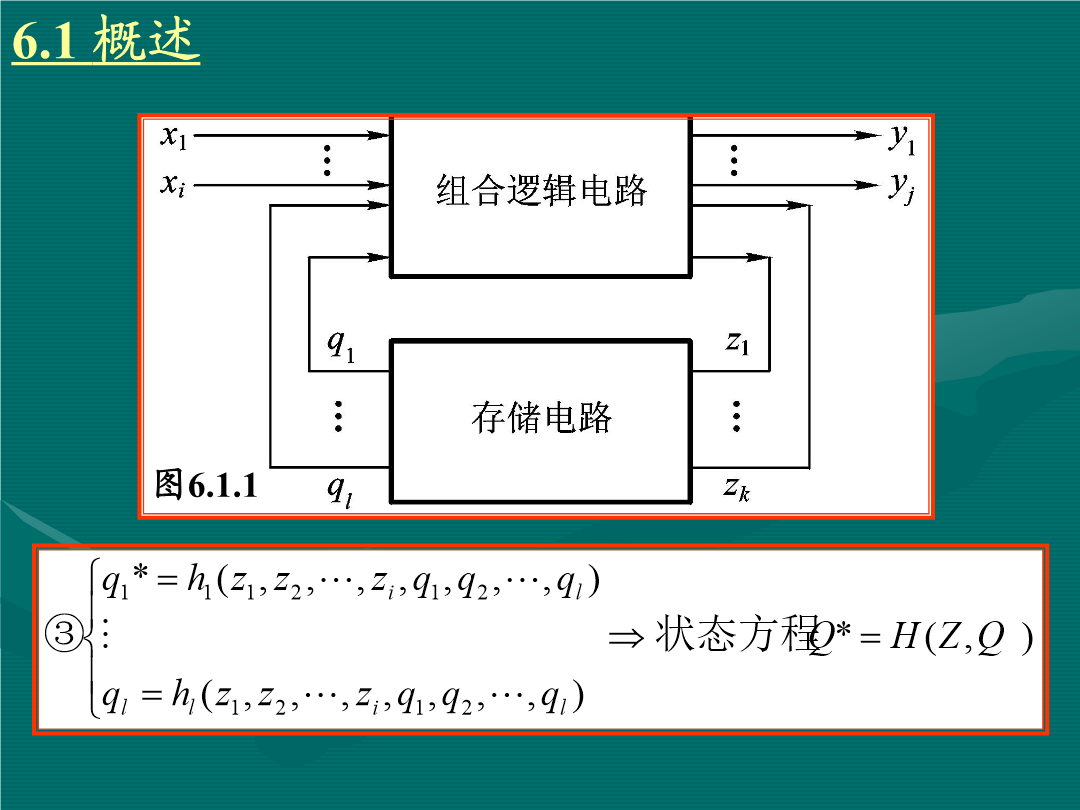

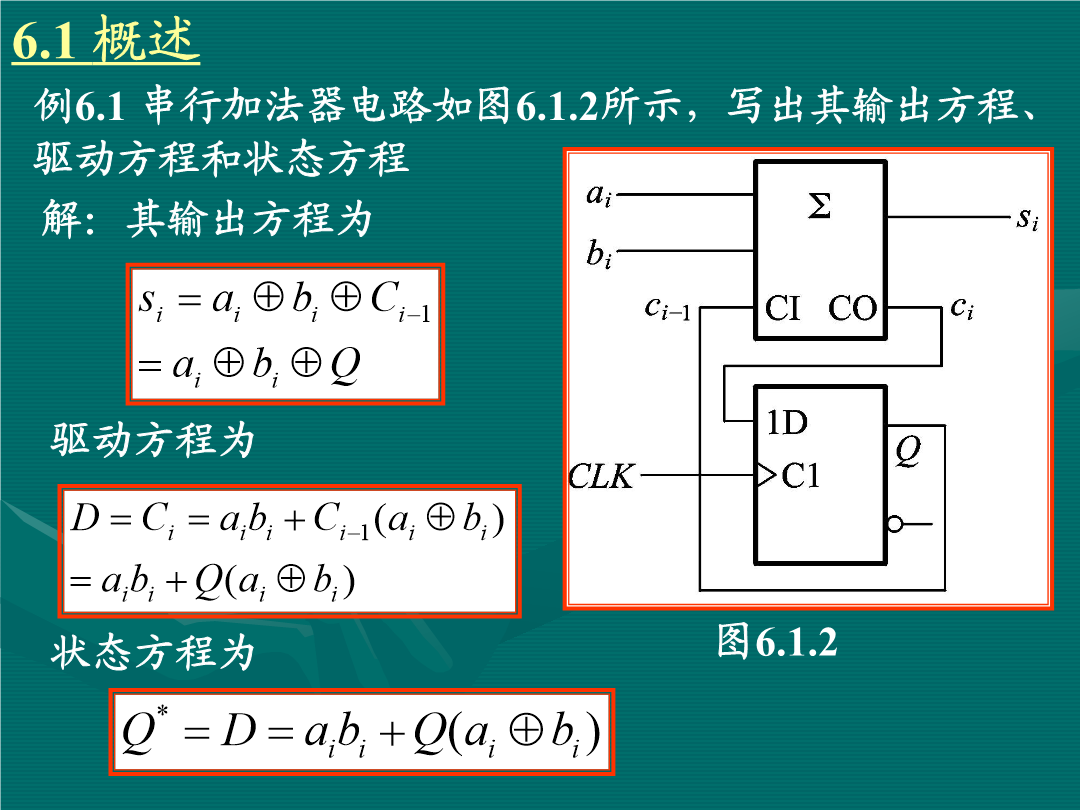

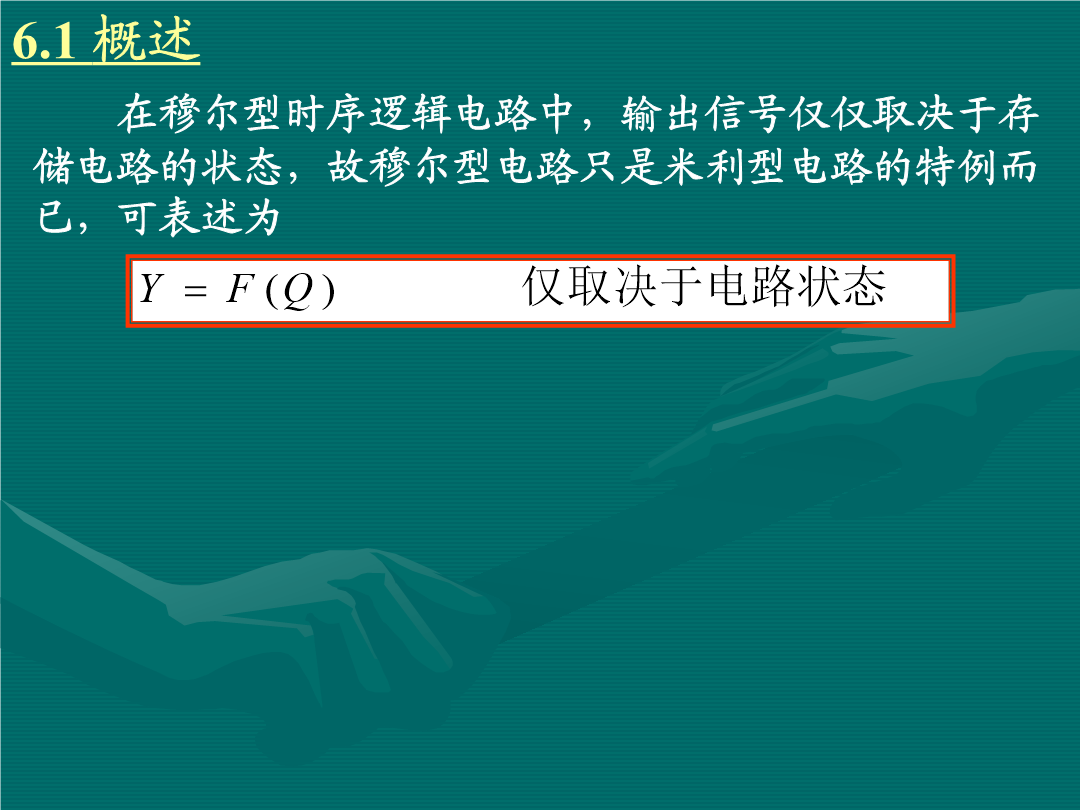

2024/2/8本章主要内容6.1概述特点:可以用三个方程组来描述6.1概述6.1概述例6.1串行加法器电路如图6.1.2所示,写出其输出方程、驱动方程和状态方程三、时序逻辑电路的分类:在穆尔型时序逻辑电路中,输出信号仅仅取决于存储电路的状态,故穆尔型电路只是米利型电路的特例而已,可表述为6.2.时序逻辑电路的分析方法2.把得到的驱动方程代入相应触发器的特性方程中,就可以得到每个触发器的状态方程,由这些状态方程得到整个时序逻辑电路的方程组;例6.2.1试分析图6.2.1所示的时序逻辑电路的逻辑功能,写出它

数字电路常见时序逻辑电路寄存器.pptx

第六章时序逻辑电路本章主要内容一.寄存器二.计数器同步计数器异步计数器任意进制计数器旳构成措施移位寄存器型计数器数字系统中,常需要将某些数码临时存储起来,这种临时存储数码旳逻辑部件称为寄存器。寄存器旳电路构造涉及两部分:①触发器:具有0,1两个稳定状态,所以1个触发器能够寄存1位二进制数码,N位寄存器由N个触发器构成,可存储一组N位二值代码。②寄存器还应具有由门电路构成旳控制电路,以确保信号旳接受和清除。按照是否具有移位功能,分为:一般寄存器(只具有存储功能)移位寄存器(具有存储与移位功能)①按照数码移动

数字电路与逻辑设计习题时序逻辑电路.docx

第六章时序逻辑电路选择题1.同步计数器和异步计数器比较,同步计数器的显著优点是。A.工作速度高B.触发器利用率高C.电路简单D.不受时钟CP控制。2.把一个五进制计数器与一个四进制计数器串联可得到进制计数器。A.4B.5C.9D.203.下列逻辑电路中为时序逻辑电路的是。A.变量译码器B.加法器C.数码寄存器D.数据选择器4.N个触发器可以构成最大计数长度(进制数)为的计数器。A.NB.2NC.N2D.2N5.N个触发器可以构成能寄存位二进制数码的寄存器。A.N-1B.NC.N+1D.2N6.五个D触发器

物理数字电路时序逻辑电路修改学习教案.pptx

会计学2时序(shíxù)逻辑电路的分类5.2时序(shíxù)逻辑电路的分析方法5.2.1时序逻辑电路的分析(fēnxī)步骤电路图5.确定(quèdìng)逻辑功能3.求出电路(diànlù)状态方程*5.2.3异步时序逻辑电路的分析(fēnxī)举例例1(3)列状态表、画状态图和时序(shíxù)图(4)逻辑(luójí)功能分析设计步骤:1)逻辑抽象:求状态转换表和(或)状态转换图a.分析给定的逻辑问题,确定输入变量、输出变量以及电路的状态数;b.定义输入、输出变量和状态的含义,并将状态顺序编号;

数字电路第章常见时序逻辑电路计数器.pptx

数字电路第章常见时序逻辑电路计数器本章主要内容寄存器计数器同步计数器(十六进制、十进制)任意进制计数器得构成方法移位寄存器型计数器回顾:同步十进制计数器74160CLK三、任意进制计数器得构成方法例:十进制六进制构造思路:在N进制计数器得顺序计数过程中,设法跳过N-M个状态。具体方法:置零法(复位法)置数法(置位法)(1)置零法CLKR‘D=(Q’3Q2Q1Q‘0)'大家学习辛苦了,还是要坚持(2)置数法(2)置数法CLKLD‘=(Q’3Q2Q‘1Q0)'为了避免进位信号C取不到1问题:改进电路:在电路