多芯片贴装结构及其制备方法.pdf

努力****向丝

亲,该文档总共16页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

多芯片贴装结构及其制备方法.pdf

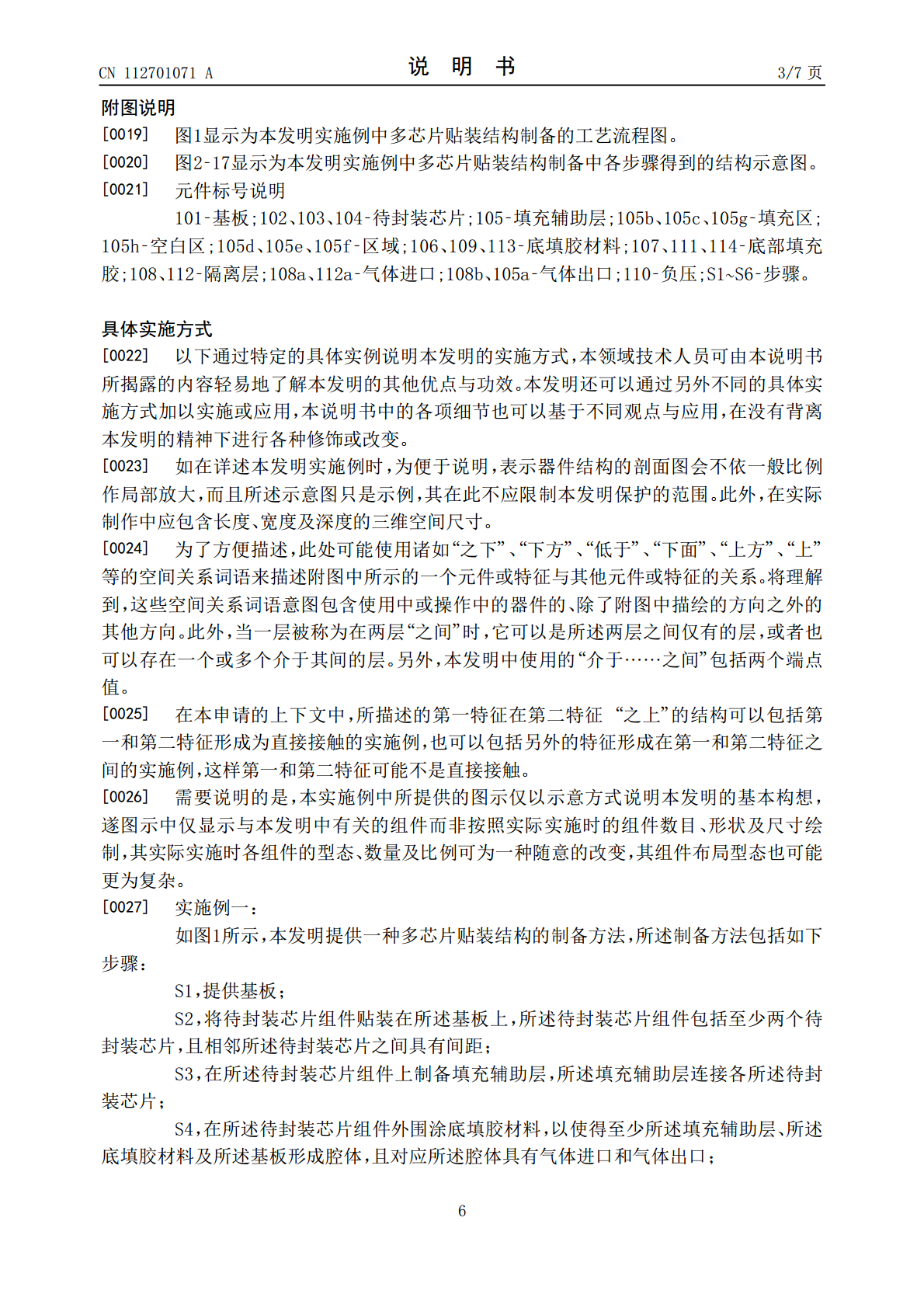

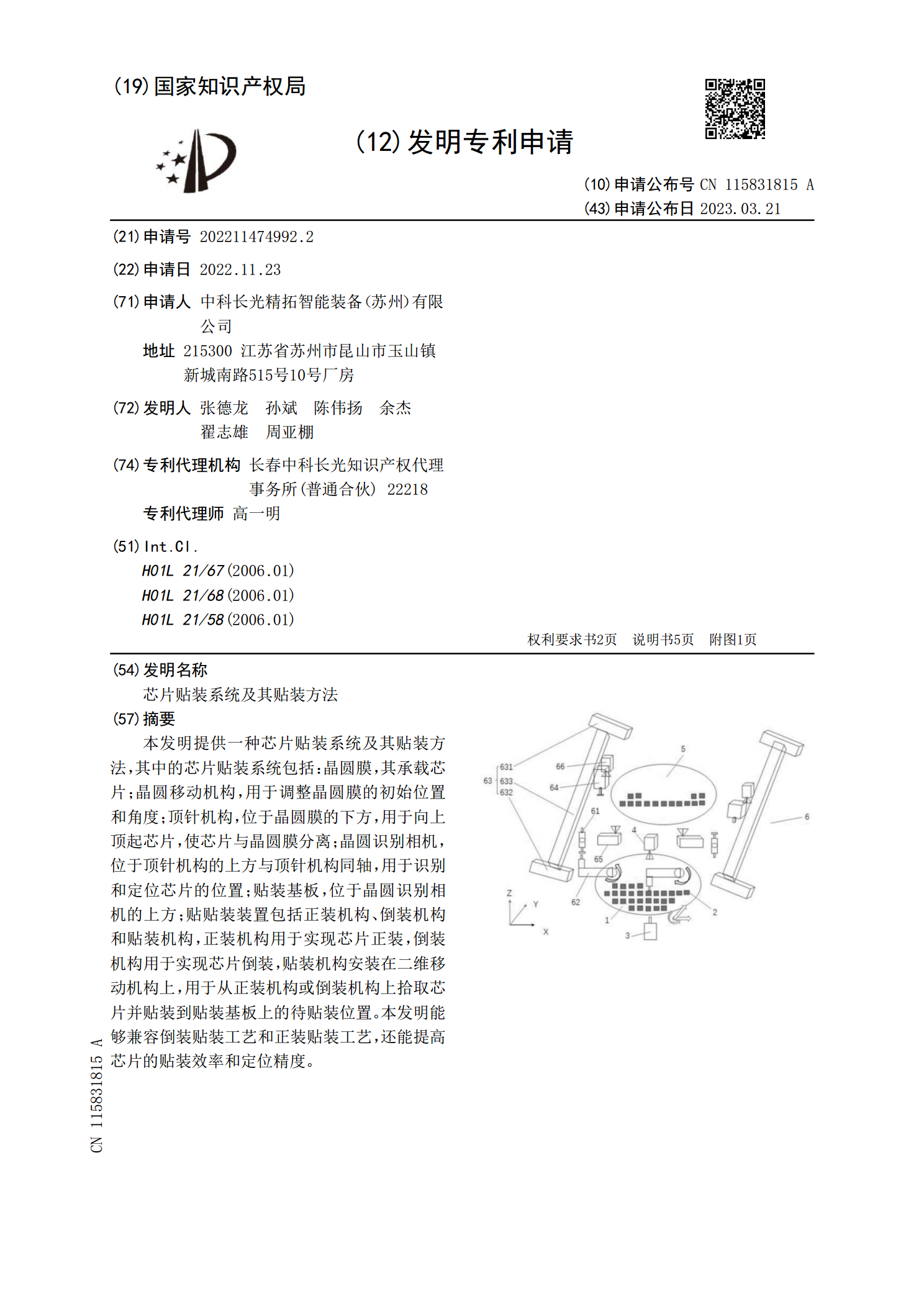

本发明提供一种多芯片贴装结构及制备方法,制备包括:在基板上贴装多个芯片,在芯片上制备填充辅助层以形成腔体,对应所述腔体具有气体进口和气体出口,在气体进口涂底填胶材料,在气体出口处施加负压,基于空气压力使底填胶材料流入芯片底部形成底部填充胶。对于多个芯片模组的封装结构,本发明在待封装芯片与基板之间构建腔体,在气体进口涂底填胶材料,在气体出口施加负压,使底部填胶在气压作用下被压入芯片底部,能够减小多芯片结构底填胶的填充难度,有利于解决填充气泡的问题。还可解决多芯片小间距的结构中,填胶头难以放置、填胶工艺复杂及

曲面芯片贴装结构及其制备方法.pdf

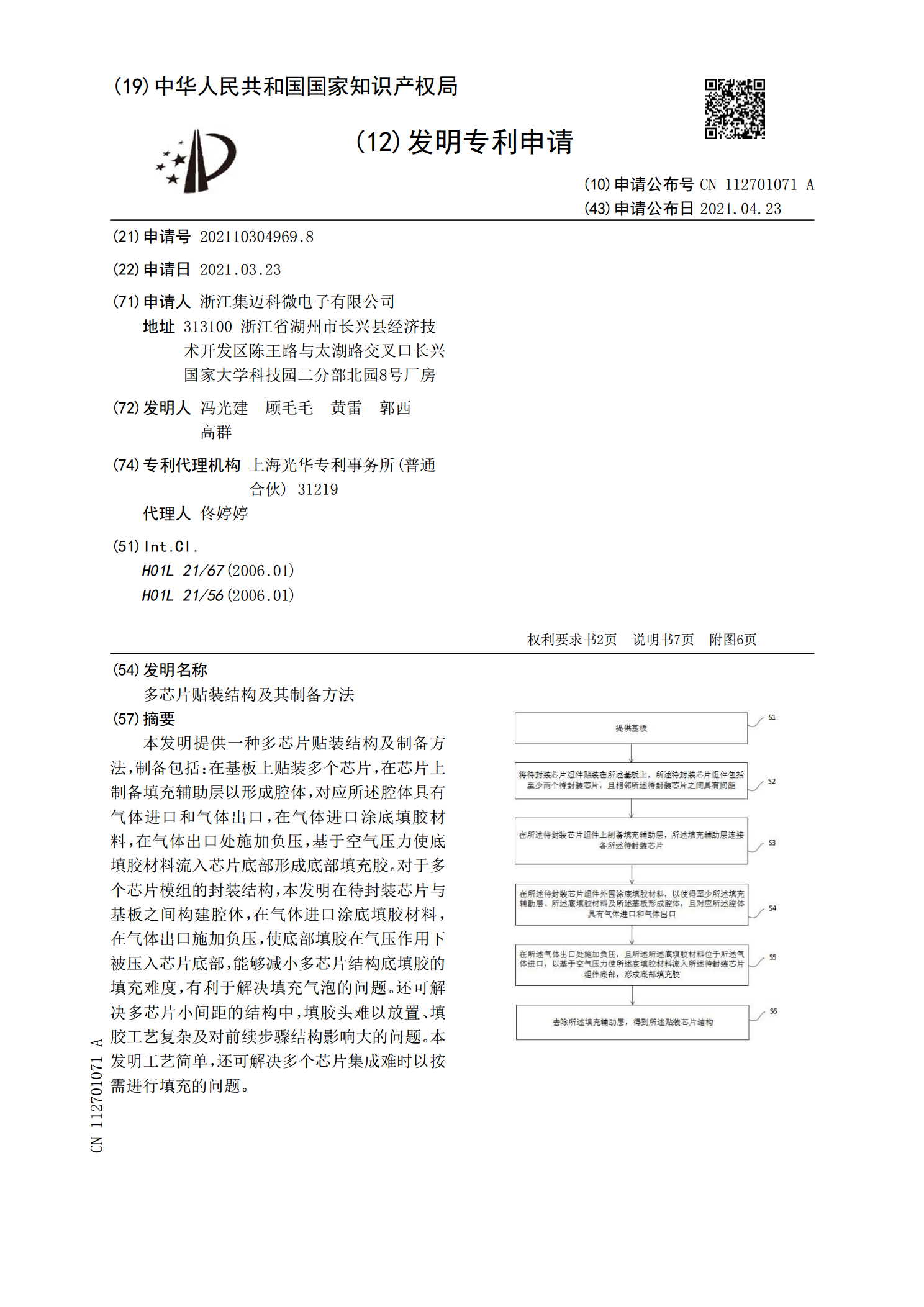

本发明提供一种曲面芯片贴装结构及其制备方法,制备包括:在曲面芯片上制备焊球,控制模具的柔性面具有第一曲面状态,将焊球焊接在柔性面上,熔融焊球并控制柔性面具有第二曲面状态,固化焊球,使得固化后焊球的顶部与柔性面的第二曲面状态相同。本发明通过引入柔性面的模具,在曲面芯片贴装过程中发生不同曲面状态的变化,使曲面芯片表面的熔融的焊球发生形状变换,使固化后焊球顶部形成需要的状态,使原本不平整的焊球重新熔融冷却后形成平滑平整的共面或根据终端的曲面形状重新固化形状。为曲面芯片、曲面玻璃等不平整电子器件解决贴片过程中脱焊

芯片贴装系统及其贴装方法.pdf

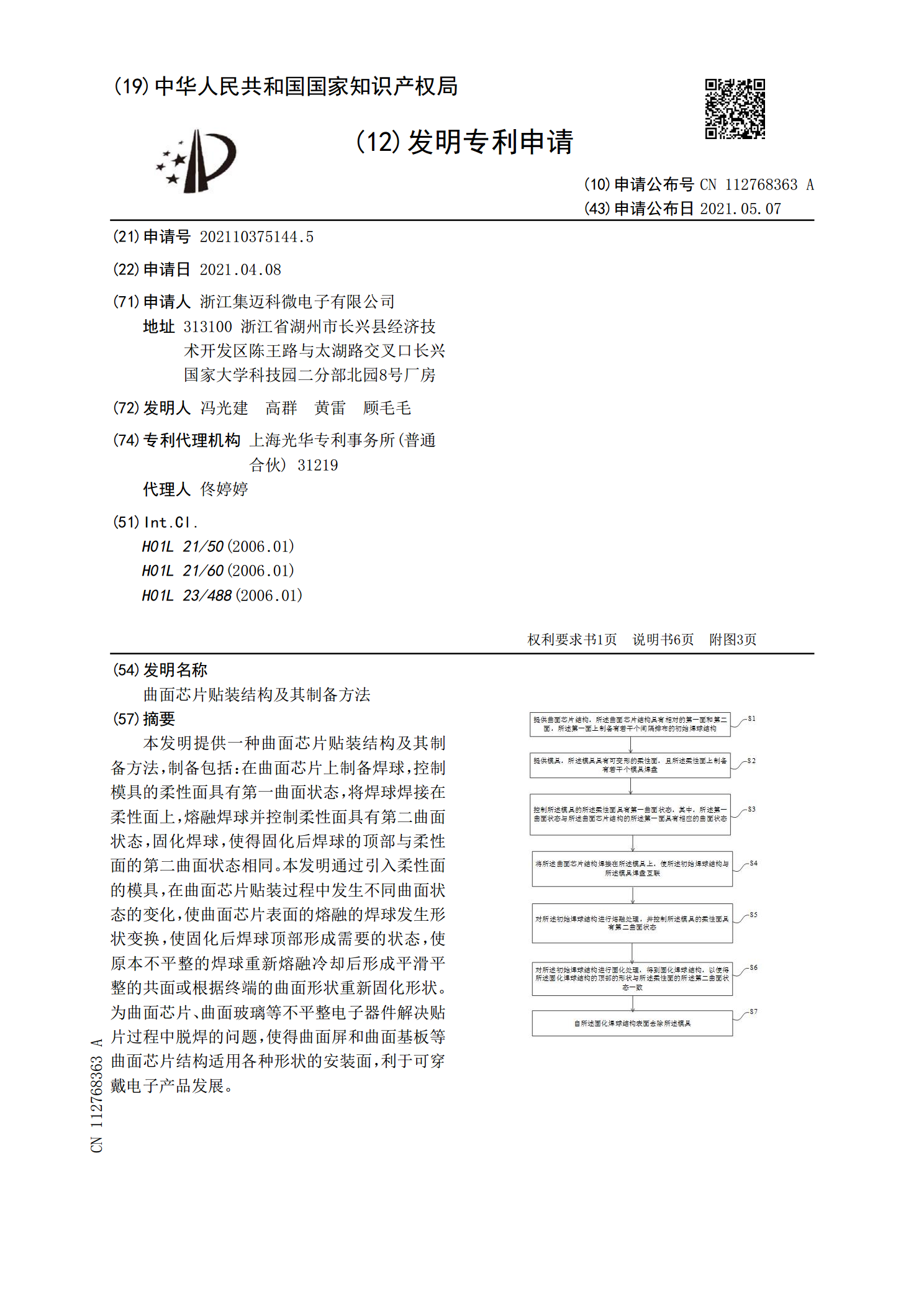

本发明提供一种芯片贴装系统及其贴装方法,其中的芯片贴装系统包括:晶圆膜,其承载芯片;晶圆移动机构,用于调整晶圆膜的初始位置和角度;顶针机构,位于晶圆膜的下方,用于向上顶起芯片,使芯片与晶圆膜分离;晶圆识别相机,位于顶针机构的上方与顶针机构同轴,用于识别和定位芯片的位置;贴装基板,位于晶圆识别相机的上方;贴贴装装置包括正装机构、倒装机构和贴装机构,正装机构用于实现芯片正装,倒装机构用于实现芯片倒装,贴装机构安装在二维移动机构上,用于从正装机构或倒装机构上拾取芯片并贴装到贴装基板上的待贴装位置。本发明能够兼容

一种芯片贴装用纳米银浆及其制备方法.pdf

本发明提供一种制备芯片贴装用纳米银浆的方法,包括以下几个步骤:步骤A.将还原剂和分散剂滴入硝酸银溶液中,搅拌;步骤B.将步骤A所得的溶液进行离心分离,得到上层为混合溶液,下层为沉淀的纳米银颗粒;步骤C.将步骤B分离出的纳米银颗粒用去离子水清洗后,再用电解质溶液絮凝,重新析出可进行离心分离的纳米银颗粒;步骤D.将纳米银颗粒反复进行清洗、絮凝、离心多次,最终得到水溶性纳米银浆;步骤E.将步骤D得到的纳米银浆作用于芯片与基板表面进行互连,通过热风工作台或炉中加热形成烧结接头。

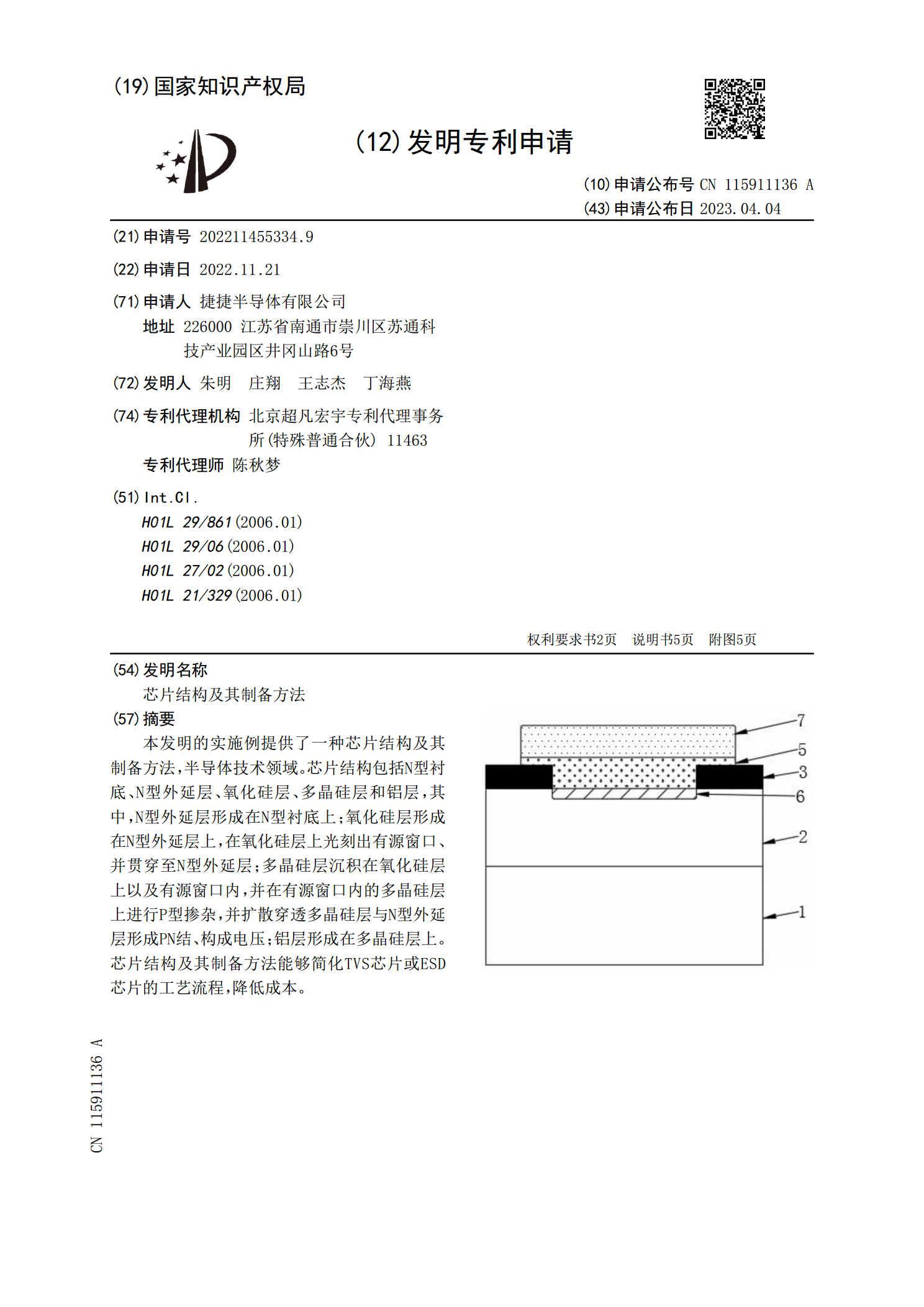

芯片结构及其制备方法.pdf

本发明的实施例提供了一种芯片结构及其制备方法,半导体技术领域。芯片结构包括N型衬底、N型外延层、氧化硅层、多晶硅层和铝层,其中,N型外延层形成在N型衬底上;氧化硅层形成在N型外延层上,在氧化硅层上光刻出有源窗口、并贯穿至N型外延层;多晶硅层沉积在氧化硅层上以及有源窗口内,并在有源窗口内的多晶硅层上进行P型掺杂,并扩散穿透多晶硅层与N型外延层形成PN结、构成电压;铝层形成在多晶硅层上。芯片结构及其制备方法能够简化TVS芯片或ESD芯片的工艺流程,降低成本。