超结器件及其制造方法.pdf

是笛****加盟

亲,该文档总共17页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

超结器件及其制造方法.pdf

本发明公开了一种超结器件,包括形成于超结结构的N型柱顶部的沟槽栅,沟道区的掺杂包括在源极对应的接触孔的开口形成后、金属填充前进行带倾角的P型离子注入形成的P型离子注入杂质,P型离子注入的注入峰值的纵向深度小于等于栅极沟槽的底部表面深度,P型离子注入使沟道区的底部形成一个深度从栅极沟槽的底部到P型柱逐渐变深的轮廓结构,沟道区的底部轮廓使超结器件单元的碰撞电离最强区域从多晶硅栅侧面覆盖位置下探到沟道区的底部轮廓区域,用以提升器件的EAS能力。本发明还公开了一种超结器件的制造方法。本发明能提高器件的EAS能力。

超结器件及其制造方法.pdf

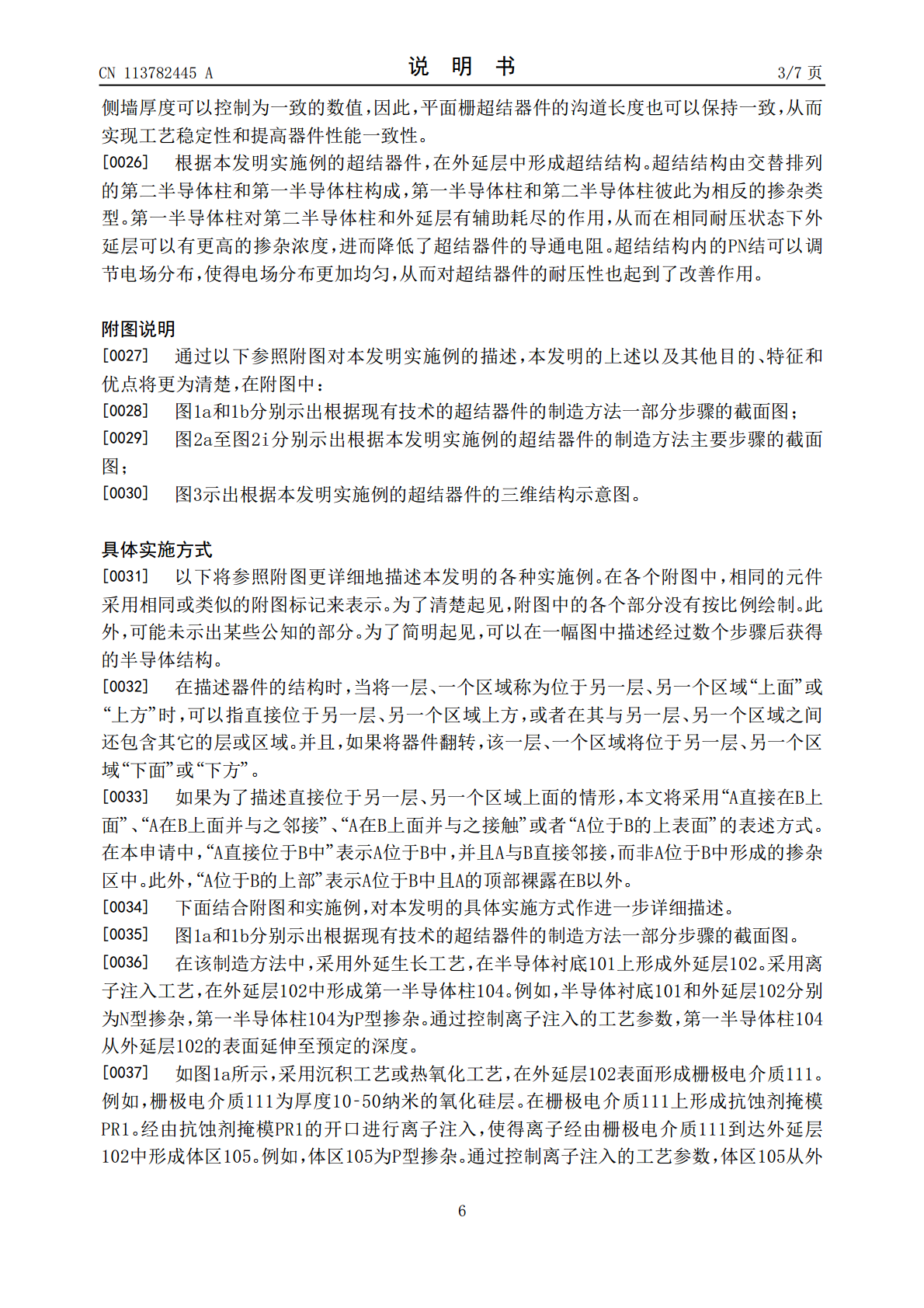

本申请公开了一种超结器件及其制造方法。该超结器件的制造方法,包括:在半导体衬底上形成外延层;在外延层中形成多个第一半导体柱;在外延层上形成牺牲叠层;以牺牲叠层作为第一硬掩模,在外延层中形成体区,体区具有与第一硬掩模对齐的第一边缘;在牺牲叠层的侧壁形成侧墙;以牺牲叠层和侧墙作为第二硬掩模,在体区中形成源区,源区具有与第二硬掩模对齐的第一边缘;去除牺牲叠层;以及在外延层上形成栅叠层,栅叠层横跨体区的第一边缘和源区的第一边缘,使得超结器件的沟道长度对应于牺牲叠层的侧墙厚度。该制造方法采用牺牲叠层的侧墙控制沟道长

超结半导体器件及其制造方法.pdf

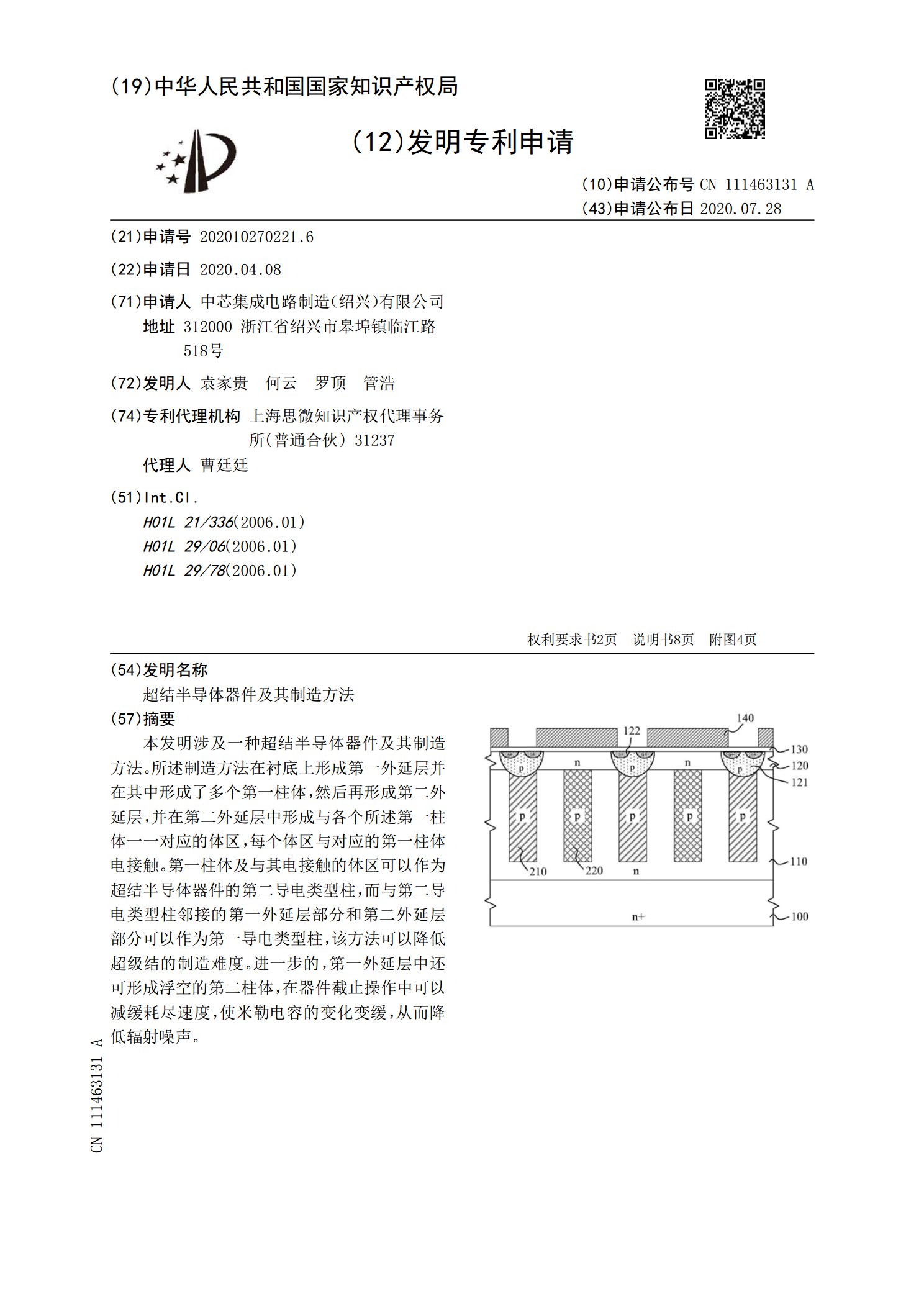

本发明涉及一种超结半导体器件及其制造方法。所述制造方法在衬底上形成第一外延层并在其中形成了多个第一柱体,然后再形成第二外延层,并在第二外延层中形成与各个所述第一柱体一一对应的体区,每个体区与对应的第一柱体电接触。第一柱体及与其电接触的体区可以作为超结半导体器件的第二导电类型柱,而与第二导电类型柱邻接的第一外延层部分和第二外延层部分可以作为第一导电类型柱,该方法可以降低超级结的制造难度。进一步的,第一外延层中还可形成浮空的第二柱体,在器件截止操作中可以减缓耗尽速度,使米勒电容的变化变缓,从而降低辐射噪声。

一种超结器件的制造方法及超结器件.pdf

本发明公开了一种超结器件的制造方法及超结器件,其中,方法包括:以1~2um/min的单晶硅生长速度在第一类型衬底上外延生长n层第一类型的单晶硅层,以最多在n‑2层单晶硅层上形成与第一类型衬底上的第一光刻对位标记正对的第二光刻对位标记,且当n大于或等于4时,除最上层单晶硅层外,在任意相邻三层单晶硅层中的至少一层单晶硅层上形成第二光刻对位标记;根据第一光刻对位标记和第二光刻对位标记,对每层单晶硅层进行光刻,以留出至少两个离子注入窗口;通过离子注入窗口对每层单晶硅层进行第二类型离子注入;将n层单晶硅层经高温推阱

沟槽栅超结IGBT器件及其制造方法.pdf

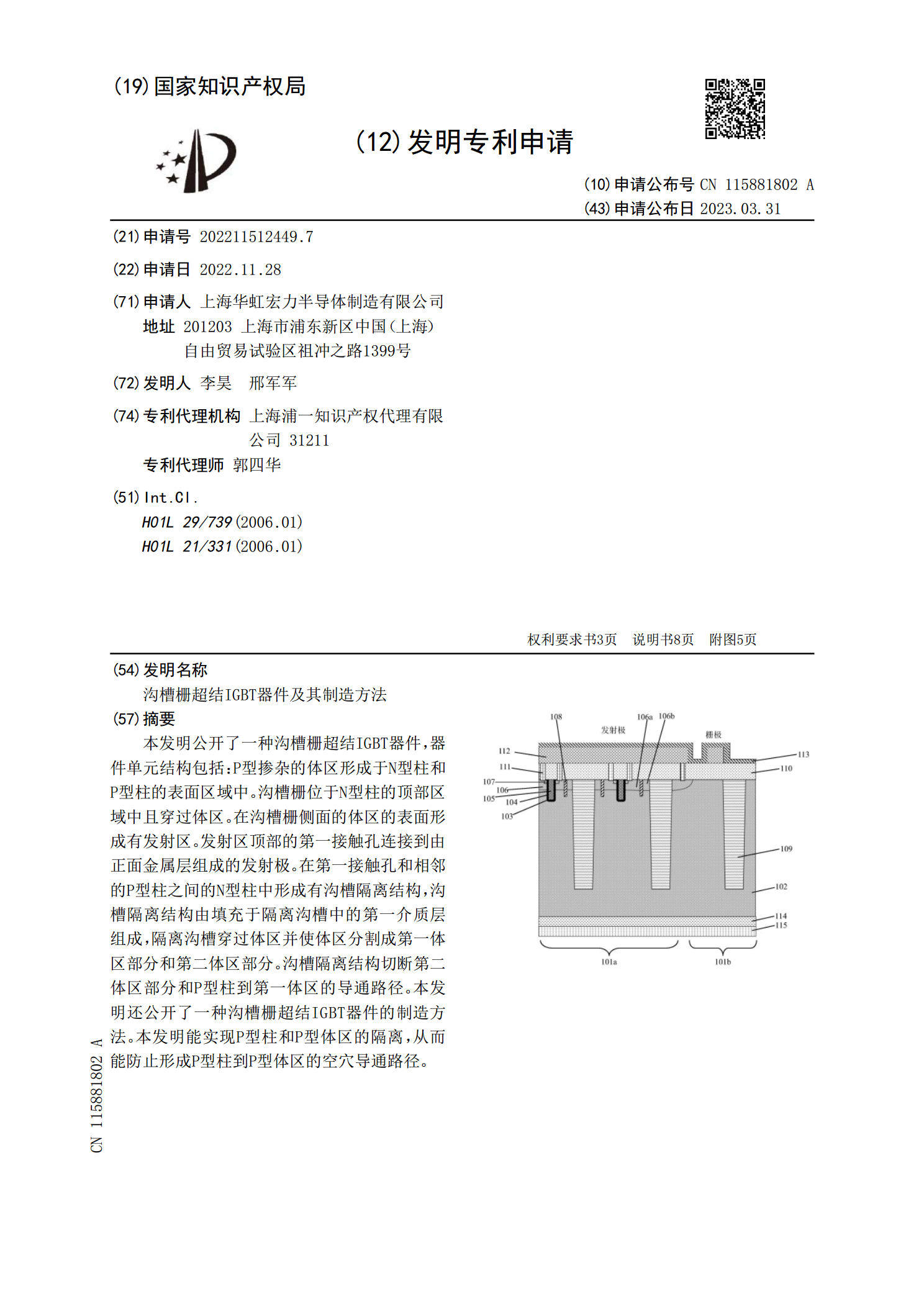

本发明公开了一种沟槽栅超结IGBT器件,器件单元结构包括:P型掺杂的体区形成于N型柱和P型柱的表面区域中。沟槽栅位于N型柱的顶部区域中且穿过体区。在沟槽栅侧面的体区的表面形成有发射区。发射区顶部的第一接触孔连接到由正面金属层组成的发射极。在第一接触孔和相邻的P型柱之间的N型柱中形成有沟槽隔离结构,沟槽隔离结构由填充于隔离沟槽中的第一介质层组成,隔离沟槽穿过体区并使体区分割成第一体区部分和第二体区部分。沟槽隔离结构切断第二体区部分和P型柱到第一体区的导通路径。本发明还公开了一种沟槽栅超结IGBT器件的制造方