一种沟槽型MOSFET及其制备方法.pdf

Ja****44

亲,该文档总共17页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种沟槽型MOSFET及其制备方法.pdf

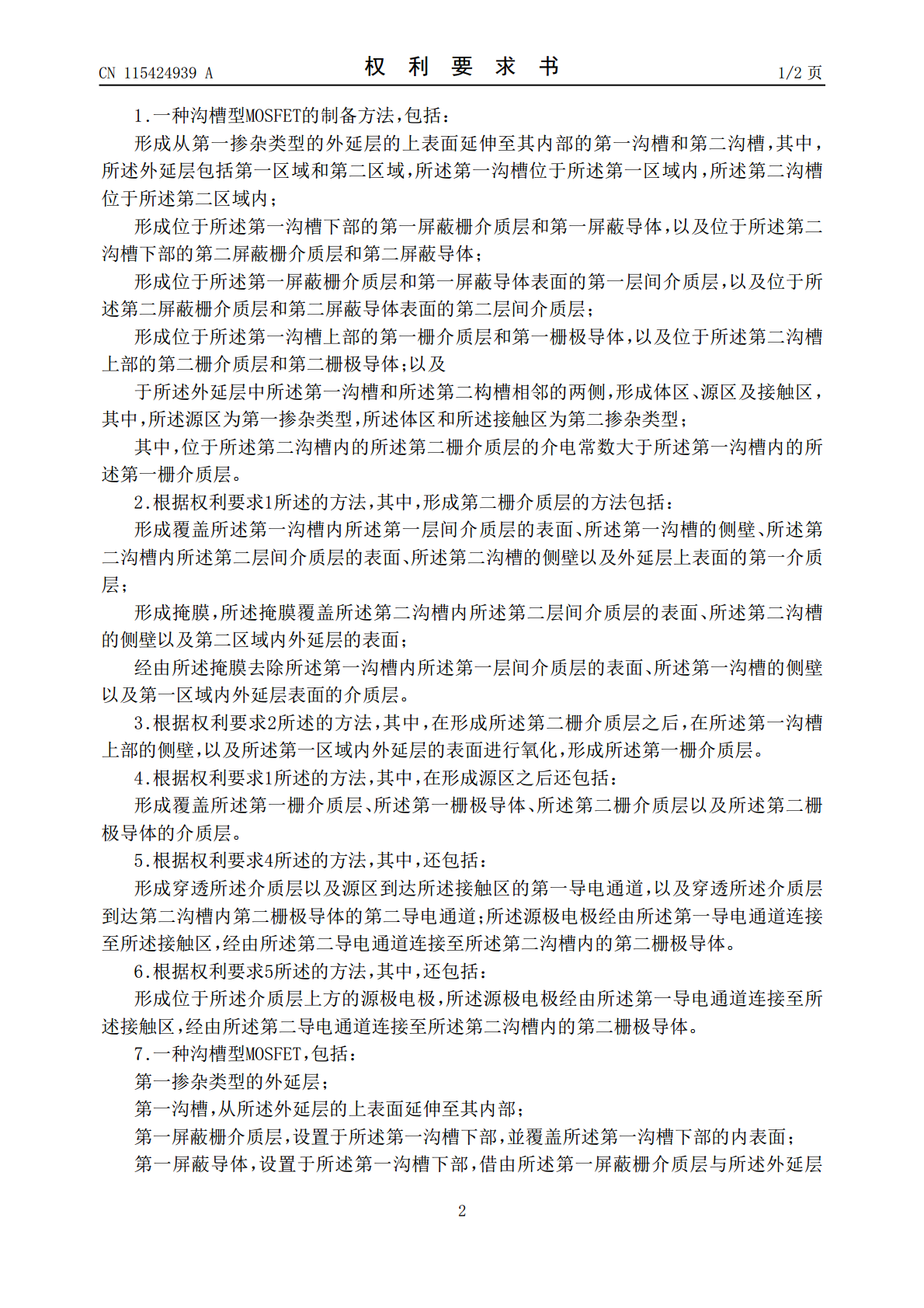

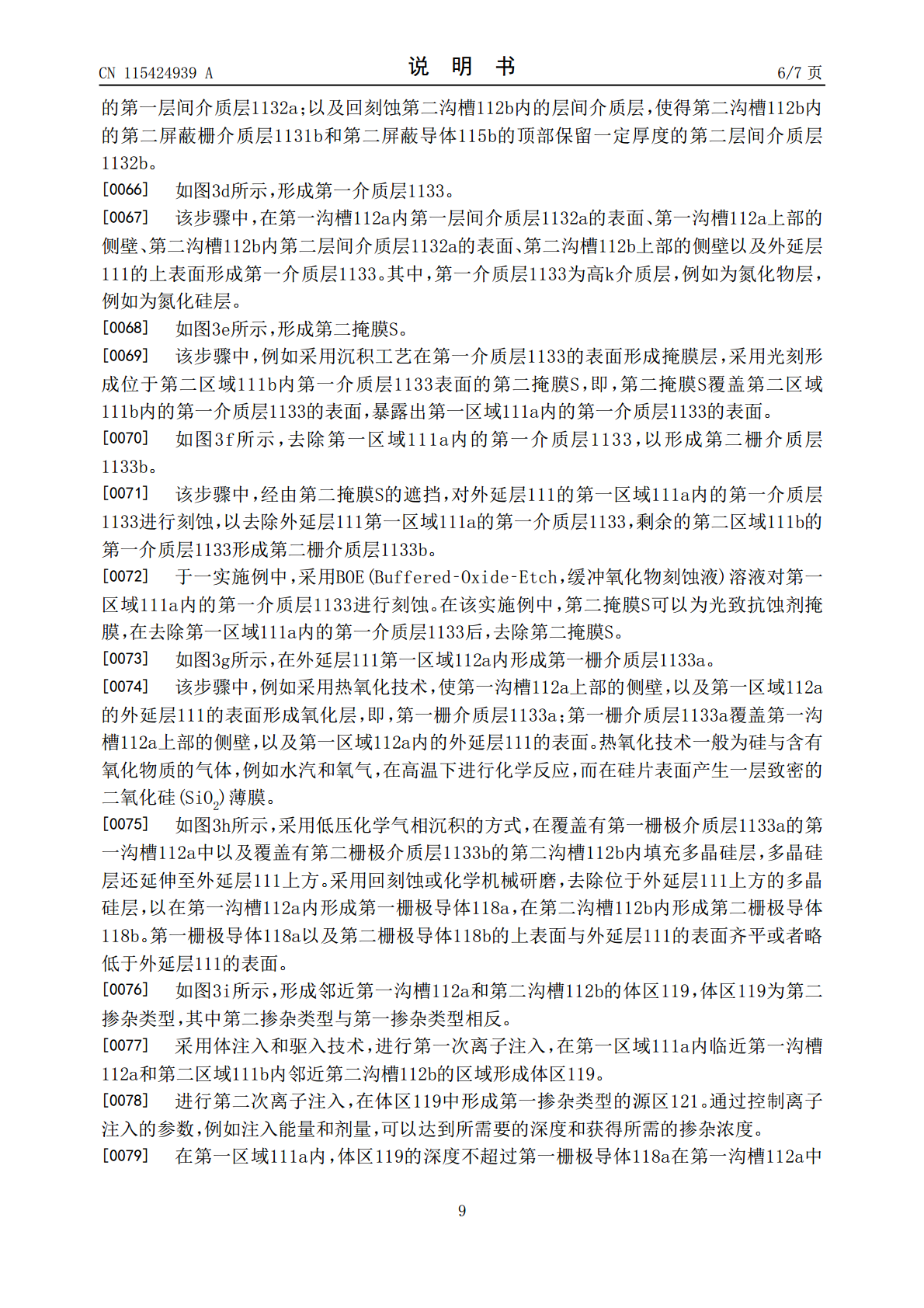

本申请公开一种沟槽型MOSFET及其制备方法,方法包括:形成从第一掺杂类型的外延层的上表面延伸至其内部的第一沟槽和第二沟槽;形成位于所述第一沟槽下部的第一屏蔽栅介质层和第一屏蔽导体,以及位于所述第二沟槽下部的第二屏蔽栅介质层和第二屏蔽导体;形成位于所述第一屏蔽栅介质层和第一屏蔽导体表面的第一层间介质层,以及位于所述第二屏蔽栅介质层和第二屏蔽导体表面的第二层间介质层;形成位于所述第一沟槽上部的第一栅介质层和第一栅极导体,以及位于所述第二沟槽上部的第二栅介质层和第二栅极导体;以及形成体区、源区及接触区,其中,

一种沟槽型MOSFET元胞结构及其制备方法.pdf

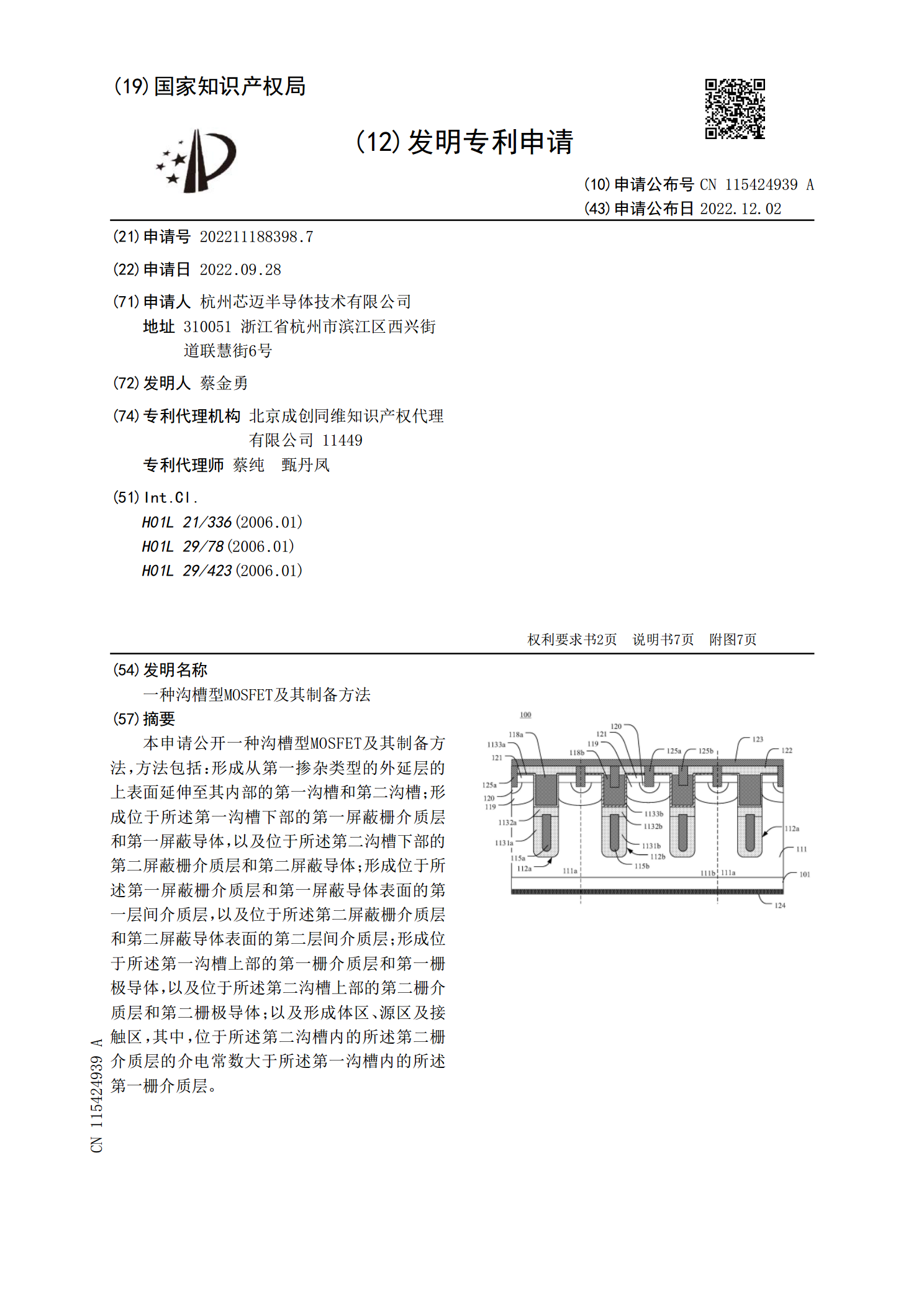

本发明公开了一种沟槽型MOSFET元胞结构,包括:栅极沟槽、辅助源极沟槽、N

一种沟槽MOSFET器件及其制备方法.pdf

本发明提供了一种沟槽MOSFET器件及其制备方法,n级阶梯源极沟槽位于栅极沟槽的底部,相当于栅极沟槽和n级阶梯源极沟槽均在同一沟槽内部可以使元胞尺寸减小,且n级阶梯源极沟槽的设置还可以使n级阶梯源极沟槽底部注入的高掺杂的第五掺杂区域更深,以更好的保护优化栅氧化层底部的电场分布;并且在源极附近还反并联肖特基二极管,在不影响元胞尺寸的基础上可显著降低MOSFET晶体管二极管压降,提升芯片的集成度,降低集成肖特基二极管的MOSFET器件的制作成本;通过多个结构的改进还可以进一步提升电流密度,降低比导通电阻,并且

一种分裂栅型沟槽MOSFET的制备方法.pdf

本发明提供一种分裂栅型沟槽MOSFET的制备方法,包括步骤:1)提供一衬底,在所述衬底表面生长一外延层;2)刻蚀所述外延层,形成具有第一深度的沟槽,在所述沟槽表面淀积氮化物层,之后腐蚀掉沟槽底部的氮化物层,保留侧壁的氮化物层;3)继续刻蚀所述沟槽底部的外延层材料至第二深度,并热生长氧化物层附着在未被氮化物层覆盖的沟槽侧壁及底部;4)在所述沟槽下部填充第一导电材料,去除侧壁上的氮化物层,在所述第一导电材料表面制作一层隔离层;5)生长栅氧化层,覆盖于沟槽上部裸露的侧壁上,并在沟槽上部填充满第二导电材料,形成上

沟槽型MOSFET器件及其制造方法.pdf

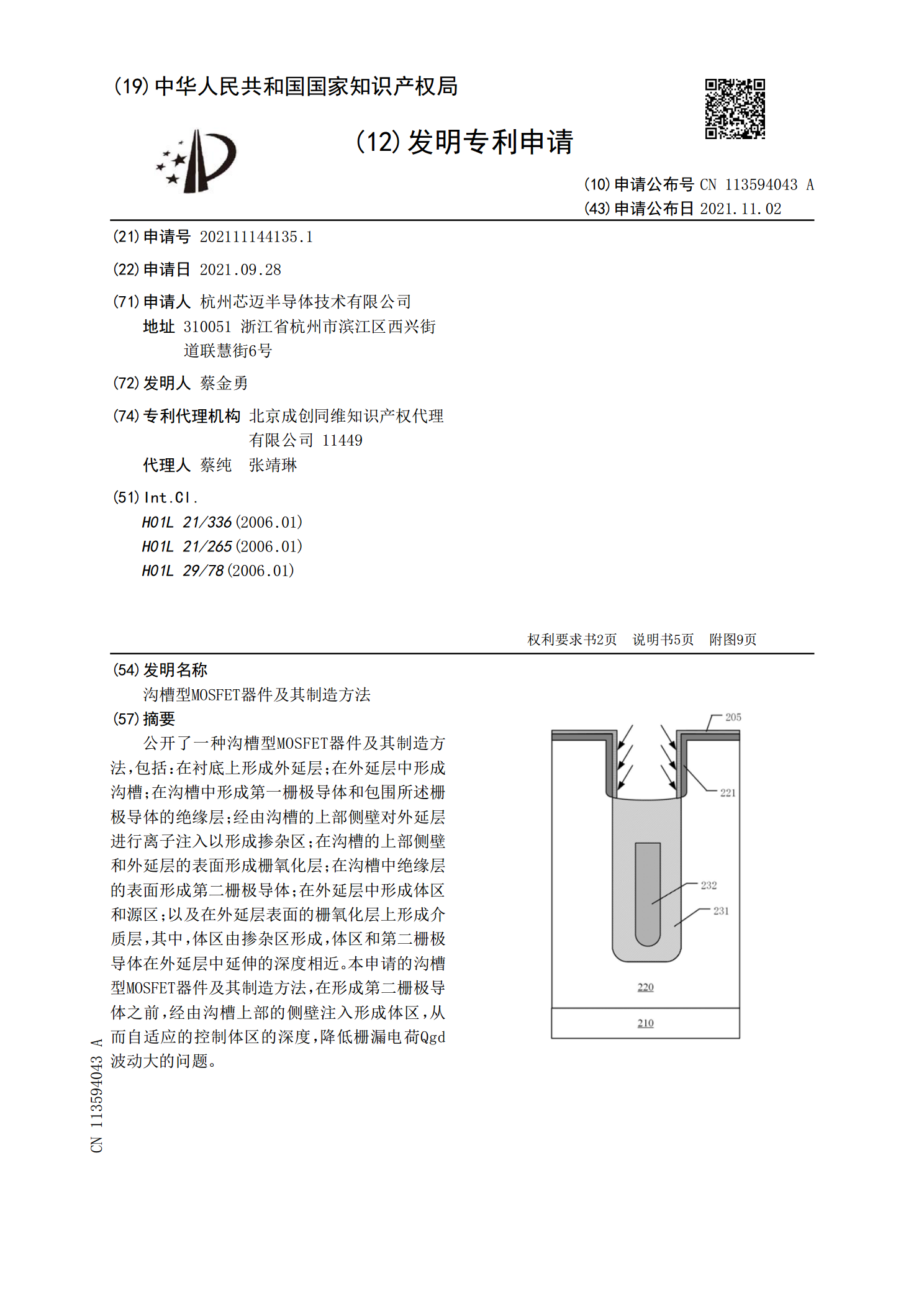

公开了一种沟槽型MOSFET器件及其制造方法,包括:在衬底上形成外延层;在外延层中形成沟槽;在沟槽中形成第一栅极导体和包围所述栅极导体的绝缘层;经由沟槽的上部侧壁对外延层进行离子注入以形成掺杂区;在沟槽的上部侧壁和外延层的表面形成栅氧化层;在沟槽中绝缘层的表面形成第二栅极导体;在外延层中形成体区和源区;以及在外延层表面的栅氧化层上形成介质层,其中,体区由掺杂区形成,体区和第二栅极导体在外延层中延伸的深度相近。本申请的沟槽型MOSFET器件及其制造方法,在形成第二栅极导体之前,经由沟槽上部的侧壁注入形成体区