阵列基板及包括该阵列基板的显示装置.pdf

书生****22

亲,该文档总共17页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

阵列基板及包括该阵列基板的显示装置.pdf

本申请涉及阵列基板及包括该阵列基板的显示装置。其中,用于显示装置的阵列基板包括:具有多个像素区域的基板;在基板上的多个栅极线,所述多个栅极线中的每个包括彼此间隔开的多个栅极图案;多个数据线,所述多个数据线与所述多个栅极线交叉以限定所述多个像素区域;以及连接所述多个栅极图案的第一连接图案,第一连接图案处于与所述多个栅极线不同的层。

阵列基板和包括该阵列基板的液晶显示装置.pdf

根据本公开内容,披露了一种阵列基板以及包括该阵列基板的液晶显示装置。第一电极与第二电极之间的保护层形成为双层,该双层包括作为高电阻率层的第一层和作为低电阻率层的第二层。因此,DC释放时间减少,从而在维持取向膜的高取向力的同时有效减少了残像。另外,第一电极与第二电极之间的保护层形成有具有高电阻率的第一层、具有低电阻率的第二层和具有高电阻率的第三层。因此,在维持高取向力的同时抑制了第一取向膜的界面的极化现象,从而有效减少了由于R‑DC而导致的残像。另外,防止了由于低电阻率层的形成而导致的灰度偏移的增加以及由于

阵列基板和包括阵列基板的显示装置.pdf

本发明公开了阵列基板和包括阵列基板的显示装置。阵列基板包括基板、基板上方的屏蔽金属和薄膜晶体管,该薄膜晶体管包括在屏蔽金属上方的具有沟道区域的有源层、以及在屏蔽金属、有源层和阵列基板中的至少一个中的热梯度部分,以使沟道区域的第一区域的温度低于沟道区域的第二区域的温度。在沟道区域与屏蔽金属之间的冷却带由热梯度部分限定。包括限定薄膜晶体管与屏蔽金属之间的冷却带的热梯度部分的阵列基板和包括该阵列基板的显示装置可以改善扭结效应、维持高驱动电压、增加导通电流和/或改善开关特性。

阵列基板和包括阵列基板的液晶显示装置.pdf

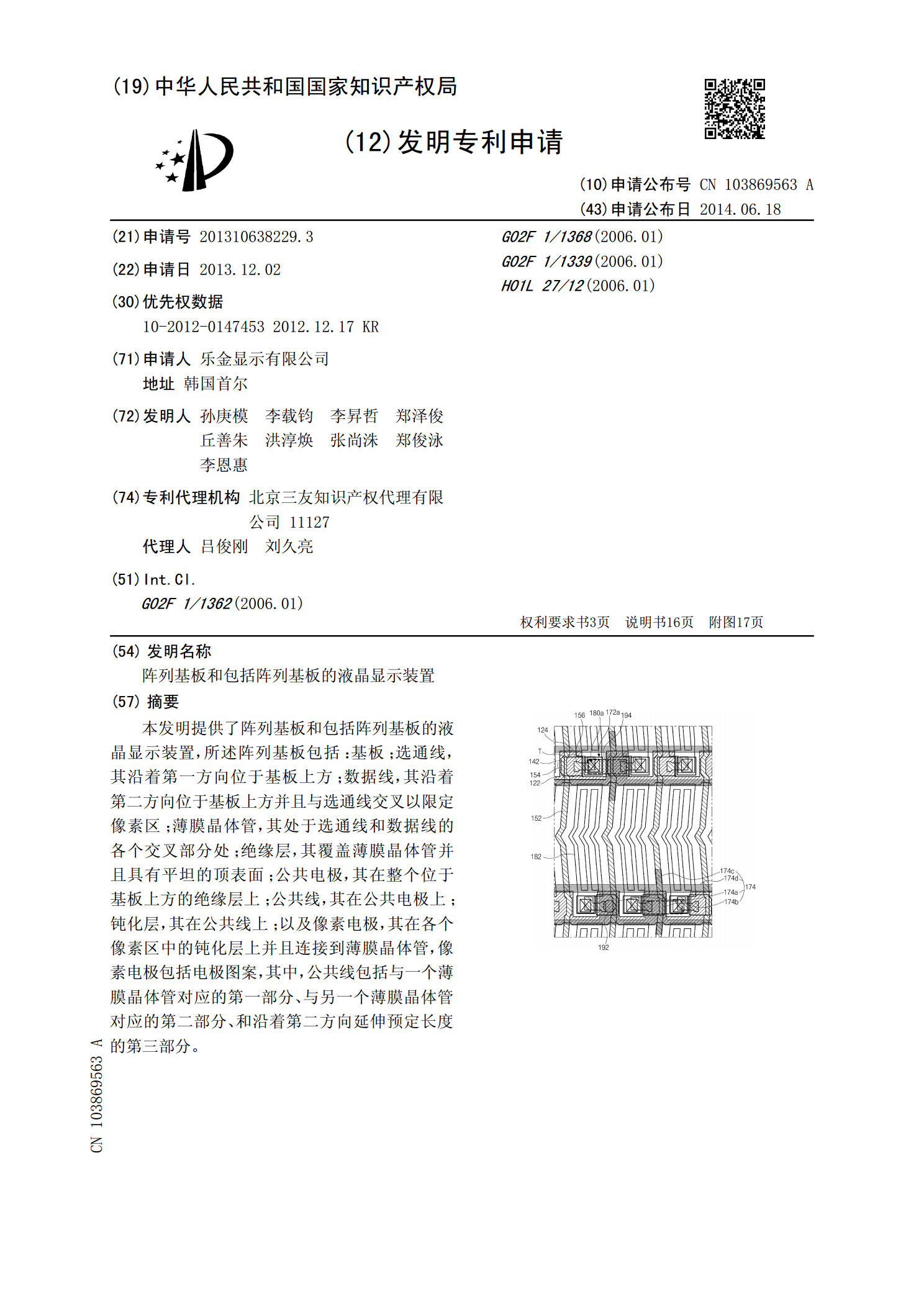

本发明提供了阵列基板和包括阵列基板的液晶显示装置,所述阵列基板包括:基板;选通线,其沿着第一方向位于基板上方;数据线,其沿着第二方向位于基板上方并且与选通线交叉以限定像素区;薄膜晶体管,其处于选通线和数据线的各个交叉部分处;绝缘层,其覆盖薄膜晶体管并且具有平坦的顶表面;公共电极,其在整个位于基板上方的绝缘层上;公共线,其在公共电极上;钝化层,其在公共线上;以及像素电极,其在各个像素区中的钝化层上并且连接到薄膜晶体管,像素电极包括电极图案,其中,公共线包括与一个薄膜晶体管对应的第一部分、与另一个薄膜晶体管对

阵列基板和包括其的显示装置.pdf

提供了一种阵列基板和包括其的显示装置。根据本公开的示范性实施例,如果有源区具有弯曲角部,则包括配置成补偿寄生电容的补偿单元。而且,被配置成与有源区的角部交叠的多条数据线,按照在数据线之间具有不同宽度的方式设置。因此,可以减小设置成与有源区的角部交叠的每条栅极线或数据线的寄生电容差异,也可以减小数据线之间的电阻差异。因此,在每条栅极线或数据线中,经由多条栅极线或数据线传送的信号的延迟程度相似,由此在显示图像中不会发生缺陷。