用于X射线探测器的阵列基板以及包括其的X射线探测器.pdf

甲申****66

亲,该文档总共14页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

用于X射线探测器的阵列基板以及包括其的X射线探测器.pdf

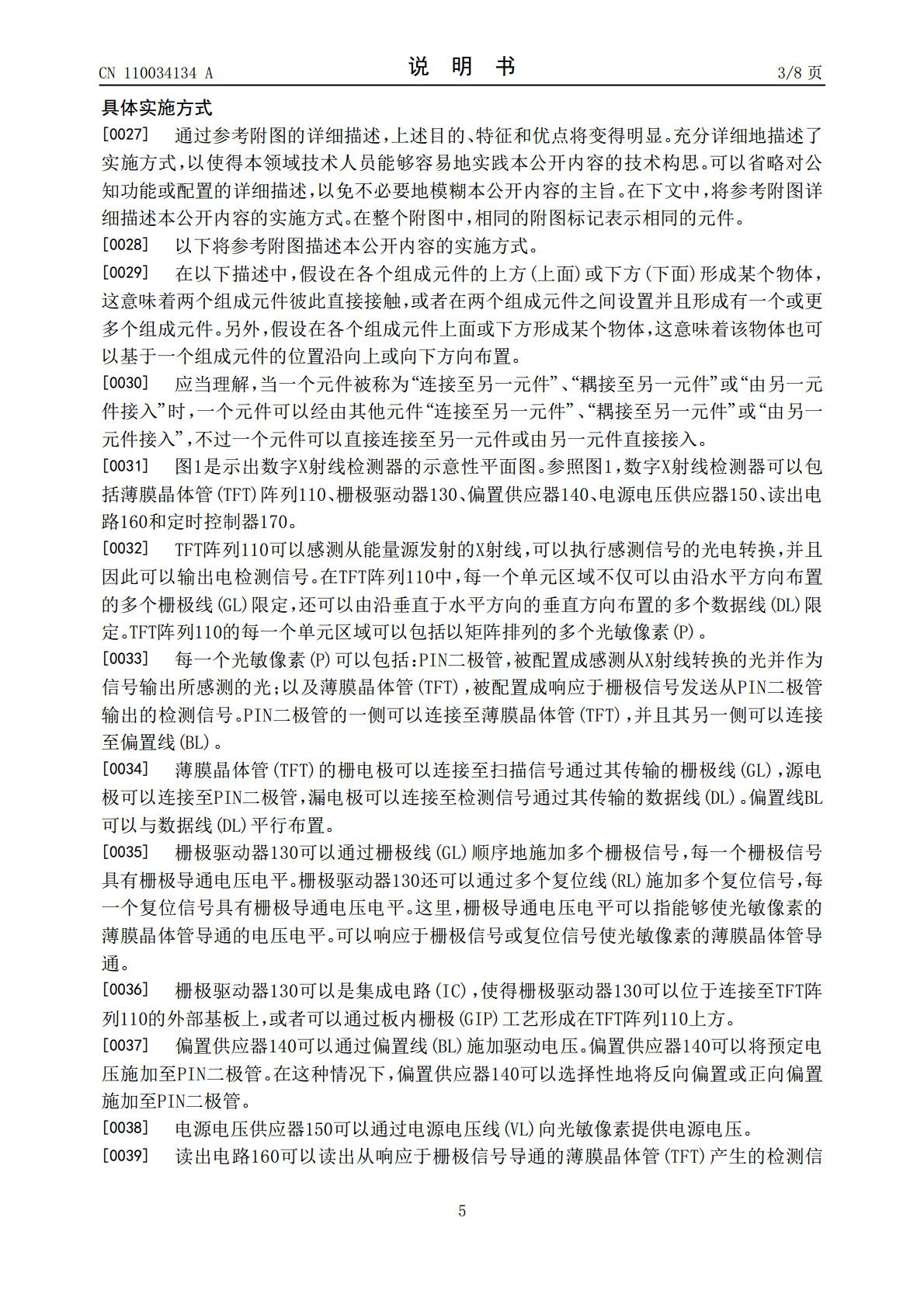

公开了一种用于X射线探测器的阵列基板和包括该阵列基板的X射线探测器,其使由PIN层的蚀刻引起的漏电流最小化,并且使PIN层在非像素区域内的光反应最小化。为此,用于X射线探测器的阵列基板包括形成为覆盖所有像素区域的集成PIN层。根据各个像素区域彼此间隔开的上电极设置在PIN层上方。遮光部分设置在相邻的上电极之间。

用于X射线检测器的阵列基板以及包括其的X射线检测器.pdf

本公开涉及用于X射线检测器的阵列基板以及包括其的X射线检测器。阵列基板限定为有源区和焊盘区,其中焊盘区包括多个测试区,测试区包括第一测试图案和第二测试图案。第一测试图案包括:在基板上的第一栅电极;在第一栅电极上的第一有源层;在第一有源层上的第一源/漏电极;以及在第一源/漏电极上的第一数据线,并且第二测试图案包括:在基板上的第一下电极,在第一下电极上的第一光电导层;以及在第一光电导层上的第一上电极,从而以高精度测量晶体管和光检测器中的每一个的特性。

用于X射线检测器的阵列基板以及包括其的X射线检测器.pdf

本公开涉及用于X射线检测器的阵列基板以及包括其的X射线检测器。阵列基板限定为有源区和焊盘区,其中焊盘区包括:基板,该基板包括第一区和从第一区延伸的第二区;以及接触基板的上表面并且从第一区朝向第二区延伸的多条数据线,多条数据线的相邻数据线彼此间隔开,基板的上表面在基板的第一区中的相邻数据线之间的区域露出;以及在基板与基板的第二区中的数据线之间设置有第一绝缘膜,从而防止切割期间由于数据线与有机层之间的团聚而导致相邻数据线之间的短路。

数字X射线检测器用阵列基板及包括其的X射线检测器.pdf

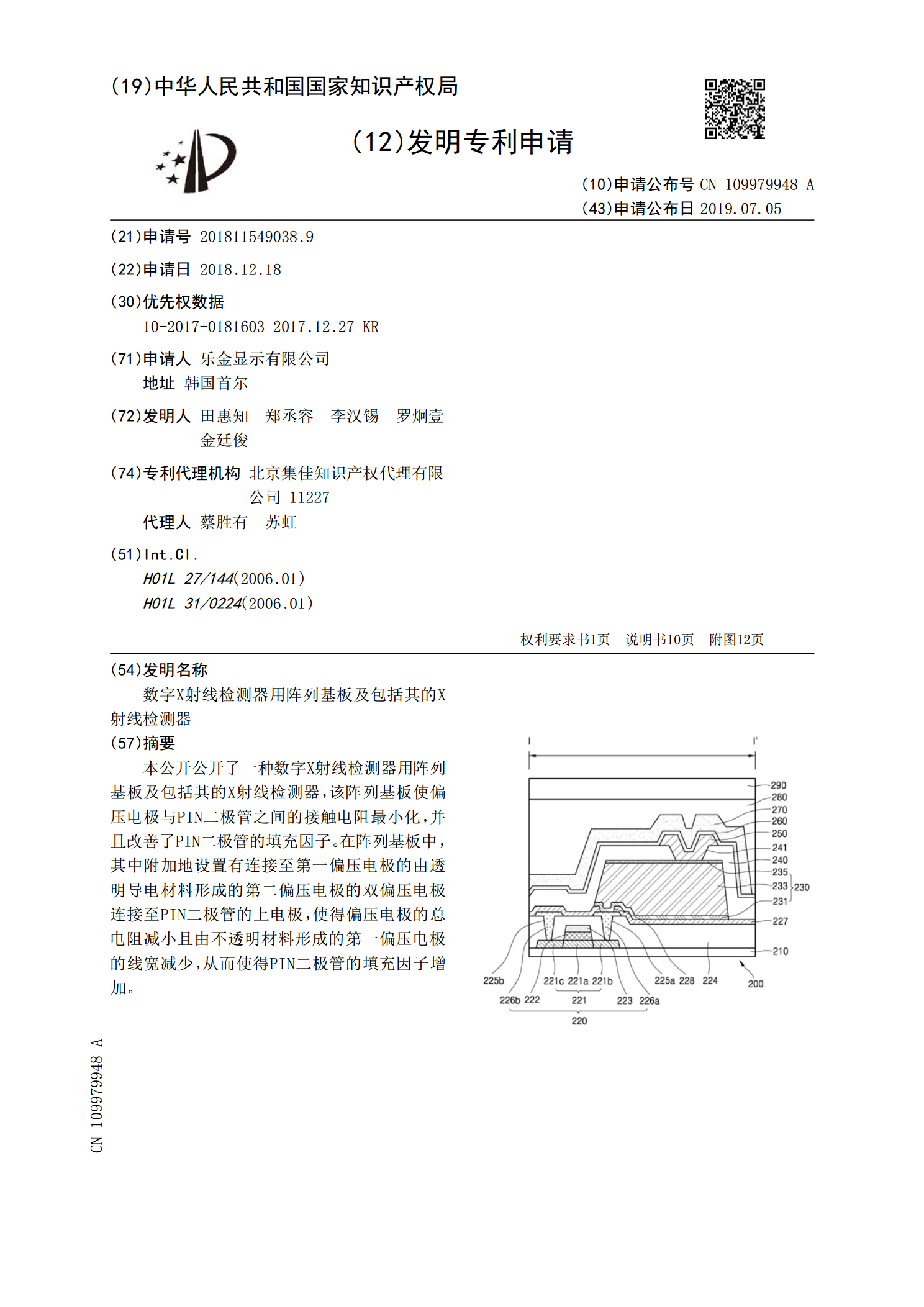

本公开公开了一种数字X射线检测器用阵列基板及包括其的X射线检测器,该阵列基板使偏压电极与PIN二极管之间的接触电阻最小化,并且改善了PIN二极管的填充因子。在阵列基板中,其中附加地设置有连接至第一偏压电极的由透明导电材料形成的第二偏压电极的双偏压电极连接至PIN二极管的上电极,使得偏压电极的总电阻减小且由不透明材料形成的第一偏压电极的线宽减少,从而使得PIN二极管的填充因子增加。

用于X射线检测的线阵列探测器技术的研究.pptx

汇报人:CONTENTSPARTONEPARTTWO研究背景研究目的和意义研究内容和方法PARTTHREE线阵列探测器的结构和工作原理X射线与物质的相互作用线阵列探测器的性能指标PARTFOUR医学影像诊断工业无损检测安全检查其他应用领域PARTFIVE线阵列探测器技术的优势线阵列探测器技术的挑战未来发展方向PARTSIX实验设备和方法实验结果与分析结果比较与讨论PARTSEVEN研究结论研究成果的应用前景对未来研究的建议汇报人: