互连结构的制造方法.pdf

是你****辉呀

亲,该文档总共11页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

互连结构的制造方法.pdf

一种互连结构的制造方法,包括:提供基底,在基底上形成具有第一开口的层间介质层,在第一开口内填充导电层形成第一互连结构,对导电层进行化学机械抛光至所述层间介质层,层间介质层表面具有化学机械抛光残留物;对层间介质层进行紫外线处理,去除层间介质层表面的所述残留物;对层间介质层进行紫外线处理后,在层间介质层上形成多孔介质层;在多孔介质层上形成图形化硬掩膜层,以图形化的硬掩膜层为掩膜刻蚀所述多孔介质层,在多孔介质层内形成第二开口,第二开口与第一开口相通,在第二开口内填充导电层形成第二互连结构。采用本发明的方法可以提

互连结构的制造方法.pdf

一种互连结构的制造方法,通过在干法刻蚀形成金属导线沟槽和湿法清洗金属导线沟槽中的刻蚀残留物之后,利用含氟的酸性溶液湿法清洗所形成金属导线沟槽开口处的氧化硅保护层和氮化钛硬掩模层,去除部分氧化硅和氮化钛,进而使得金属导线沟槽的氧化硅保护层和氮化钛硬掩模层开口宽度与氧化硅保护层下方的低介电常数介质层的开口宽度对应,改善了所形成的金属导线沟槽的形态,利于后续工艺中籽晶层和金属互连线的沉积,提高了所制造半导体器件的性能。

互连结构的制造方法.pdf

(19)中华人民共和国国家知识产权局(12)发明专利说明书(10)申请公布号CN101127320A(43)申请公布日2008.02.20(21)申请号CN200610030075.X(22)申请日2006.08.14(71)申请人中芯国际集成电路制造(上海)有限公司地址201203上海市浦东新区张江路18号(72)发明人杨小明蓝受龙高莺汪钉崇(74)专利代理机构北京集佳知识产权代理有限公司代理人逯长明(51)Int.CIH01L21/768H01L21/31权利要求说明书说明书幅图(54)发明名称互连结

中段互连结构及制造方法.pdf

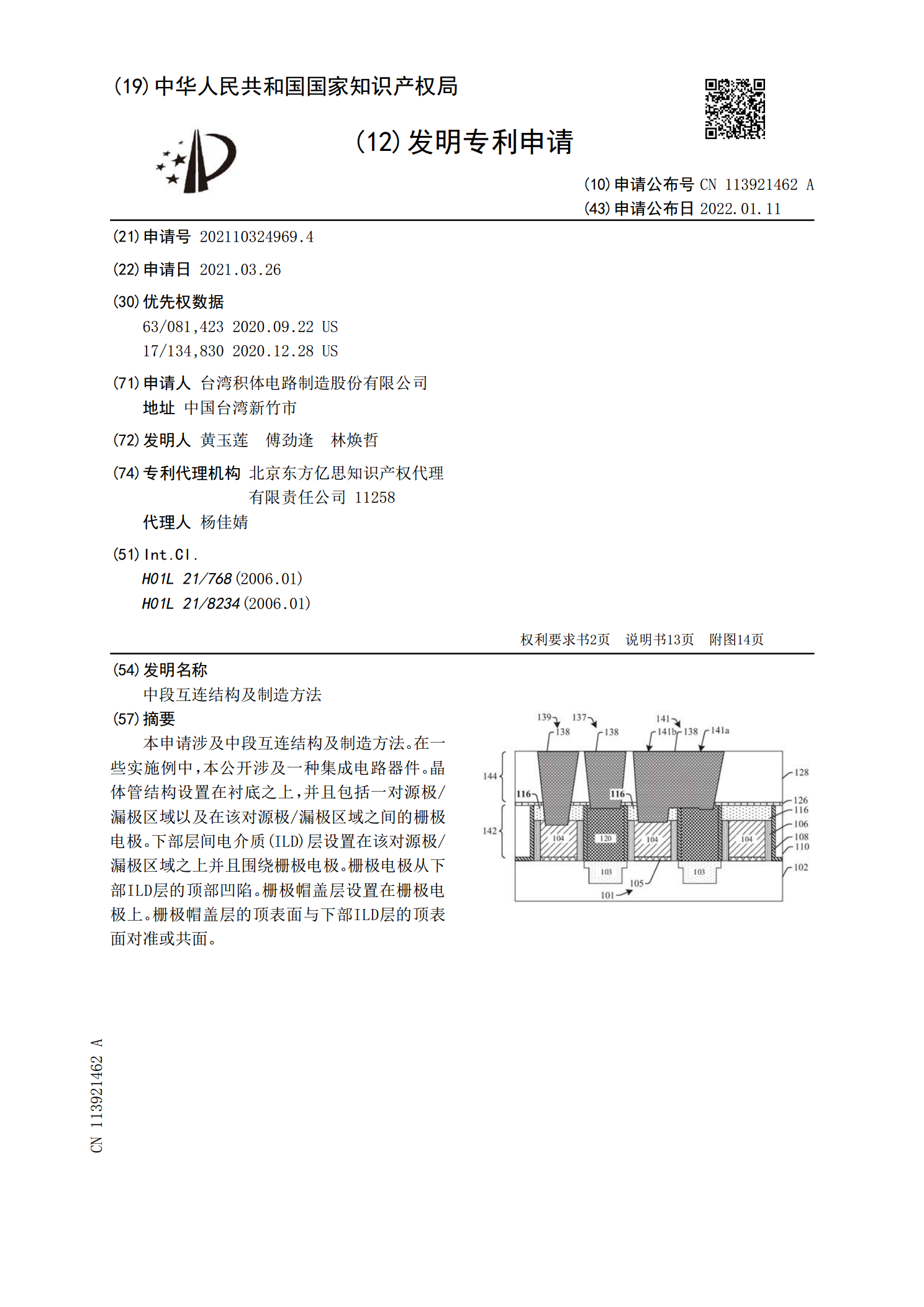

本申请涉及中段互连结构及制造方法。在一些实施例中,本公开涉及一种集成电路器件。晶体管结构设置在衬底之上,并且包括一对源极/漏极区域以及在该对源极/漏极区域之间的栅极电极。下部层间电介质(ILD)层设置在该对源极/漏极区域之上并且围绕栅极电极。栅极电极从下部ILD层的顶部凹陷。栅极帽盖层设置在栅极电极上。栅极帽盖层的顶表面与下部ILD层的顶表面对准或共面。

互连结构、具有互连结构的半导体器件及其制造方法.pdf

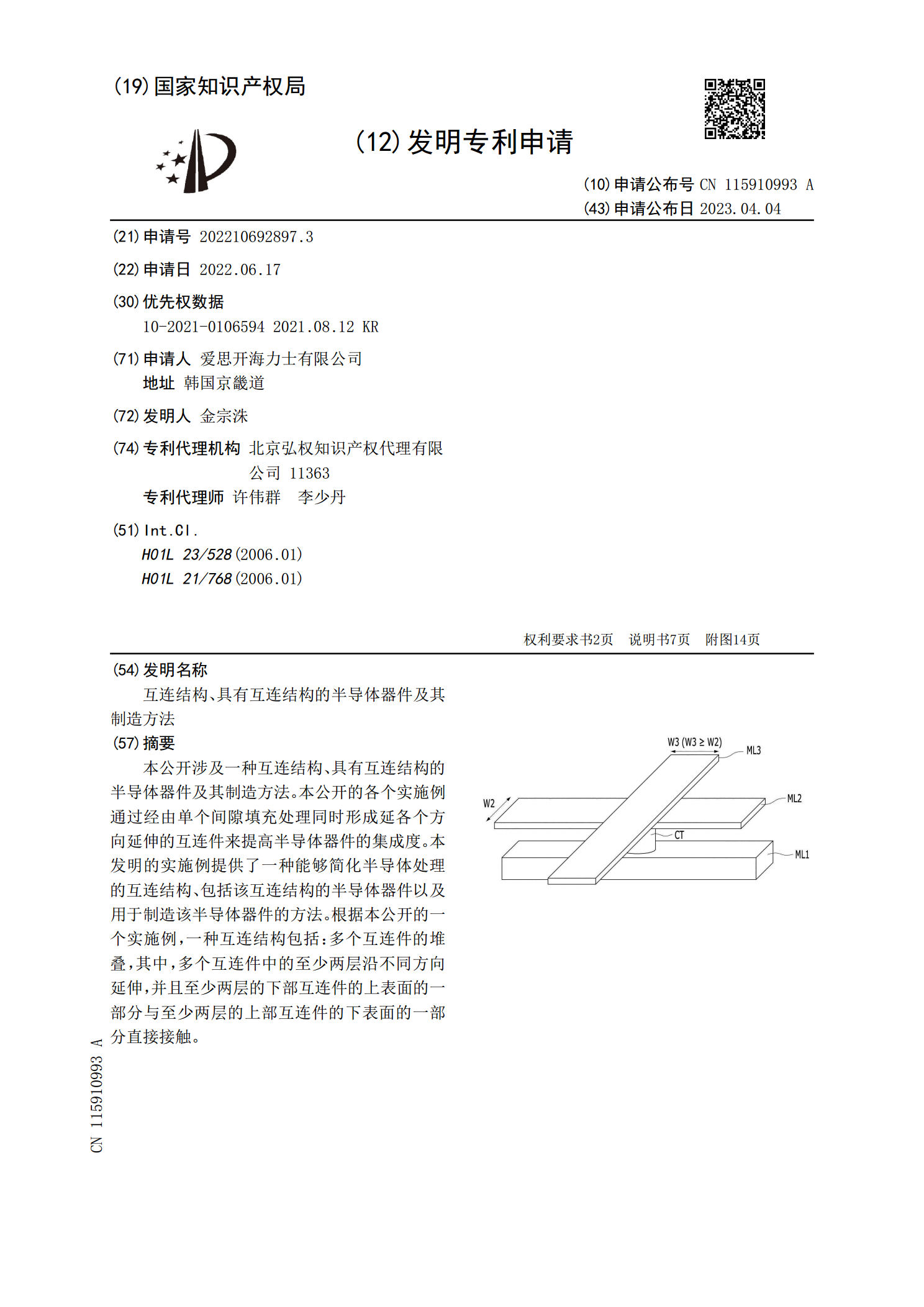

本公开涉及一种互连结构、具有互连结构的半导体器件及其制造方法。本公开的各个实施例通过经由单个间隙填充处理同时形成延各个方向延伸的互连件来提高半导体器件的集成度。本发明的实施例提供了一种能够简化半导体处理的互连结构、包括该互连结构的半导体器件以及用于制造该半导体器件的方法。根据本公开的一个实施例,一种互连结构包括:多个互连件的堆叠,其中,多个互连件中的至少两层沿不同方向延伸,并且至少两层的下部互连件的上表面的一部分与至少两层的上部互连件的下表面的一部分直接接触。