用于RFID标签的数据存留控制装置.pdf

一吃****春晓

亲,该文档总共12页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

用于RFID标签的数据存留控制装置.pdf

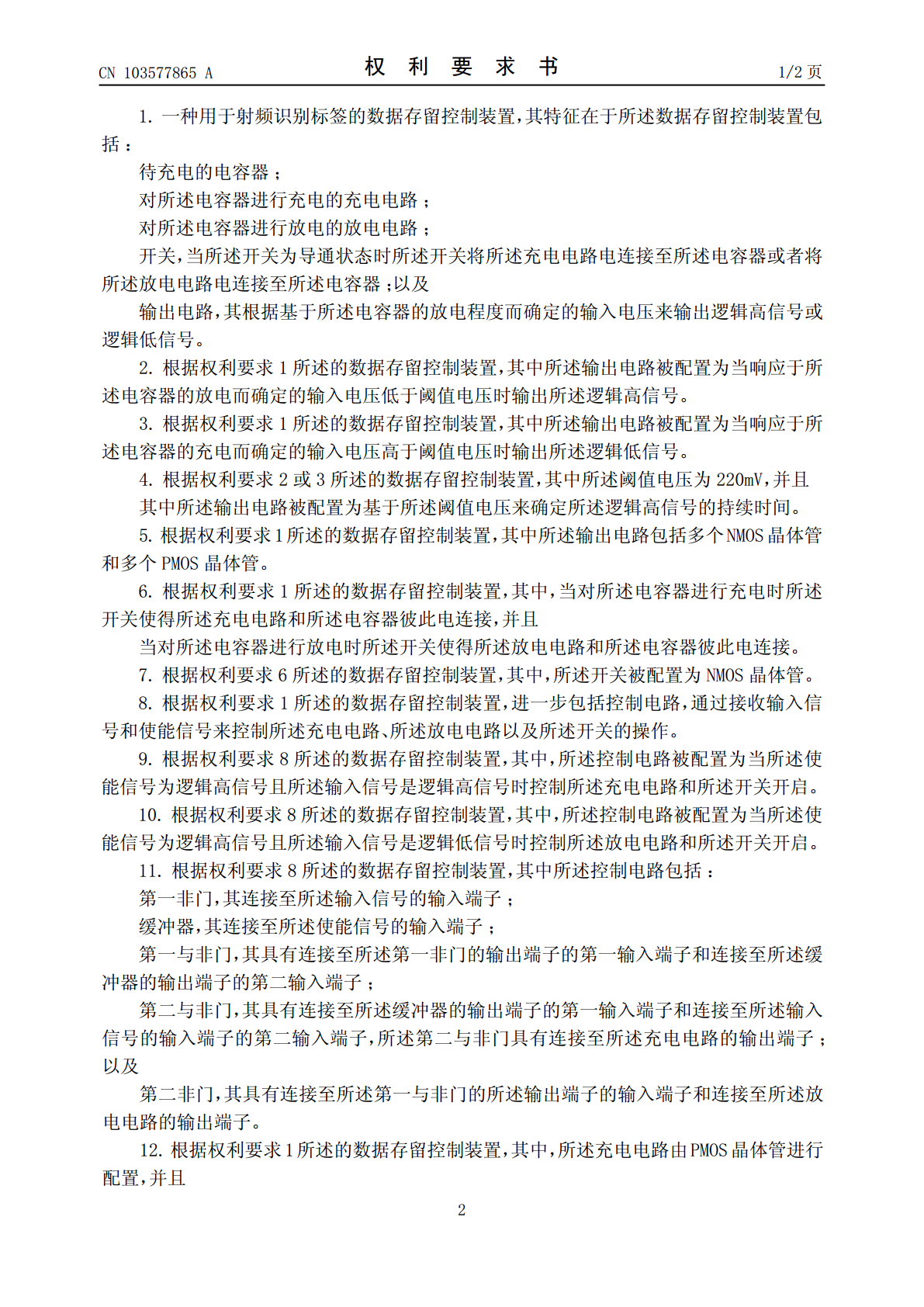

本发明提供了一种用于射频识别标签的数据存留控制装置。所述装置包括:待充电的电容器;对所述电容器进行充电的充电电路;对所述电容器进行放电的放电电路;开关,其接通以将所述充电电路电连接至所述电容器或者将所述放电电路电连接至所述电容器;以及输出电路,其根据基于所述电容器的放电程度所确定的输入电压来输出逻辑高信号或逻辑低信号。

用于查找RFID标签的方法和装置.pdf

一种蜂窝网络(40、51)将资源分配给装置(10),以便发送用于查找至少一个RFID标签(21‑26)的信号。装置(10)使用蜂窝网络(40、51)所分配的资源,以在被授权给蜂窝网络(40、51)的频带中向至少一个RFID标签(21‑26)发送信号。

用于定位RFID标签的方法、系统和装置.pdf

本发明题为“用于定位RFID标签的方法、系统和装置”。本文提供了一种用于确定RFID标签距离的RFID读取器系统和方法。所述RFID读取器响应于第一RF询问信号的发送接收来自RFID标签的第一反向散射信号,并所述确定第一反向散射信号的第一相位角。无线电收发器设备响应于第二RF询问信号的发送接收第二反向散射信号,并确定所述第二反向散射信号的第二相位角。主控制单元基于所述第一相位角和所述第二相位角确定所述RFID读取器与所述RFID标签之间的多个第一距离和第二距离,并且相对于所确定的第二距离选择所述多个第一距

用于打印的射频识别(RFID)标签的装置和方法.pdf

本发明涉及提供打印的射频识别(RFID)标签组件的装置和方法。在一个示例性实施例中,RFID标签组件包括衬底,衬底包括顶表面;和接收层,接收层包括具有导电特征的多个接收焊盘并且定位在衬底的顶表面上。RFID标签组件还可以包括定位在衬底的顶表面上的芯片。此外,RFID标签组件可以包括天线,天线被打印在接收层上,并且使用楔键合技术和球键合技术中的至少一个被接合到接收层。天线可以包括铜、铝、钯包覆的铜和铝包覆的铜引线或带中的至少一个。

RFID标签装置.pdf

本发明提供了一种RFID标签装置,包括:支撑件,其具有多面体结构;和设置于支撑件上的至少一个RFID标签回路,该至少一个RFID标签回路包括至少两个天线线圈,其中每个天线线圈均处于多面体结构的不同表面上。本发明的RFID标签装置有利于实现任意两个天线线圈在空间上呈一锐角或者钝角设置,避免任意两个天线线圈所在平面在空间上垂直或平行,进而可保证至少一个天线线圈与解读器的天线发射电磁波方向不垂直,能够有效避免信号盲区现象,提高标签的识读效率。