半导体器件的边角蚀刻方法.pdf

闪闪****魔王

亲,该文档总共12页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体器件的边角蚀刻方法.pdf

一种半导体器件的边角蚀刻方法,包括:提供包括器件区域以及位于器件区域周围的边角区域的衬底;在器件区域的衬底上形成半导体器件、第一层间介质层、第一导电插塞以及第二层间介质层,并在第二层间介质层中形成接触孔;对接触孔进行清洗;进行第一边角蚀刻,以去除边角区域的剩余的第二氧化物层;进行第二边角蚀刻,以去除边角区域的金属层,而保留第一氧化物层以及半导体层;本发明具有以下优点:能够较为快速的去除晶圆的边角区域上的第二氧化物层,以将所述第二氧化物层下方的金属层暴露出来;较为完整地保留在所述边角区域,使得在后续形成导电

蚀刻液、氧化物半导体器件及蚀刻方法.pdf

本申请公开了一种蚀刻液、氧化物半导体器件及蚀刻方法,应用于蚀刻氧化物半导体器件,该蚀刻液包括在蚀刻液中的质量百分比为12%至25%的氧化剂、在蚀刻液中的质量百分比为0.5%至3%的螯合剂、在蚀刻液中的质量百分比为0.5%至5%的蚀刻剂、在蚀刻液中的质量百分比为0.01%至2%的腐蚀抑制剂、在蚀刻液中的质量百分比为0.01%至2%辅助蚀刻剂、以及余量的水性介质;本申请的蚀刻液不含氟元素以及蚀刻液中辅助蚀刻剂的增加,在保证氧化物半导体层不受损的情况下,辅助蚀刻剂可以对钼系金属的尾缘及其尖端的残渣作进一步蚀刻,

半导体元器件的干蚀刻方法.pdf

本发明中公开了一种半导体元器件的干蚀刻方法,该方法包括:在硅基底材料上依次形成SiO2层、低介电常数绝缘材料层、顶层、含Si的底部抗反射层和光阻层;对含Si的底部抗反射层和光阻层进行蚀刻后,对顶层和低介电常数绝缘材料层进行蚀刻,并去除蚀刻过程中产生的残留物;对由于进行所述蚀刻后而暴露出的顶层进行氟气处理,使得在对顶层进行蚀刻的同时不对顶层之下的低介电常数材料进行蚀刻;去除对顶层进行蚀刻时所产生的残留物。通过使用上述的半导体元器件的干蚀刻方法,解决了顶部收缩和弓形轮廓的问题,使得所形成的顶层具有较好的轮廓,

一种半导体器件介质层蚀刻方法.pdf

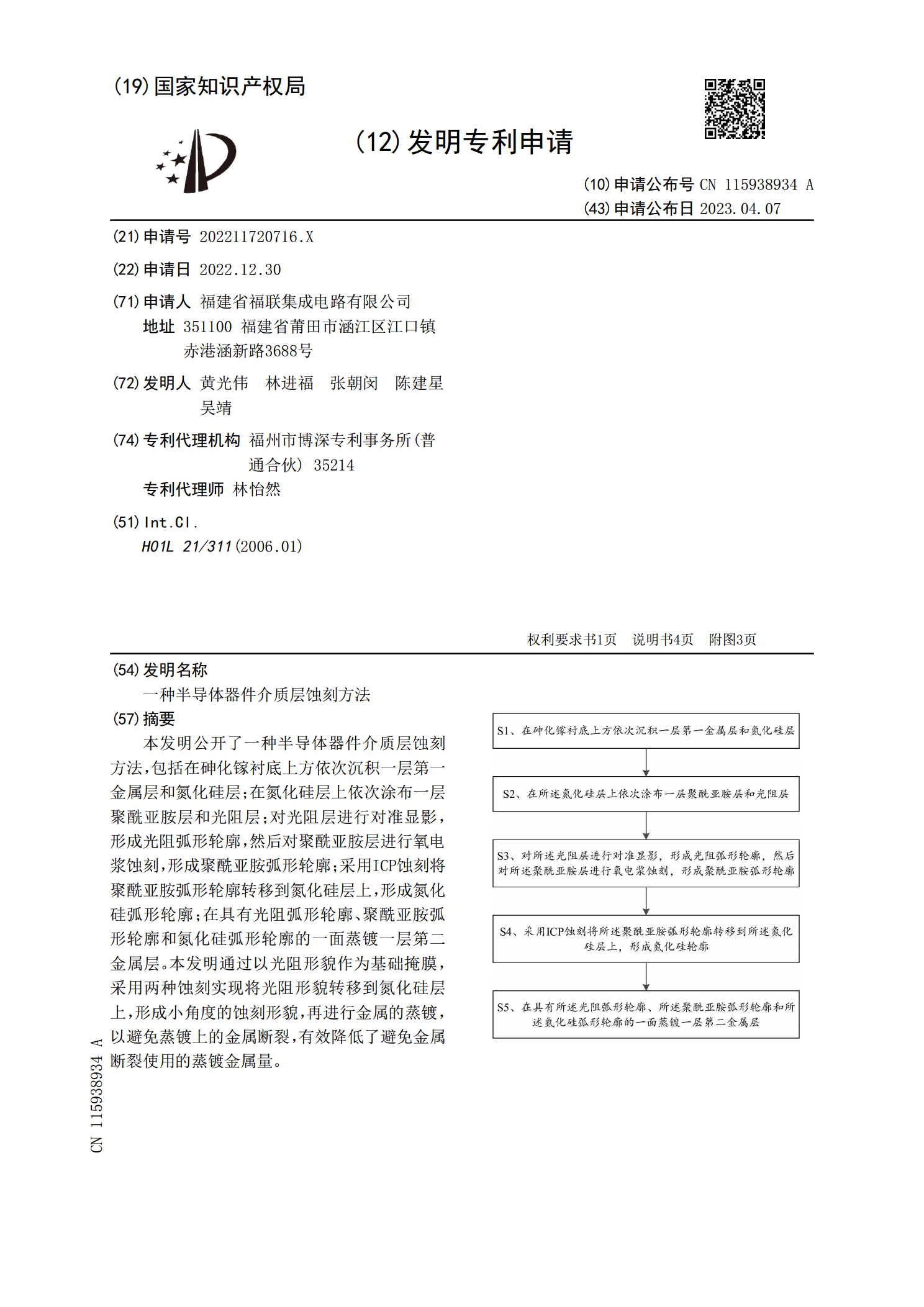

本发明公开了一种半导体器件介质层蚀刻方法,包括在砷化镓衬底上方依次沉积一层第一金属层和氮化硅层;在氮化硅层上依次涂布一层聚酰亚胺层和光阻层;对光阻层进行对准显影,形成光阻弧形轮廓,然后对聚酰亚胺层进行氧电浆蚀刻,形成聚酰亚胺弧形轮廓;采用ICP蚀刻将聚酰亚胺弧形轮廓转移到氮化硅层上,形成氮化硅弧形轮廓;在具有光阻弧形轮廓、聚酰亚胺弧形轮廓和氮化硅弧形轮廓的一面蒸镀一层第二金属层。本发明通过以光阻形貌作为基础掩膜,采用两种蚀刻实现将光阻形貌转移到氮化硅层上,形成小角度的蚀刻形貌,再进行金属的蒸镀,以避免蒸镀

半导体器件制造方法及半导体器件.pdf

本发明公开了一种半导体器件制造方法及半导体器件。该方法在相邻MOS晶体管之间的沟槽底部预留间隔层,通过该间隔层改变沟槽底部的深宽比,不仅有效避免了在沟槽底部容易造成第二层多晶硅残余的问题,防止相邻两个MOS晶体管之间因沟槽底部有第二侧层多晶硅残余而导致半导体器件内部发生短路现象;而且采用本半导体器件制造方法也不会破坏第二层多晶硅的结构。与现有技术相比较,本半导体器件制造方法优化了工艺过程,增加了第二侧层多晶硅蚀刻的工艺窗口,提升了半导体器件的质量。