三维存储器件的擦除方法.pdf

文光****iu

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

三维存储器件的擦除方法.pdf

一种三维存储器件擦除方法,包括:步骤1、接收擦除命令;步骤2、判定存储块是否被选中,是则执行步骤3,否则执行步骤4;步骤3、执行奇偶字线交替擦除,随后执行步骤5;步骤4、浮置未选中存储块的所有字线,随后结束;步骤5、验证存储块是否擦除成功,是则结束,否则执行步骤3。依照本发明的三维半导体存储器件擦除方法,使得奇数字线和偶数字线交替选通/浮置,横向电场抑制擦除空穴的移动,使得存储层中电子能够被完全擦除而没有空穴残留,避免了器件失效。

三维存储器件及其制造方法.pdf

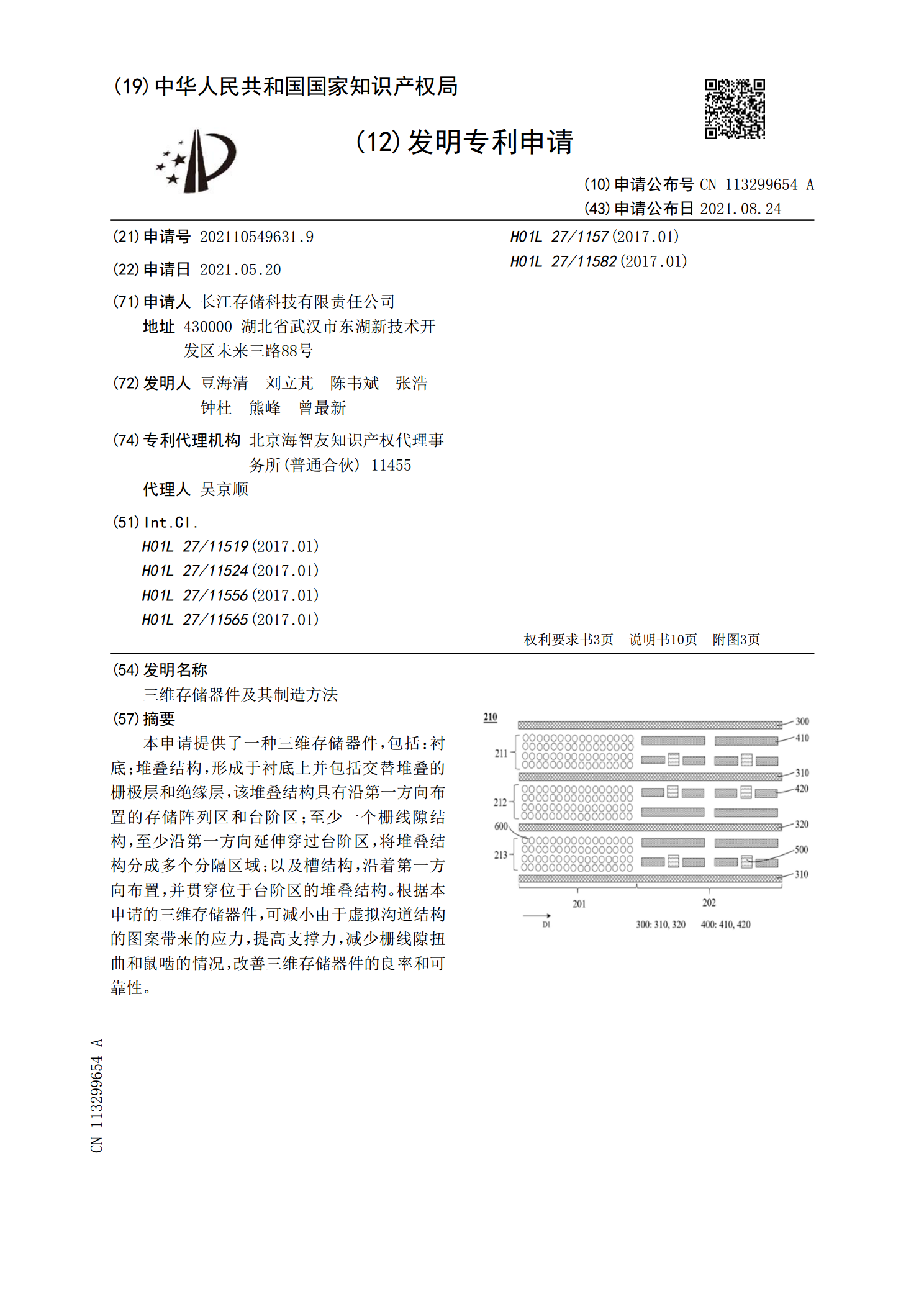

本申请提供了一种三维存储器件,包括:衬底;堆叠结构,形成于衬底上并包括交替堆叠的栅极层和绝缘层,该堆叠结构具有沿第一方向布置的存储阵列区和台阶区;至少一个栅线隙结构,至少沿第一方向延伸穿过台阶区,将堆叠结构分成多个分隔区域;以及槽结构,沿着第一方向布置,并贯穿位于台阶区的堆叠结构。根据本申请的三维存储器件,可减小由于虚拟沟道结构的图案带来的应力,提高支撑力,减少栅线隙扭曲和鼠啮的情况,改善三维存储器件的良率和可靠性。

三维存储器件及其制造方法.pdf

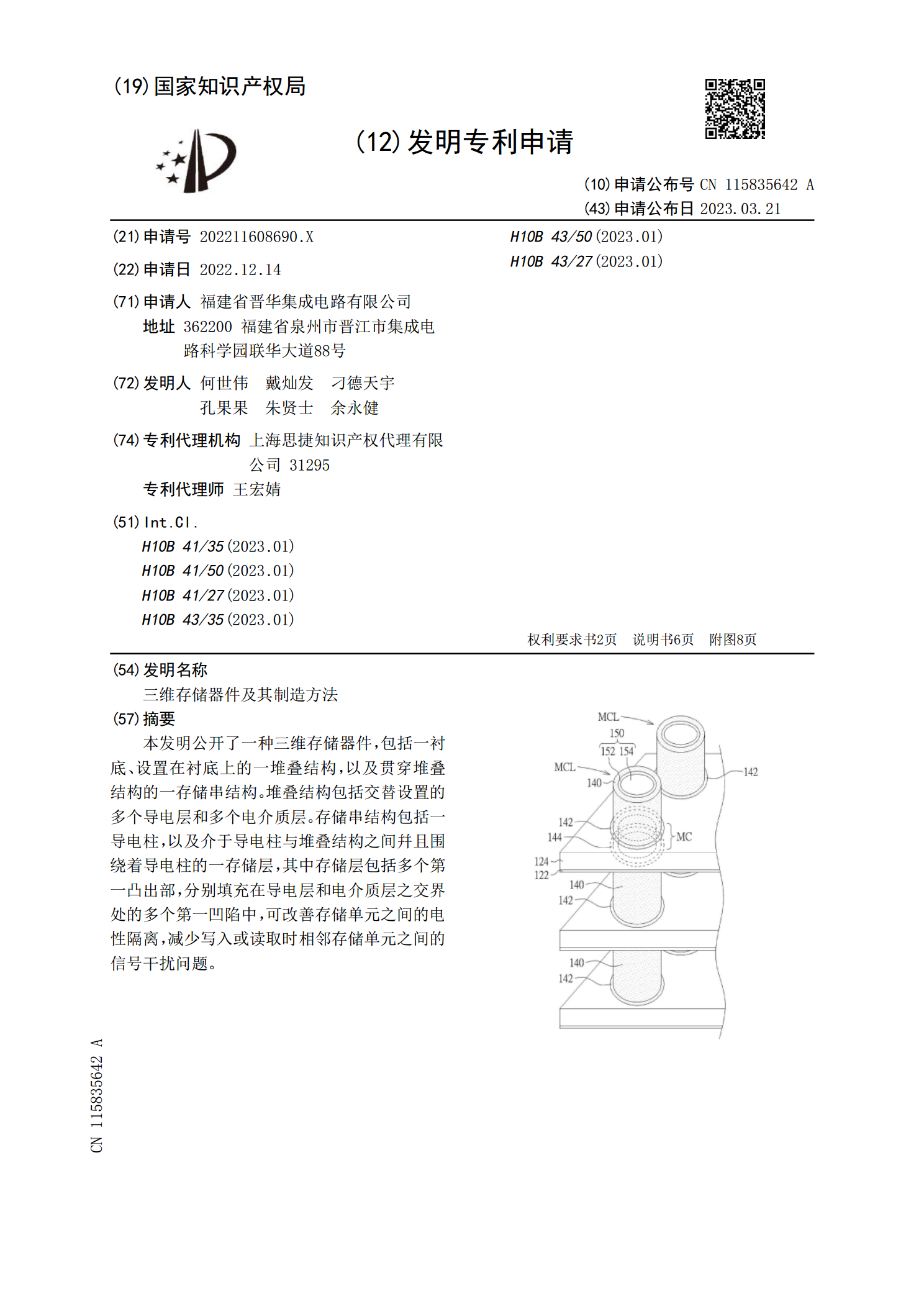

本发明公开了一种三维存储器件,包括一衬底、设置在衬底上的一堆叠结构,以及贯穿堆叠结构的一存储串结构。堆叠结构包括交替设置的多个导电层和多个电介质层。存储串结构包括一导电柱,以及介于导电柱与堆叠结构之间幷且围绕着导电柱的一存储层,其中存储层包括多个第一凸出部,分别填充在导电层和电介质层之交界处的多个第一凹陷中,可改善存储单元之间的电性隔离,减少写入或读取时相邻存储单元之间的信号干扰问题。

三维存储器件及其制作方法.pdf

本发明公开了三维存储器件及其制作方法,包括衬底以及存储堆叠结构。存储堆叠结构设置在衬底上,包括多个堆叠单元由下而上依序堆叠成阶梯状,其中,各堆叠单元具有阶梯斜率,任一设置于下方的堆叠单元的阶梯斜率的斜率大于任一设置于上方的堆叠单元的所述阶梯斜率。由此,可优化三维存储器件的结构完整性,进而提升其组件效能。

三维存储器件.pdf

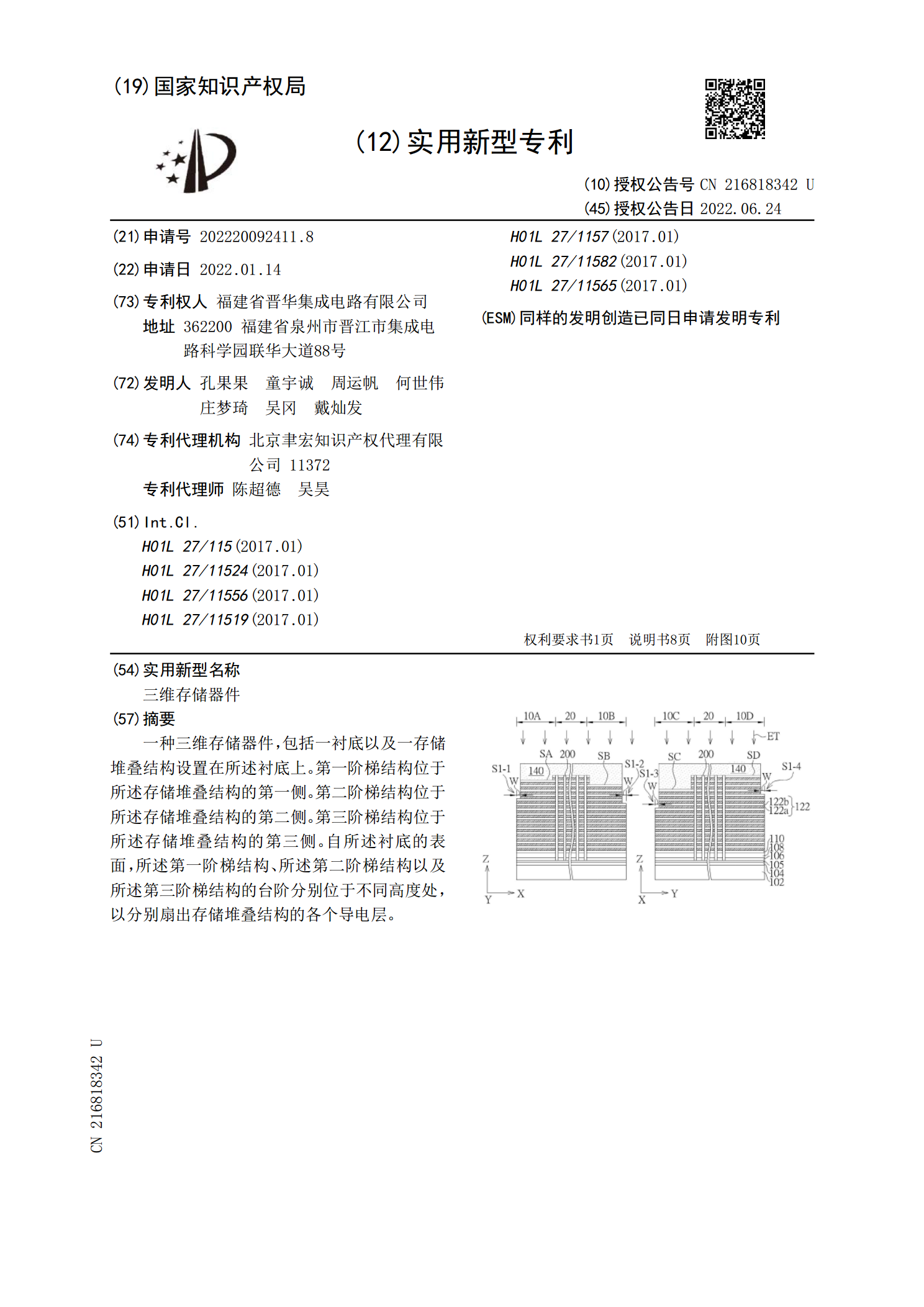

一种三维存储器件,包括一衬底以及一存储堆叠结构设置在所述衬底上。第一阶梯结构位于所述存储堆叠结构的第一侧。第二阶梯结构位于所述存储堆叠结构的第二侧。第三阶梯结构位于所述存储堆叠结构的第三侧。自所述衬底的表面,所述第一阶梯结构、所述第二阶梯结构以及所述第三阶梯结构的台阶分别位于不同高度处,以分别扇出存储堆叠结构的各个导电层。