电解质、形成铜层的方法以及形成芯片的方法.pdf

是你****辉呀

亲,该文档总共36页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

电解质、形成铜层的方法以及形成芯片的方法.pdf

本发明涉及一种电解质。该电解质可以包括至少一种配置为在温度超过大约100℃时分解或蒸发的添加剂和一种水溶性金属盐,并且所述电解质不含有碳纳米管。本发明还涉及提供一种形成金属层的方法,该方法可以包括使用电解质在载体上沉积金属层,其中该电解质可以包括至少一种配置为在温度超过大约100℃时分解或蒸发的添加剂和一种水溶性金属盐,其中所述电解质不含有碳纳米管;以及对金属层退火以形成含有多个孔的金属层。本发明还涉及一种半导体器件,该半导体器件可以包括包含多个孔的金属层,其中所述多个孔可以形成在金属层中,同时添加剂的残

层结构、芯片封装体以及它们的形成方法和焊料材料.pdf

提供了一种焊料材料。所述焊料材料可以包括具有形成第一尺寸分布的颗粒尺寸的第一量的颗粒;具有形成第二尺寸分布的颗粒尺寸的第二量的颗粒,其中,所述第二尺寸分布的颗粒尺寸大于所述第一尺寸分布的颗粒尺寸;以及其中分布有所述第一量的颗粒和所述第二量的颗粒的焊料基底材料,其中,所述第一量的颗粒和所述第二量的颗粒由或基本上由第一组金属中的金属组成,所述第一组金属包括铜、银、金、钯、铂、铁、钴和铝,所述焊料基底材料包括第二组金属中的金属,所述第二组金属包括锡、铟、锌、镓、锗、锑和铋。

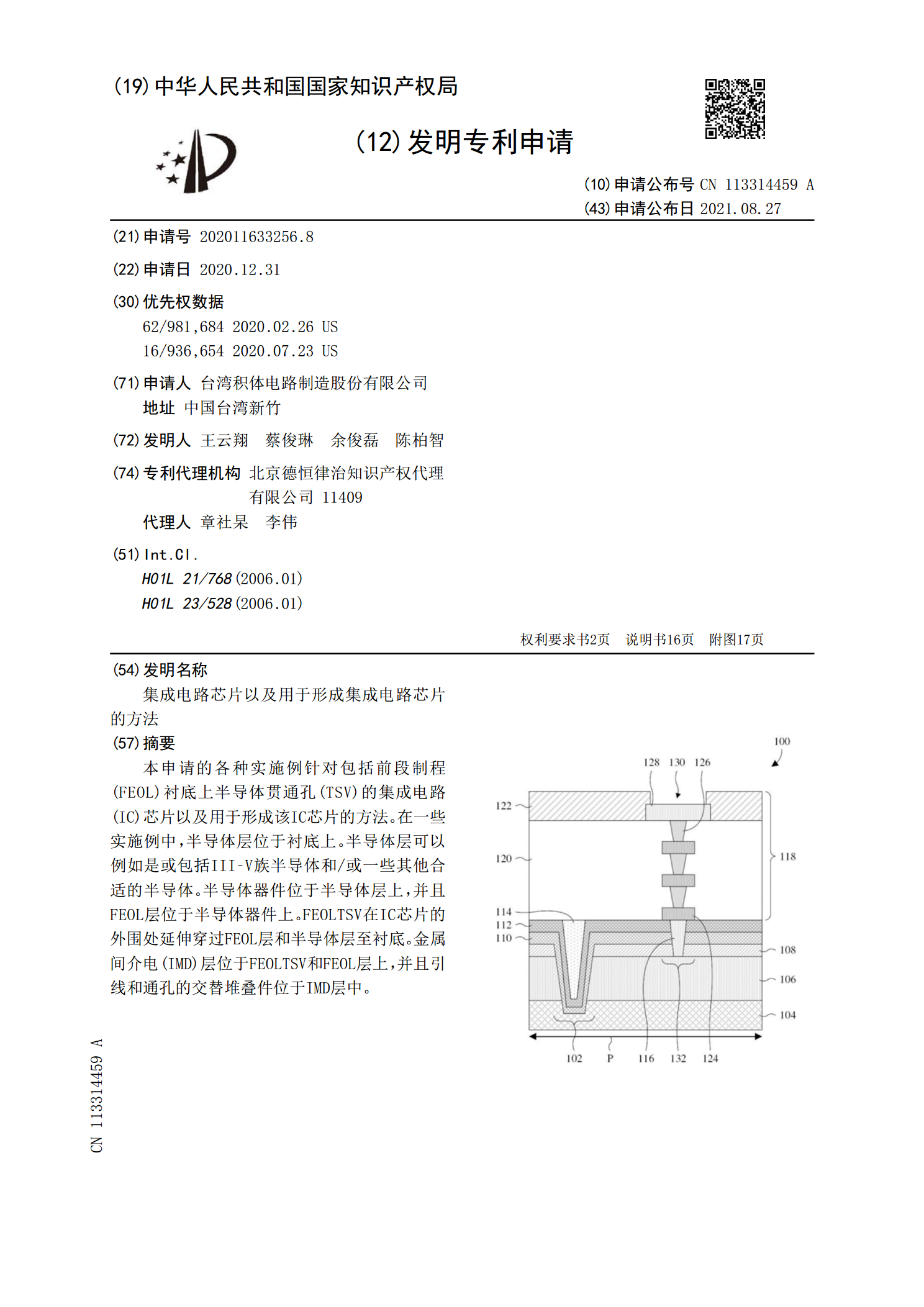

集成电路芯片以及用于形成集成电路芯片的方法.pdf

本申请的各种实施例针对包括前段制程(FEOL)衬底上半导体贯通孔(TSV)的集成电路(IC)芯片以及用于形成该IC芯片的方法。在一些实施例中,半导体层位于衬底上。半导体层可以例如是或包括III‑V族半导体和/或一些其他合适的半导体。半导体器件位于半导体层上,并且FEOL层位于半导体器件上。FEOLTSV在IC芯片的外围处延伸穿过FEOL层和半导体层至衬底。金属间介电(IMD)层位于FEOLTSV和FEOL层上,并且引线和通孔的交替堆叠件位于IMD层中。

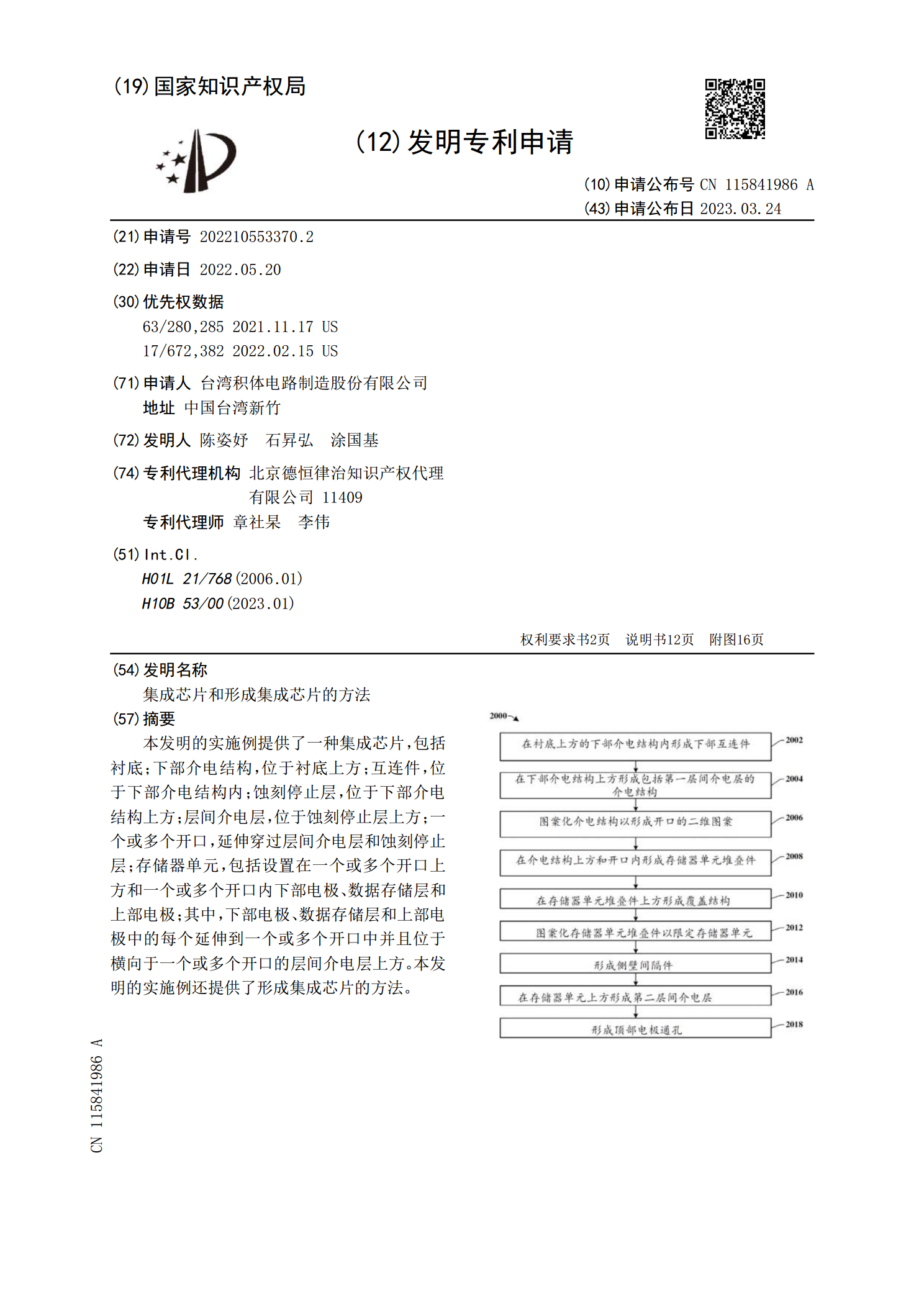

集成芯片和形成集成芯片的方法.pdf

本发明的实施例提供了一种集成芯片,包括衬底;下部介电结构,位于衬底上方;互连件,位于下部介电结构内;蚀刻停止层,位于下部介电结构上方;层间介电层,位于蚀刻停止层上方;一个或多个开口,延伸穿过层间介电层和蚀刻停止层;存储器单元,包括设置在一个或多个开口上方和一个或多个开口内下部电极、数据存储层和上部电极;其中,下部电极、数据存储层和上部电极中的每个延伸到一个或多个开口中并且位于横向于一个或多个开口的层间介电层上方。本发明的实施例还提供了形成集成芯片的方法。

蚀刻液、补给液以及铜布线的形成方法.pdf

本发明涉及蚀刻液、补给液以及铜布线的形成方法。本发明提供一种能够抑制侧向蚀刻且提高铜布线的线性、并且能够抑制未蚀刻部分的残留的蚀刻液、其补给液以及铜布线的形成方法。本发明的蚀刻液,其特征在于,是铜的蚀刻液,是含有酸、二价铜离子、唑化合物以及脂环式胺化合物的水溶液。本发明的补给液,其特征在于,是连续或反复使用上述本发明的蚀刻液时向上述蚀刻液中添加的补给液,是含有酸、唑化合物以及脂环式胺化合物的水溶液。本发明的铜布线(1)的形成方法,其特征在于,是对铜层的未被抗蚀剂(2)覆盖的部分进行蚀刻的铜布线(1)的形成