半导体器件制作方法、半导体器件及电子装置.pdf

羽沫****魔王

亲,该文档总共15页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体器件制作方法、半导体器件及电子装置.pdf

本发明提供一种半导体器件的制作方法,其包括:提供半导体衬底,在半导体衬底上形成栅极堆栈,并在所述栅极堆栈四周形成间隙壁;进行局部曝光,以定义要进行局部互连的栅极区域;形成覆盖所述栅极堆栈和间隙壁的光刻胶层,并对所述光刻胶层进行局部刻蚀以去除要进行局部互连的栅极区域内的间隙壁;在半导体衬底和栅极堆栈上沉积多晶硅膜层;刻蚀多晶硅膜层,以保留用于局部互连的多晶硅膜层,并去述多晶硅膜层的其余部分,其中,沿栅极堆栈方向,要进行局部互连的区域相对用于局部互连的多晶硅膜层具有一定延伸;在露出的部分栅极堆栈上形成硅化物,

半导体器件及其制作方法、电子装置.pdf

本发明提供一种半导体器件及其制作方法、电子装置,该制作方法包括:提供半导体衬底,所述半导体衬底包括密集区和稀疏区,在所述半导体衬底上形成有栅极叠层,所述栅极叠层包括浮栅、栅极介电层、控制栅和控制栅硬掩膜层;对所述半导体衬底密集区中的栅极叠层进行图形化以形成位于所述密集区的字线;对所述半导体衬底稀疏区中的栅极叠层进行图形化,以形成位于所述稀疏区的选择栅。该制作方法可以获得更好的器件性能和器件轮廓。该半导体器件和电子装置由于上述制作方法使得性能和良率提高。

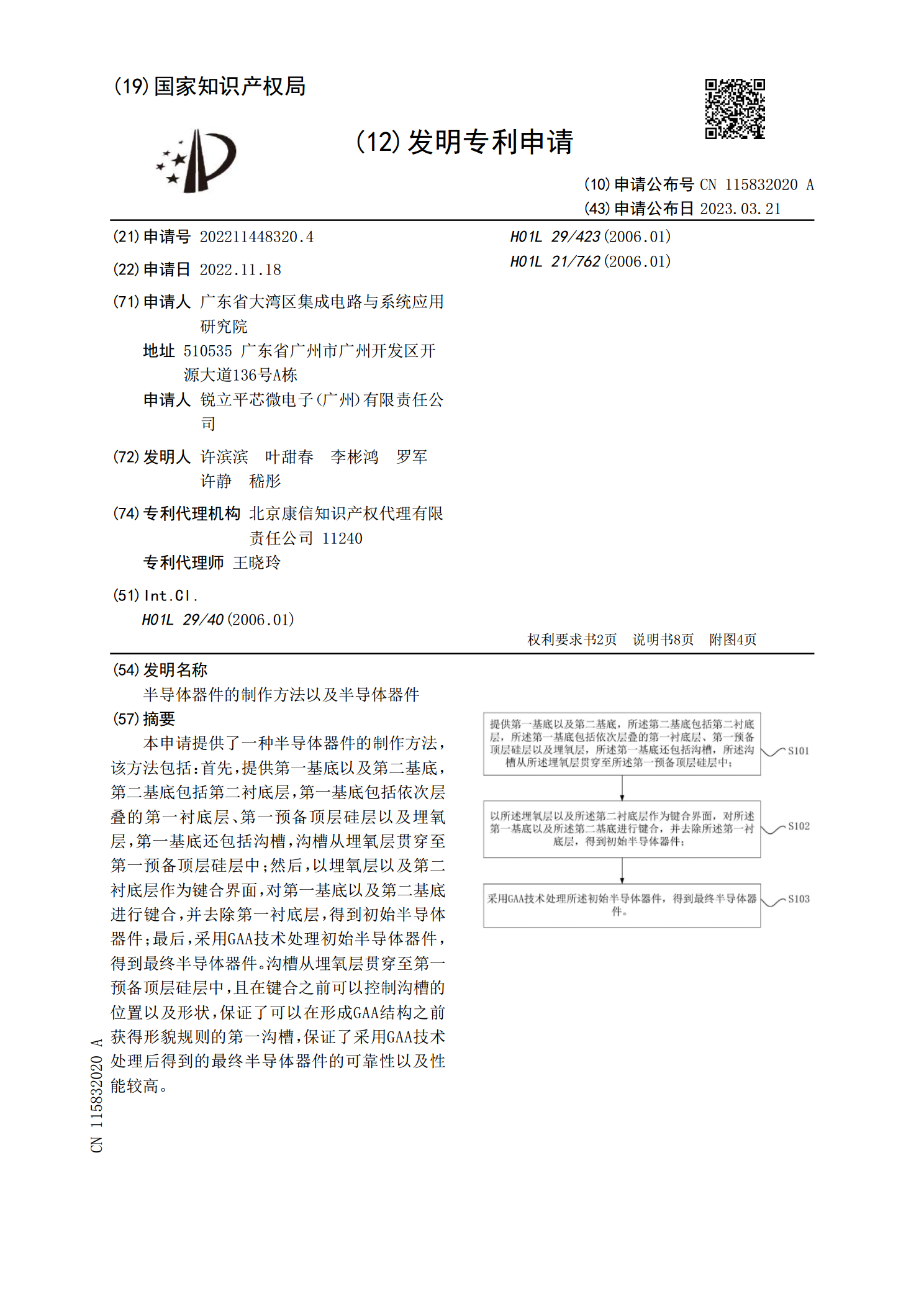

半导体器件的制作方法以及半导体器件.pdf

本申请提供了一种半导体器件的制作方法,该方法包括:首先,提供第一基底以及第二基底,第二基底包括第二衬底层,第一基底包括依次层叠的第一衬底层、第一预备顶层硅层以及埋氧层,第一基底还包括沟槽,沟槽从埋氧层贯穿至第一预备顶层硅层中;然后,以埋氧层以及第二衬底层作为键合界面,对第一基底以及第二基底进行键合,并去除第一衬底层,得到初始半导体器件;最后,采用GAA技术处理初始半导体器件,得到最终半导体器件。沟槽从埋氧层贯穿至第一预备顶层硅层中,且在键合之前可以控制沟槽的位置以及形状,保证了可以在形成GAA结构之前获得

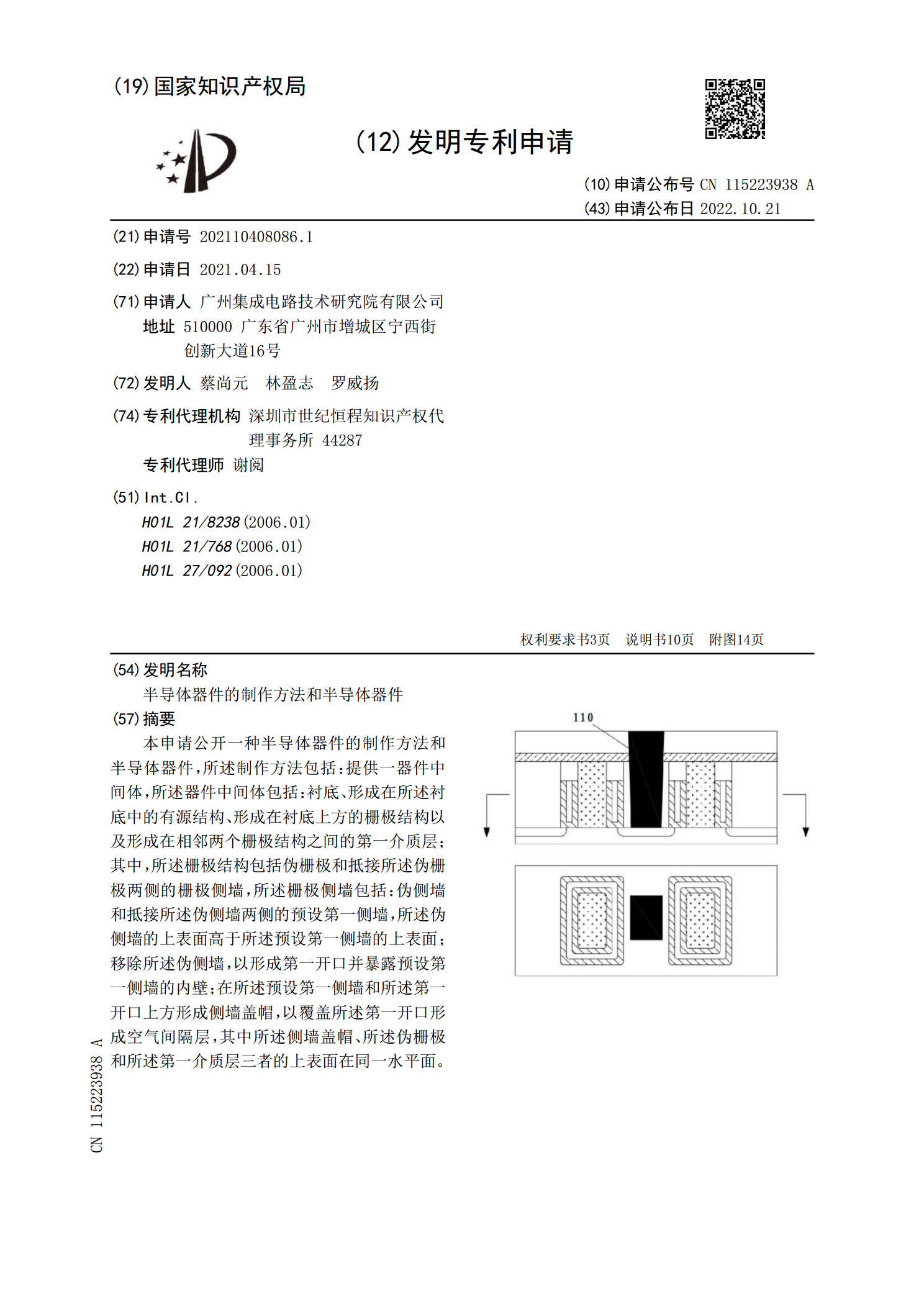

半导体器件的制作方法和半导体器件.pdf

本申请公开一种半导体器件的制作方法和半导体器件,所述制作方法包括:提供一器件中间体,所述器件中间体包括:衬底、形成在所述衬底中的有源结构、形成在衬底上方的栅极结构以及形成在相邻两个栅极结构之间的第一介质层;其中,所述栅极结构包括伪栅极和抵接所述伪栅极两侧的栅极侧墙,所述栅极侧墙包括:伪侧墙和抵接所述伪侧墙两侧的预设第一侧墙,所述伪侧墙的上表面高于所述预设第一侧墙的上表面;移除所述伪侧墙,以形成第一开口并暴露预设第一侧墙的内壁;在所述预设第一侧墙和所述第一开口上方形成侧墙盖帽,以覆盖所述第一开口形成空气间隔

半导体器件的制作方法和半导体器件.pdf

本申请公开一种半导体器件的制作方法和半导体器件,所述制作方法包括:提供一衬底,所述衬底上设置有源结构和栅极结构,所述栅极结构包括用于被移除的牺牲栅极结构和移除后剩余的预留栅极结构;在预定区域处,移除所述牺牲栅极结构以形成对应的栅极开口;在形成所述栅极开口之后,在所述衬底上方以及所述栅极开口内沉积抵接所述预留栅极结构的侧壁的阻挡层和/或层间介质层;以及在形成有所述阻挡层和/或所述层间介质层的栅极开口中形成栅极间隔件。