半导体器件及其制备方法.pdf

是飞****文章

亲,该文档总共14页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体器件及其制备方法.pdf

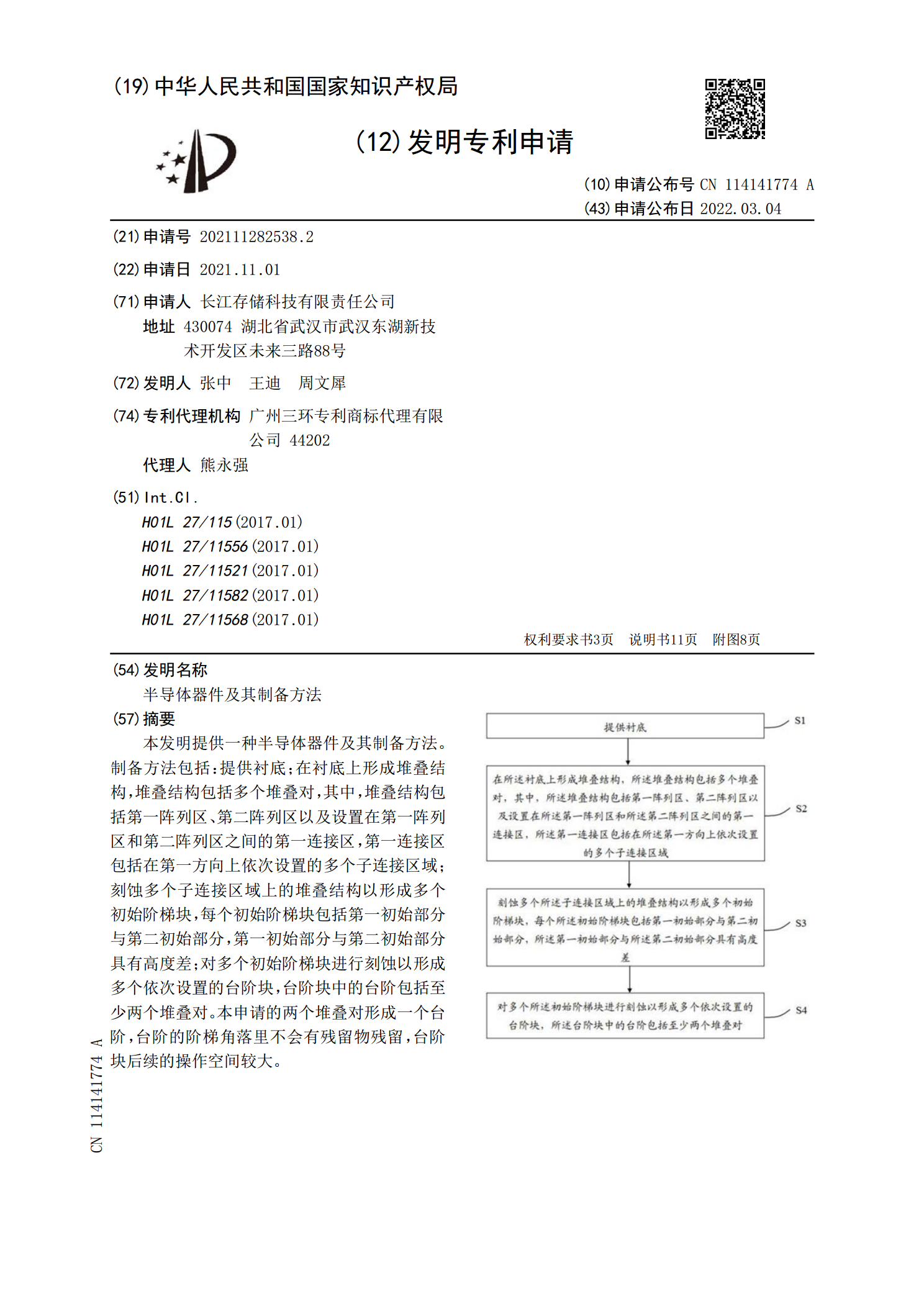

本发明提供一种半导体器件及其制备方法。制备方法包括:提供衬底;在衬底上形成堆叠结构,堆叠结构包括多个堆叠对,其中,堆叠结构包括第一阵列区、第二阵列区以及设置在第一阵列区和第二阵列区之间的第一连接区,第一连接区包括在第一方向上依次设置的多个子连接区域;刻蚀多个子连接区域上的堆叠结构以形成多个初始阶梯块,每个初始阶梯块包括第一初始部分与第二初始部分,第一初始部分与第二初始部分具有高度差;对多个初始阶梯块进行刻蚀以形成多个依次设置的台阶块,台阶块中的台阶包括至少两个堆叠对。本申请的两个堆叠对形成一个台阶,台阶的

半导体器件及其制备方法.pdf

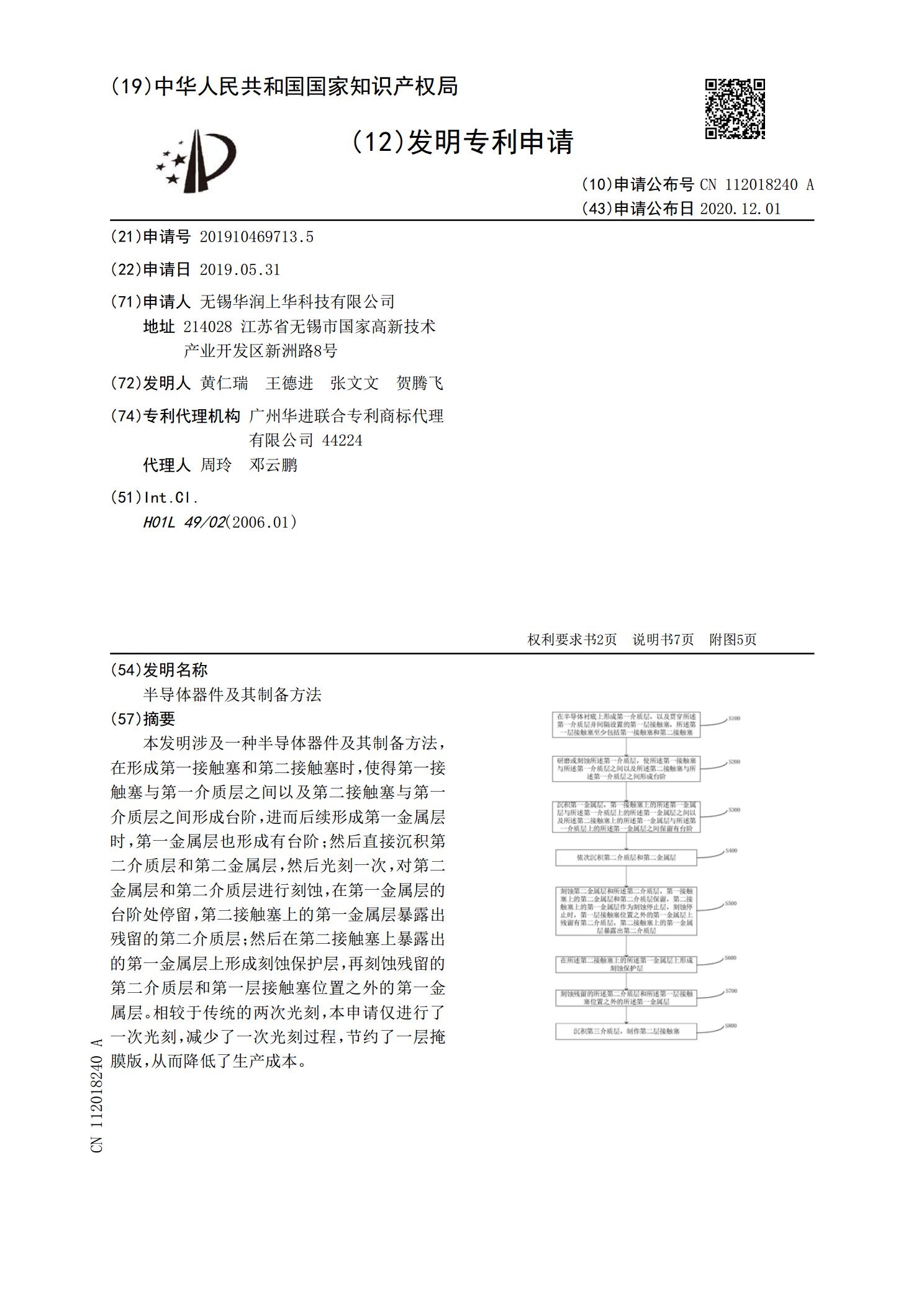

本发明涉及一种半导体器件及其制备方法,在形成第一接触塞和第二接触塞时,使得第一接触塞与第一介质层之间以及第二接触塞与第一介质层之间形成台阶,进而后续形成第一金属层时,第一金属层也形成有台阶;然后直接沉积第二介质层和第二金属层,然后光刻一次,对第二金属层和第二介质层进行刻蚀,在第一金属层的台阶处停留,第二接触塞上的第一金属层暴露出残留的第二介质层;然后在第二接触塞上暴露出的第一金属层上形成刻蚀保护层,再刻蚀残留的第二介质层和第一层接触塞位置之外的第一金属层。相较于传统的两次光刻,本申请仅进行了一次光刻,减少

半导体器件及其制备方法.pdf

本发明揭示了一种半导体器件及其制备方法,包括:提供一衬底,所述衬底具有多个第一区域以及多个第二区域;在所述衬底上形成多个第一图案,所述第一图案位于所述第一区域上,所述第一图案具有一显露所述第二区域的缺口;在所述衬底上形成一第一调整层;在所述第一调整层上形成一第二调整层,所述第二调整层填补所述缺口;去除所述第一图案上方的第二调整层残留的所述第二调整层与所述第二调整层下方的所述第一调整层共同形成为多个第二图案;去除在所述第一图案与所述第二图案之间的所述第一调整层,在所述第一图案和第二图案之间形成间隙,所述间隙

半导体器件及其制备方法.pdf

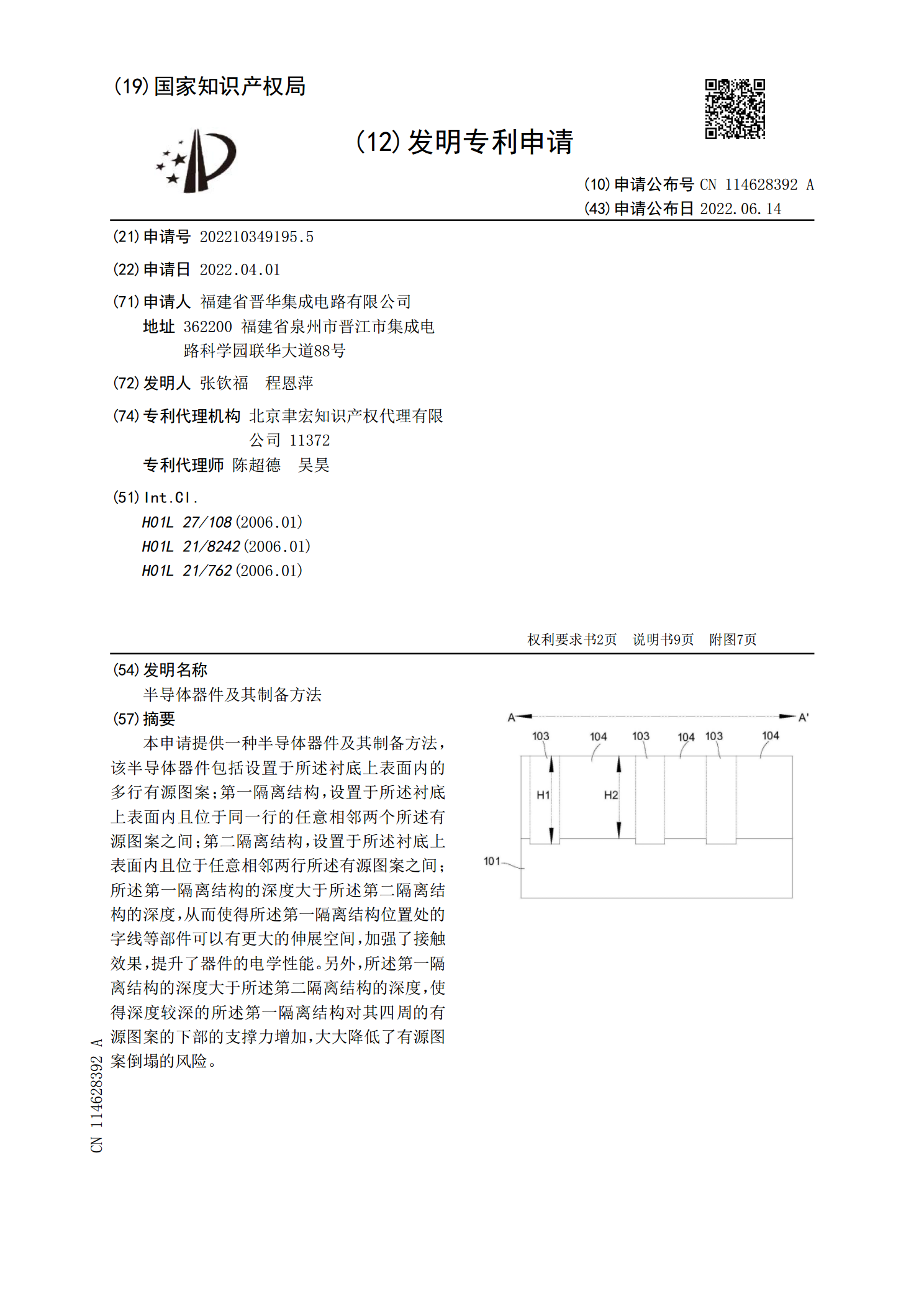

本申请提供一种半导体器件及其制备方法,该半导体器件包括设置于所述衬底上表面内的多行有源图案;第一隔离结构,设置于所述衬底上表面内且位于同一行的任意相邻两个所述有源图案之间;第二隔离结构,设置于所述衬底上表面内且位于任意相邻两行所述有源图案之间;所述第一隔离结构的深度大于所述第二隔离结构的深度,从而使得所述第一隔离结构位置处的字线等部件可以有更大的伸展空间,加强了接触效果,提升了器件的电学性能。另外,所述第一隔离结构的深度大于所述第二隔离结构的深度,使得深度较深的所述第一隔离结构对其四周的有源图案的下部的支

半导体器件及其制备方法.pdf

本发明揭示了一种半导体器件及其制备方法,包括:提供一衬底,所述衬底具有多个第一区域以及多个第二区域;在所述衬底上形成多个第一图案,所述第一图案位于所述第一区域上,所述第一图案具有一显露所述第二区域的缺口;在所述衬底上形成一第一调整层;在所述第一调整层上形成一第二调整层,所述第二调整层填补所述缺口;去除所述第一图案上方的第二调整层残留的所述第二调整层与所述第二调整层下方的所述第一调整层共同形成为多个第二图案;去除在所述第一图案与所述第二图案之间的所述第一调整层,在所述第一图案和第二图案之间形成间隙,所述间隙