MRAM与其制作方法.pdf

是你****芹呀

亲,该文档总共15页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

MRAM与其制作方法.pdf

本申请提供了一种MRAM与其制作方法。该制作方法包括:步骤S1,在基底上设置预存储结构,预存储结构至少包括MTJ单元;步骤S2,在预存储结构的裸露表面上设置保护层材料,或者在预存储结构的裸露表面上以及基底的裸露表面上设置保护层材料;步骤S3,采用各向异性刻蚀法自对准刻蚀去除部分保护层材料,形成位于预存储结构的至少部分侧壁上的保护层。采用自对准刻蚀技术刻蚀保护层,该方法无需设置掩膜层,方法简单,容易控制,且只留下预存储结构侧壁上的保护层材料,避免了MTJ单元两侧的基底表面上或者是部分预存储结构的表面上的保护

包括MRAM底电极制作工艺的制作方法及MRAM器件.pdf

本申请提供了一种包括MRAM底电极制作工艺的制作方法及MRAM器件,该制作方法包括:提供一基底,基底包括依次设置的金属互联层、第一阻挡层以及介电层,在第一阻挡层和介电层中形成底部通孔;在底部通孔和底部通孔两侧的介电层的裸露表面上依次覆盖第二阻挡层和导电金属层,导电金属层填充满底部通孔;采用化学机械抛光法去除第二阻挡层表面的导电金属层,保留第二阻挡层,底部通孔中形成凹陷;沉积底电极金属,填充满凹陷,形成底电极金属预制层;通过化学机械抛光去除部分底电极金属预制层,形成表面平整的底电极金属预制层;对底电极金属预

MRAM芯片结构的制作方法.pdf

本发明提供了一种MRAM芯片结构的制作方法。制作方法包括:提供表面具有阵列区和逻辑区的衬底,阵列区和逻辑区中具有底电极和磁性隧道结;在磁性隧道结上形成层叠设置的顶电极和掩膜层,底电极、磁性隧道结和顶电极构成磁性隧道结单元;在衬底上形成包裹掩膜层和磁性隧道结单元的第一介质层;沿第一介质层的表面进行平坦化处理,以使掩膜层或顶电极具有裸露表面;在磁性隧道结单元远离衬底的一侧形成互连线,使互连线分别与阵列区中的磁性隧道结单元以及逻辑区中的衬底连接。通过使阵列区和逻辑区中的介质层在研磨后厚度具有均一性,再在介质层上

一种SOT-MRAM器件及其制作方法.pdf

本发明提供一种SOT‑MRAM器件及其制作方法,该方法包括以下步骤:形成SOT层于衬底上;自下而上依次MTJ层及顶电极层于SOT层上;刻蚀MTJ层及顶电极层的预设区域,以分割得到多个分立设置的MTJ结构;形成第一电介质层以被覆MTJ结构的暴露表面及SOT层未被MTJ结构遮盖的表面;形成第二电介质层于第一电介质层上;形成贯穿第一、第二电介质层及SOT层的分隔槽以得到多个分立设置的位单元,每一位单元包括一MTJ结构。本发明在SOT层沉积和CMP工艺完成后直接沉积MTJ层和顶电极层,在完成MTJ结构的刻蚀和覆盖

封装基板与其制作方法.pdf

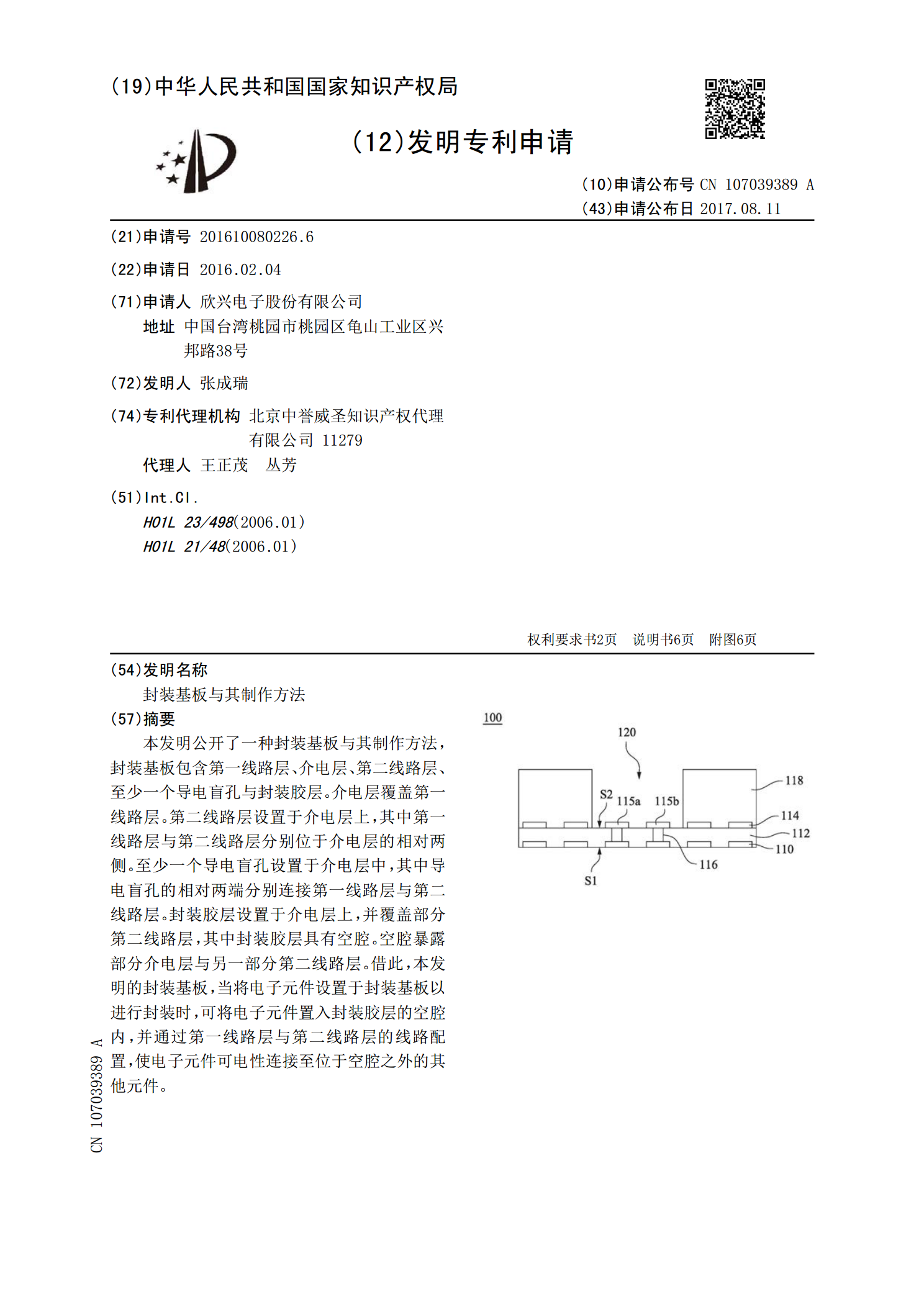

本发明公开了一种封装基板与其制作方法,封装基板包含第一线路层、介电层、第二线路层、至少一个导电盲孔与封装胶层。介电层覆盖第一线路层。第二线路层设置于介电层上,其中第一线路层与第二线路层分别位于介电层的相对两侧。至少一个导电盲孔设置于介电层中,其中导电盲孔的相对两端分别连接第一线路层与第二线路层。封装胶层设置于介电层上,并覆盖部分第二线路层,其中封装胶层具有空腔。空腔暴露部分介电层与另一部分第二线路层。借此,本发明的封装基板,当将电子元件设置于封装基板以进行封装时,可将电子元件置入封装胶层的空腔内,并通过第