一种SOT-MRAM器件及其制作方法.pdf

波峻****99

亲,该文档总共19页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种CMOS器件及其制作方法.pdf

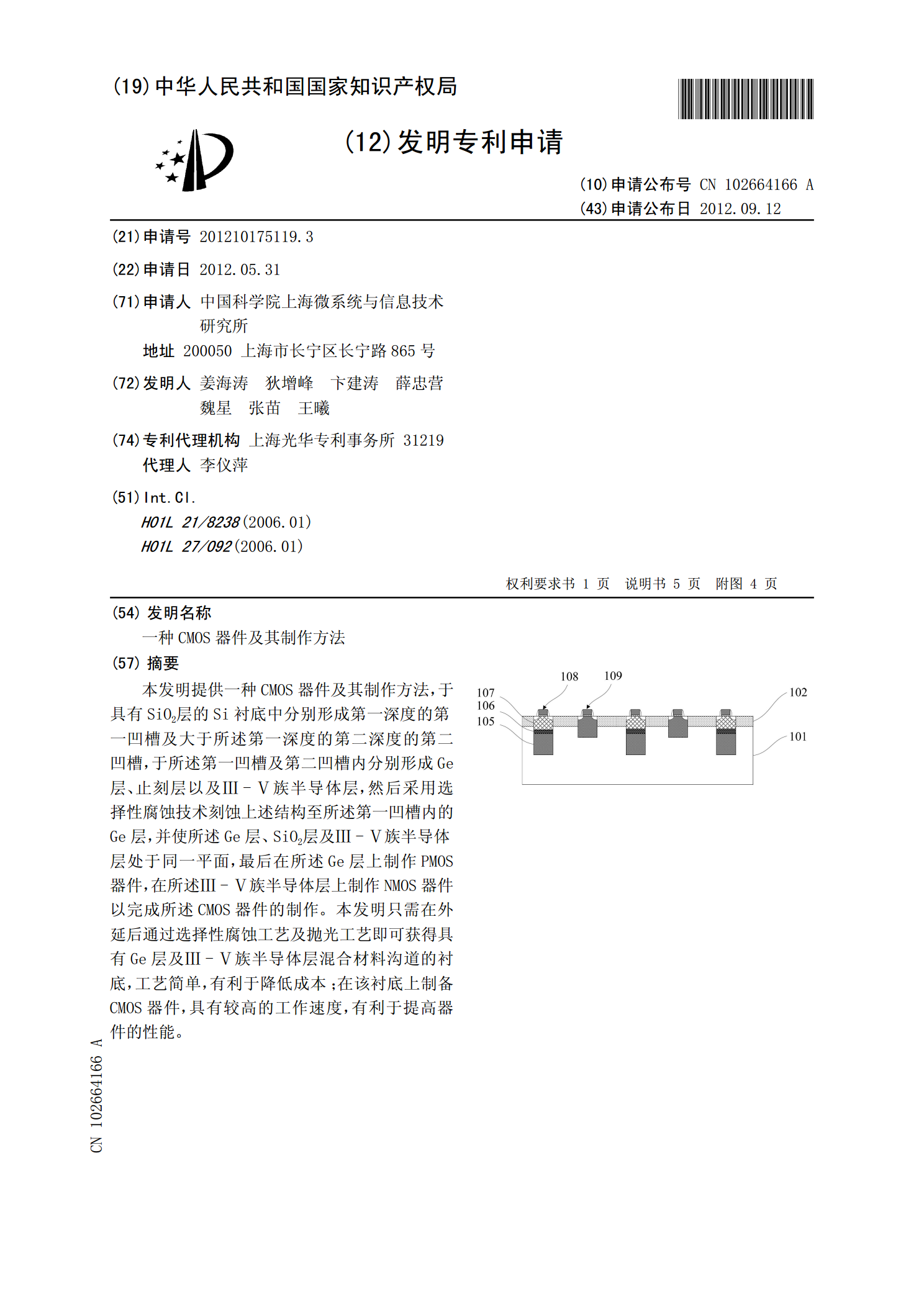

本发明提供一种CMOS器件及其制作方法,于具有SiO2层的Si衬底中分别形成第一深度的第一凹槽及大于所述第一深度的第二深度的第二凹槽,于所述第一凹槽及第二凹槽内分别形成Ge层、止刻层以及Ⅲ-Ⅴ族半导体层,然后采用选择性腐蚀技术刻蚀上述结构至所述第一凹槽内的Ge层,并使所述Ge层、SiO2层及Ⅲ-Ⅴ族半导体层处于同一平面,最后在所述Ge层上制作PMOS器件,在所述Ⅲ-Ⅴ族半导体层上制作NMOS器件以完成所述CMOS器件的制作。本发明只需在外延后通过选择性腐蚀工艺及抛光工艺即可获得具有Ge层及Ⅲ-Ⅴ族半导体层

一种半导体器件及其制作方法.pdf

本发明提供一种半导体器件及其制作方法,所述制作方法包括:提供晶圆,所述晶圆包括若干芯片以及设置在相邻芯片之间的切割道,其中所述切割道包括自下而上的蜂窝状结构,所述蜂窝状结构由多层绝缘层和形成于所述绝缘层内的具有填充空洞的若干通孔结构组成;沿所述切割道对所述晶圆进行切割。根据本发明的制作方法,由于本发明的切割道包括蜂窝状结构,在切割过程中降低了机械应力,防止了芯片边缘由于机械应力而导致的裂缝问题的产生,保护了芯片的内部结构不受到裂缝的影响,进而提高了器件的良率和可靠性。

一种半导体器件及其制作方法.pdf

本公开提供了一种半导体器件及其制作方法。所述半导体器件制作方法包括:在半导体衬底(101)上形成的沟槽(112)的底部和壁形成第一隔离层(116);在隔离层(116)上沉积半导体材料,形成屏蔽栅(SG),通过光刻掩模保留半导体材料形成屏蔽栅(SG)的引出栅(DG);在屏蔽栅(SG)之上形成第二隔离层(145);在第二隔离层(145)上顺序形成控制栅(CG)和源极(S);在形成高频半导体器件的情况下和形成可靠型半导体器件的情况下,分别将将引出栅(DG)与源极(S)接合、和与控制栅(CG)接合。本公开通过采用

一种半导体器件及其制作方法.pdf

本发明提供一种半导体器件及其制作方法,提供晶圆,在晶圆上形成阻挡层;在阻挡层上形成图案化的光刻胶层;以光刻胶层为掩膜,刻蚀去除部分厚度的阻挡层,剩余阻挡层作为保护层;利用光刻胶剥离工艺去除光刻胶层;在阻挡层上形成聚酰亚胺层;刻蚀去除保护层以露出晶圆表面的焊盘;对聚酰亚胺层执行固化处理。本发明通过在对阻挡层进行图案化处理时,对阻挡层不进行全部刻蚀,保留部分厚度的阻挡层作为保护层,在后续形成聚酰亚胺层显影时,避免了金属与显影液直接接触,完全避免了显影液对金属腐蚀发黑现象的产生,尤其对于再工事批次,大大提升了外

一种倒装MOSFET器件及其制作方法.pdf

本发明公开了一种倒装MOSFET器件及其制作方法,其中,倒装MOSFET器件包括从上至下依次层设的氧化镓衬底、n型掺杂氧化镓层、n型重掺杂氧化镓层、二氧化硅钝化层、氧化铝介质层、键合层和氮化铝导热层;所述n型重掺杂氧化镓层和所述二氧化硅钝化层之间设有源电极和漏电极,所述氧化铝介质层上设有栅电极;所述氧化镓衬底的自由端面上刻蚀有由微纳结构阵列形成的散热结构,所述微纳结构的横截面尺寸为微米级或纳米级。本发明在氧化镓衬底的表面上刻蚀有微纳结构阵列,提高了散热效率。相比于电子器件散热器,本发明在器件的设计阶段预留