一种在印制电路板平面集成薄膜磁芯电感的方法及相关薄膜磁芯电感.pdf

光誉****君哥

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种在印制电路板平面集成薄膜磁芯电感的方法及相关薄膜磁芯电感.pdf

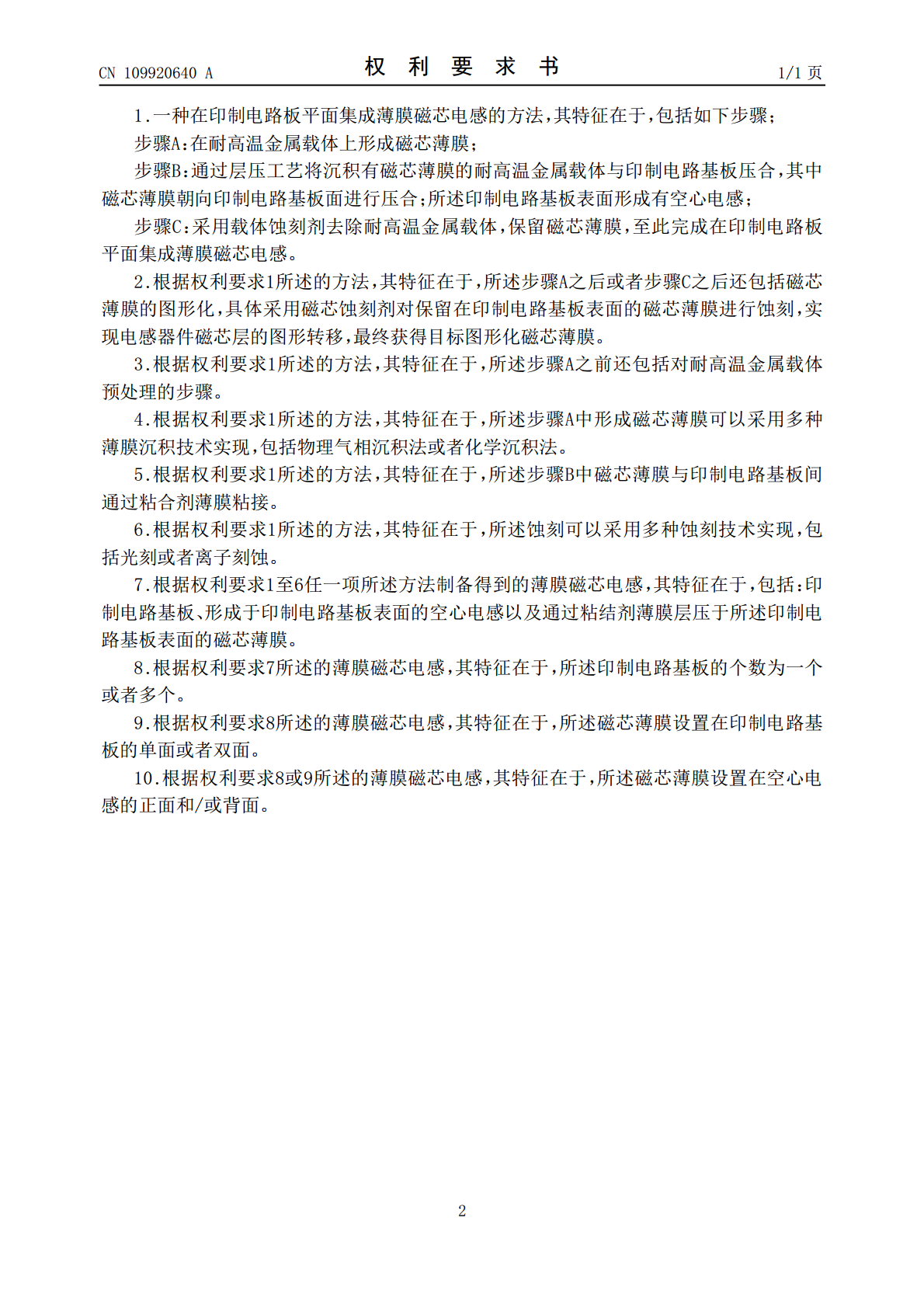

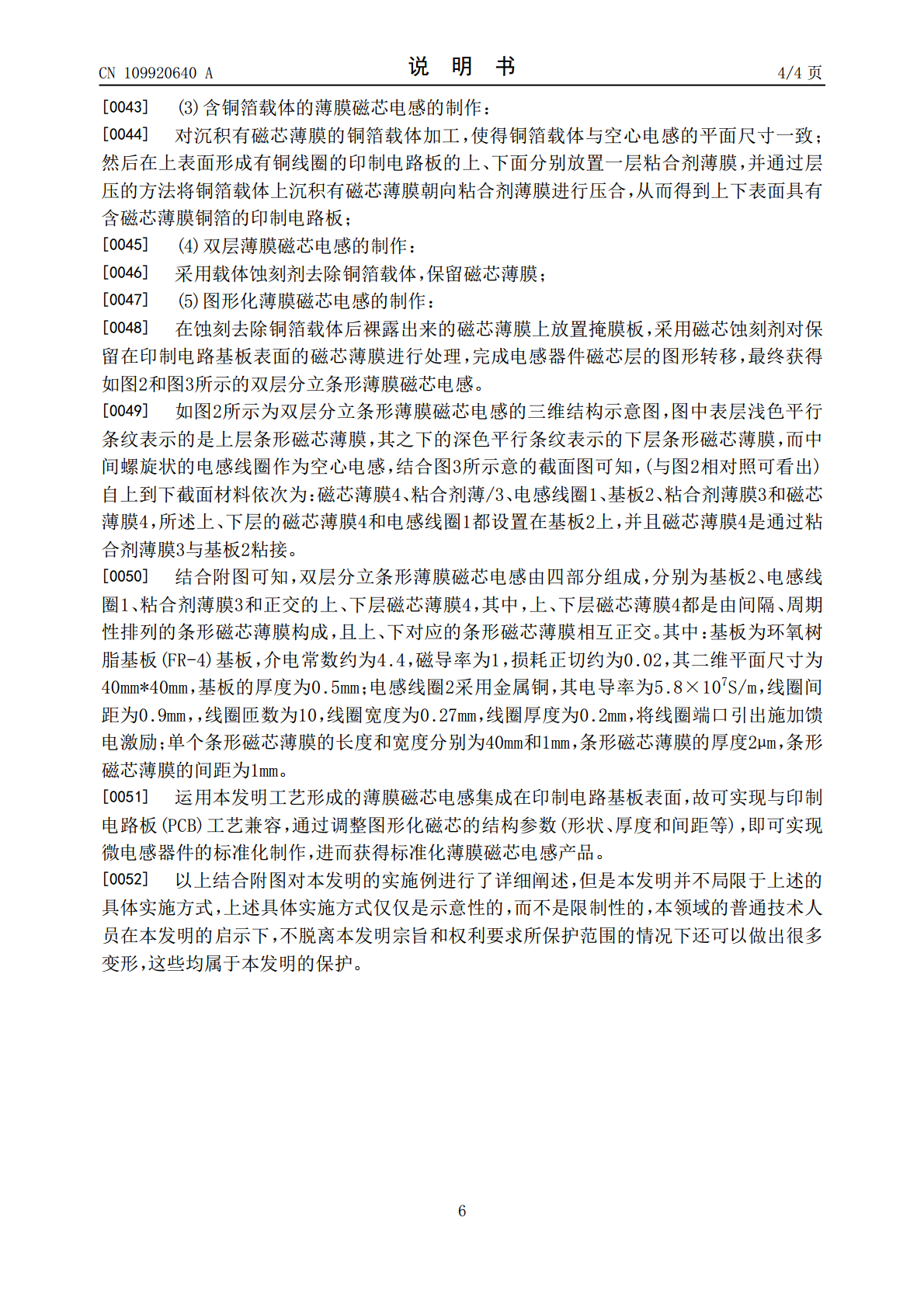

一种在印制电路板平面集成薄膜磁芯电感的方法及相关薄膜磁芯电感,属于印制电路技术领域。本发明利用耐高温金属作为磁芯薄膜的载体和电感结构的牺牲层,然后基于层压技术将沉积有磁芯薄膜的耐高温金属载体与形成有空心电感的印制电路板压合,再蚀刻去除耐高温金属而保留磁芯薄膜,并根据需要实现磁芯薄膜的图形化,从而实现了标准化薄膜磁芯电感产品的制作。运用本方法得到的磁芯薄膜粘接在形成有空心电感的印制电路板表面,实现了微电感器件在印制电路板上的平面集成。本发明提供的工艺能够与PCB工艺相兼容,易于实现产业化生产,非常有利于微电

磁芯、电感器和制造磁芯的方法.pdf

磁芯包括具有基本均匀厚度的中心部分和连接至中心部分并且围绕中心部分的边缘部分。边缘部分包括底部和设置在底部上的顶部,其中,底部具有平缓的侧表面,而顶部具有陡的侧表面。磁芯的轮廓可以更像矩形,从而提供更好的电感器性能。本发明的实施例还涉及磁芯、电感器和制造磁芯的方法。

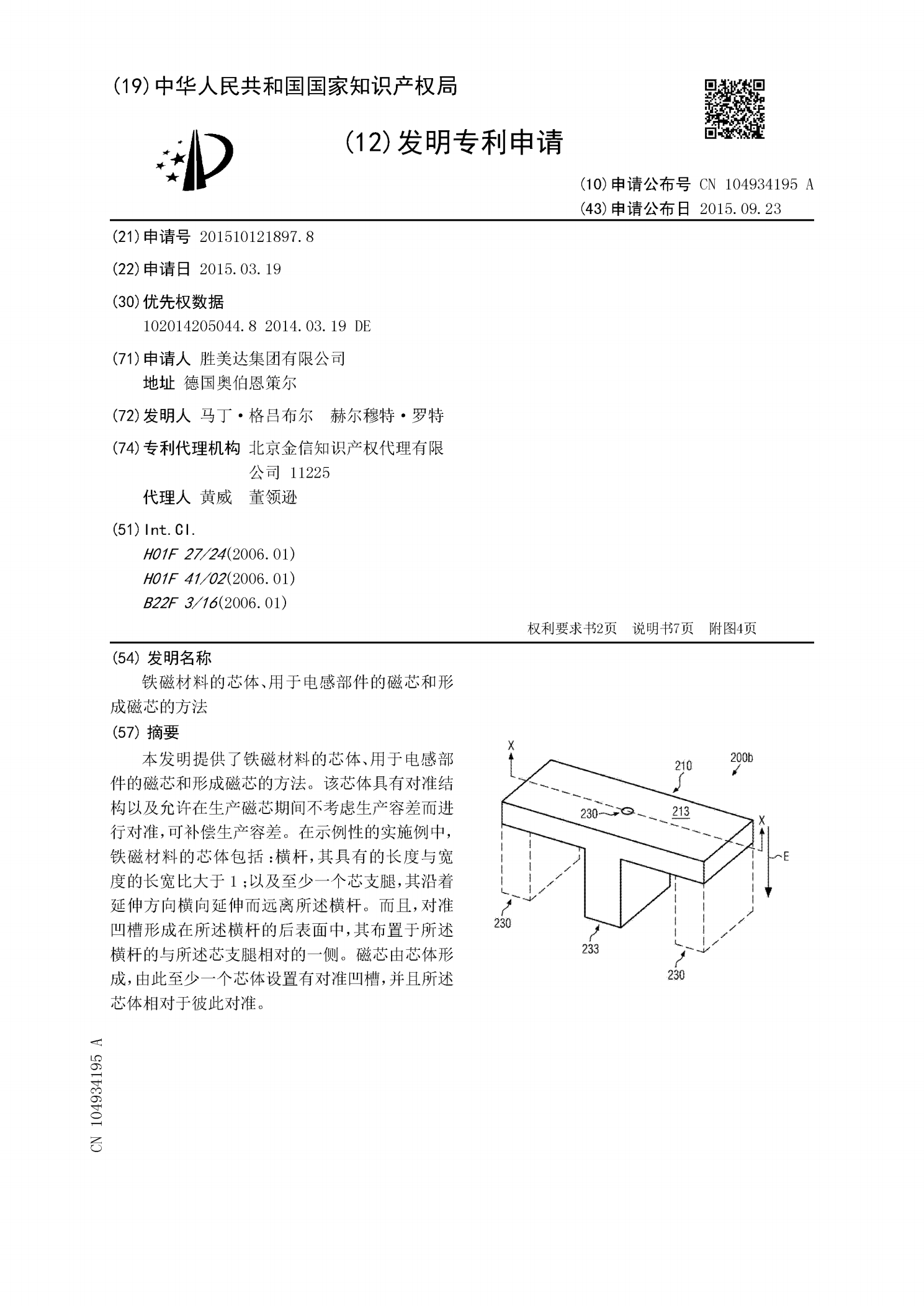

铁磁材料的芯体、用于电感部件的磁芯和形成磁芯的方法.pdf

本发明提供了铁磁材料的芯体、用于电感部件的磁芯和形成磁芯的方法。该芯体具有对准结构以及允许在生产磁芯期间不考虑生产容差而进行对准,可补偿生产容差。在示例性的实施例中,铁磁材料的芯体包括:横杆,其具有的长度与宽度的长宽比大于1;以及至少一个芯支腿,其沿着延伸方向横向延伸而远离所述横杆。而且,对准凹槽形成在所述横杆的后表面中,其布置于所述横杆的与所述芯支腿相对的一侧。磁芯由芯体形成,由此至少一个芯体设置有对准凹槽,并且所述芯体相对于彼此对准。

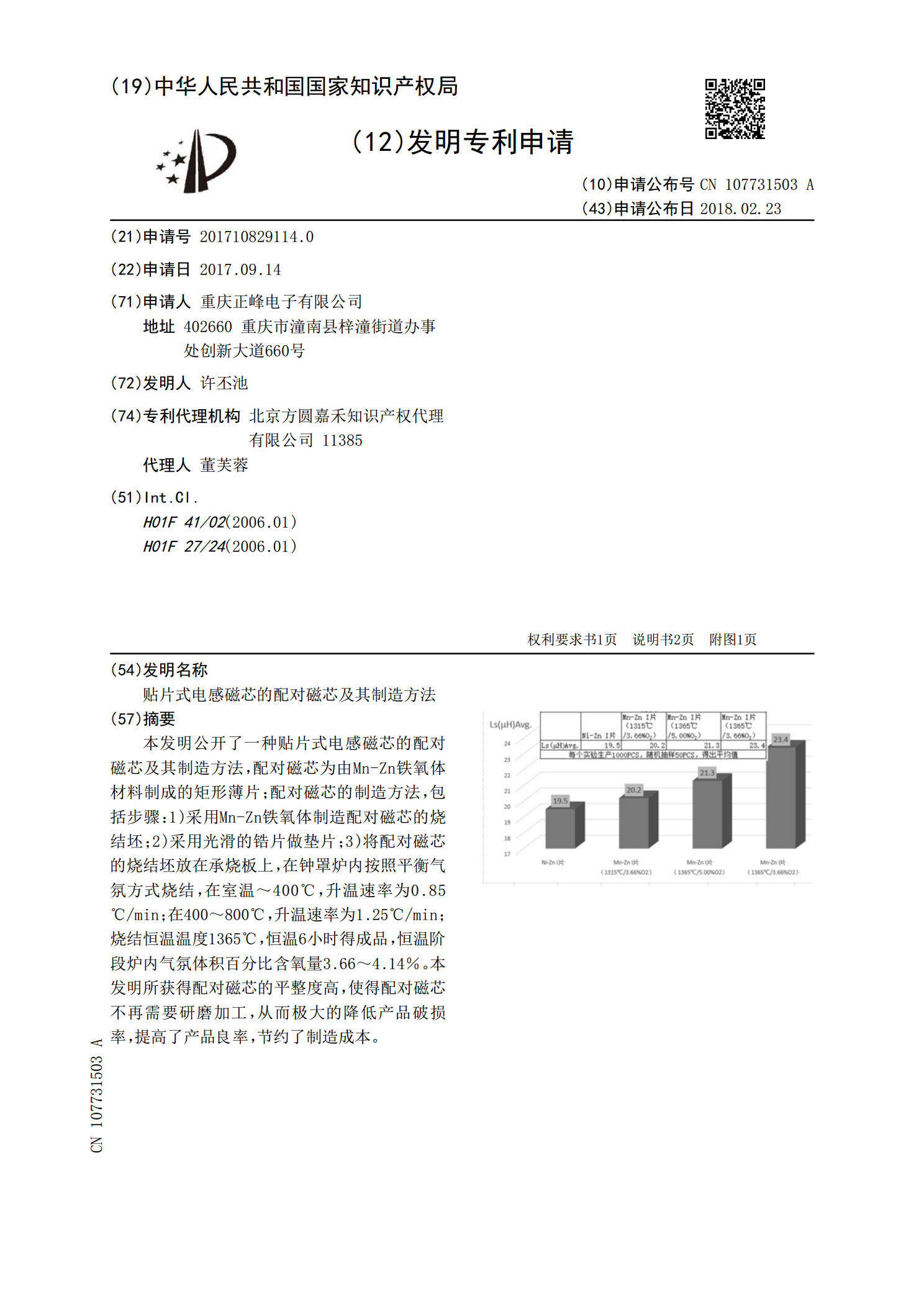

贴片式电感磁芯的配对磁芯及其制造方法.pdf

本发明公开了一种贴片式电感磁芯的配对磁芯及其制造方法,配对磁芯为由Mn‑Zn铁氧体材料制成的矩形薄片;配对磁芯的制造方法,包括步骤:1)采用Mn‑Zn铁氧体制造配对磁芯的烧结坯;2)采用光滑的锆片做垫片;3)将配对磁芯的烧结坯放在承烧板上,在钟罩炉内按照平衡气氛方式烧结,在室温~400℃,升温速率为0.85℃/min;在400~800℃,升温速率为1.25℃/min;烧结恒温温度1365℃,恒温6小时得成品,恒温阶段炉内气氛体积百分比含氧量3.66~4.14%。本发明所获得配对磁芯的平整度高,使得配对磁芯

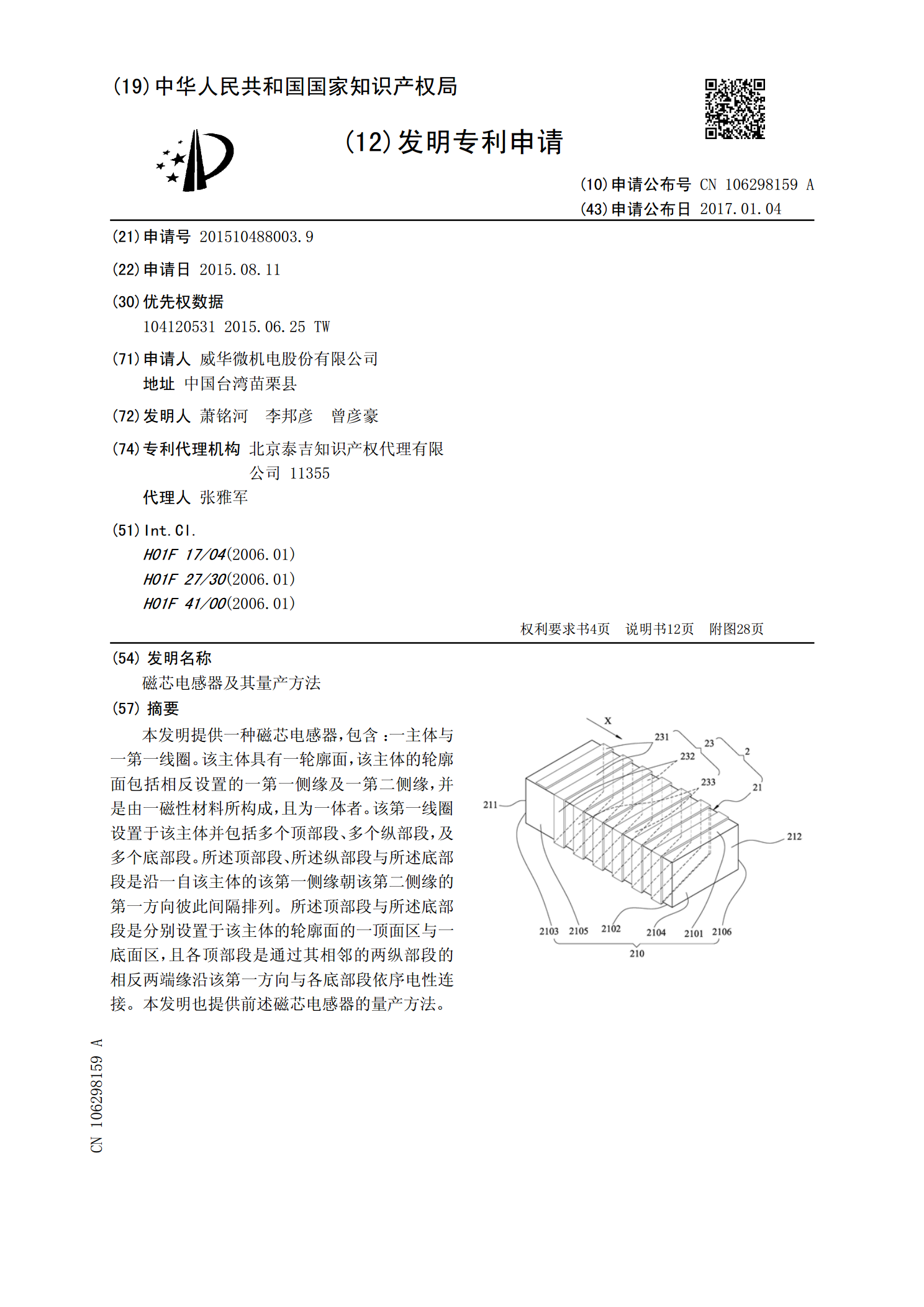

磁芯电感器及其量产方法.pdf

本发明提供一种磁芯电感器,包含:一主体与一第一线圈。该主体具有一轮廓面,该主体的轮廓面包括相反设置的一第一侧缘及一第二侧缘,并是由一磁性材料所构成,且为一体者。该第一线圈设置于该主体并包括多个顶部段、多个纵部段,及多个底部段。所述顶部段、所述纵部段与所述底部段是沿一自该主体的该第一侧缘朝该第二侧缘的第一方向彼此间隔排列。所述顶部段与所述底部段是分别设置于该主体的轮廓面的一顶面区与一底面区,且各顶部段是通过其相邻的两纵部段的相反两端缘沿该第一方向与各底部段依序电性连接。本发明也提供前述磁芯电感器的量产方法。