半导体存储单元的制造方法及半导体存储单元.pdf

Jo****34

亲,该文档总共17页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体存储单元的制造方法及半导体存储单元.pdf

本发明实施例公开了一种半导体存储单元的制造方法及半导体存储单元。制造方法包括:提供基板,基板包括位线和位线隔离结构,位线隔离结构之间形成电容接触槽,电容接触槽下方的基板中包括浅沟道隔离结构和分别设置在其两侧的漏极,漏极的上表面形成漏极的第一基准面;在基板一侧表面上形成第一隔离牺牲层,第一隔离牺牲层在位线隔离结构的侧面处的厚度小于漏极的第一基准面的宽度;自第一隔离牺牲层的上表面向下刻蚀,以去除在位线隔离结构的上表面、浅沟道隔离结构的上表面和在部分第一基准面上的第一隔离牺牲层,藉以保留在位线隔离结构的侧面处的

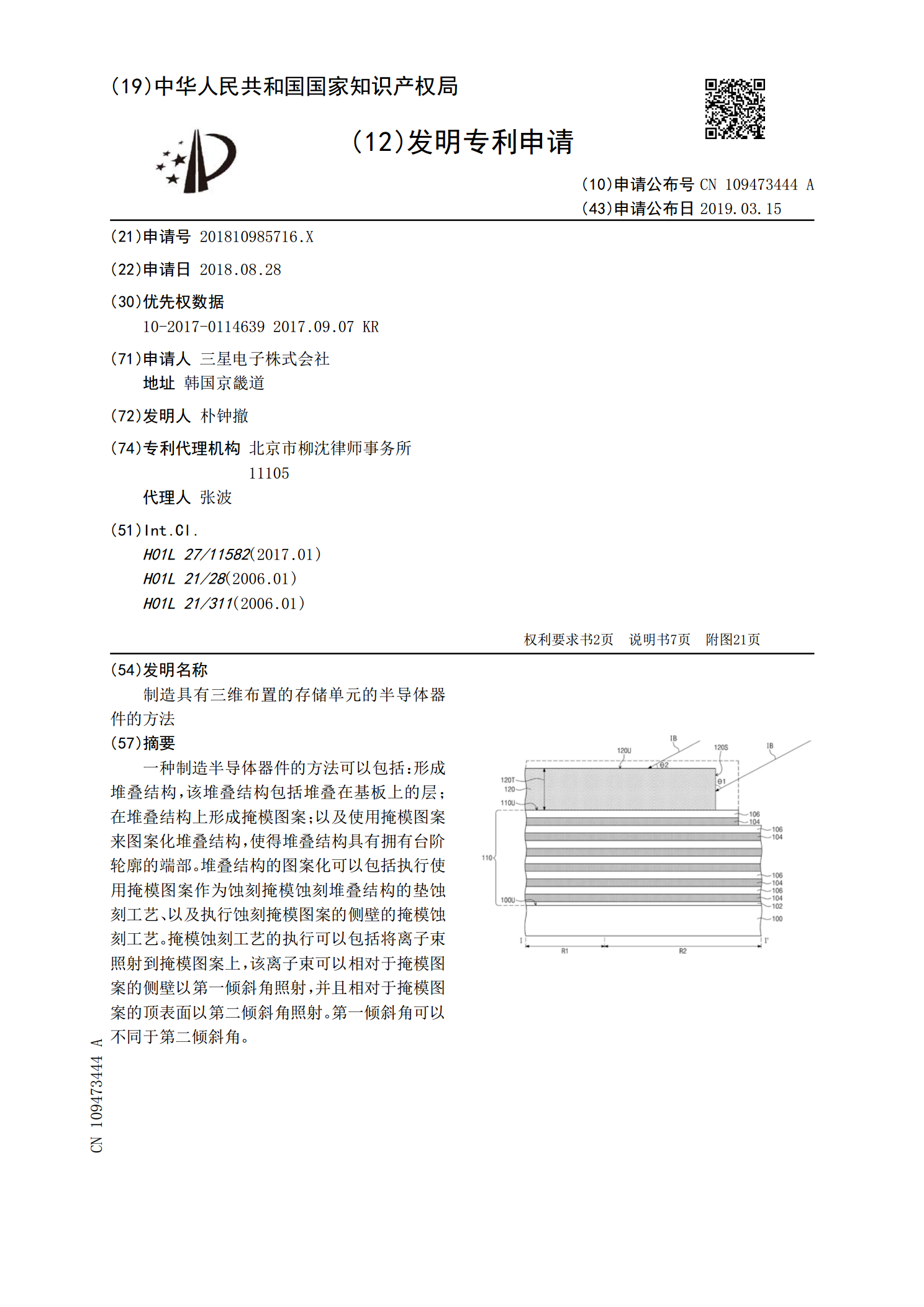

制造具有三维布置的存储单元的半导体器件的方法.pdf

一种制造半导体器件的方法可以包括:形成堆叠结构,该堆叠结构包括堆叠在基板上的层;在堆叠结构上形成掩模图案;以及使用掩模图案来图案化堆叠结构,使得堆叠结构具有拥有台阶轮廓的端部。堆叠结构的图案化可以包括执行使用掩模图案作为蚀刻掩模蚀刻堆叠结构的垫蚀刻工艺、以及执行蚀刻掩模图案的侧壁的掩模蚀刻工艺。掩模蚀刻工艺的执行可以包括将离子束照射到掩模图案上,该离子束可以相对于掩模图案的侧壁以第一倾斜角照射,并且相对于掩模图案的顶表面以第二倾斜角照射。第一倾斜角可以不同于第二倾斜角。

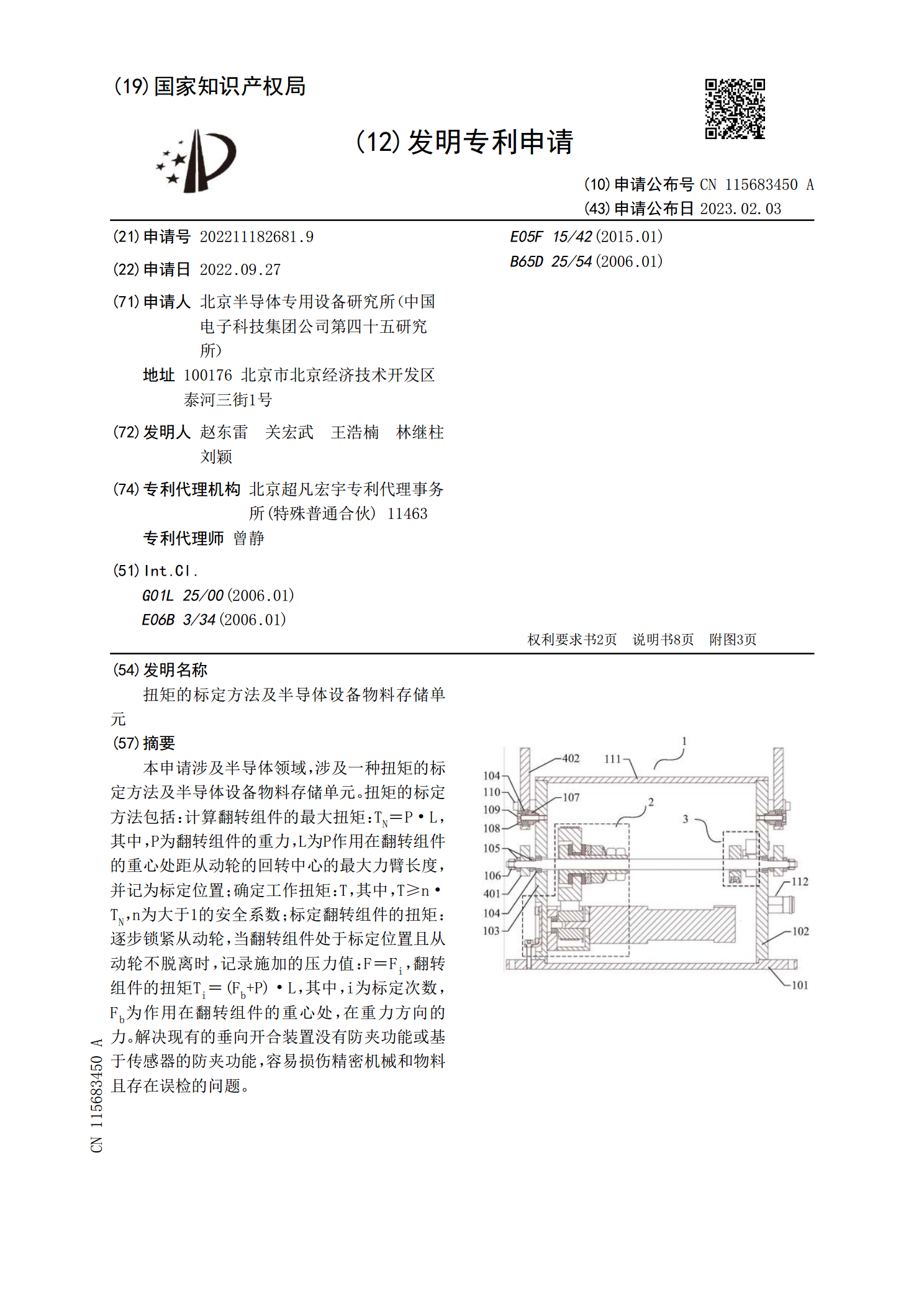

扭矩的标定方法及半导体设备物料存储单元.pdf

本申请涉及半导体领域,涉及一种扭矩的标定方法及半导体设备物料存储单元。扭矩的标定方法包括:计算翻转组件的最大扭矩:T<base:Sub>N</base:Sub>=P·L,其中,P为翻转组件的重力,L为P作用在翻转组件的重心处距从动轮的回转中心的最大力臂长度,并记为标定位置;确定工作扭矩:T,其中,T≥n·T<base:Sub>N</base:Sub>,n为大于1的安全系数;标定翻转组件的扭矩:逐步锁紧从动轮,当翻转组件处于标定位置且从动轮不脱离时,记录施加的压力值:F=F<base:Sub>i</base

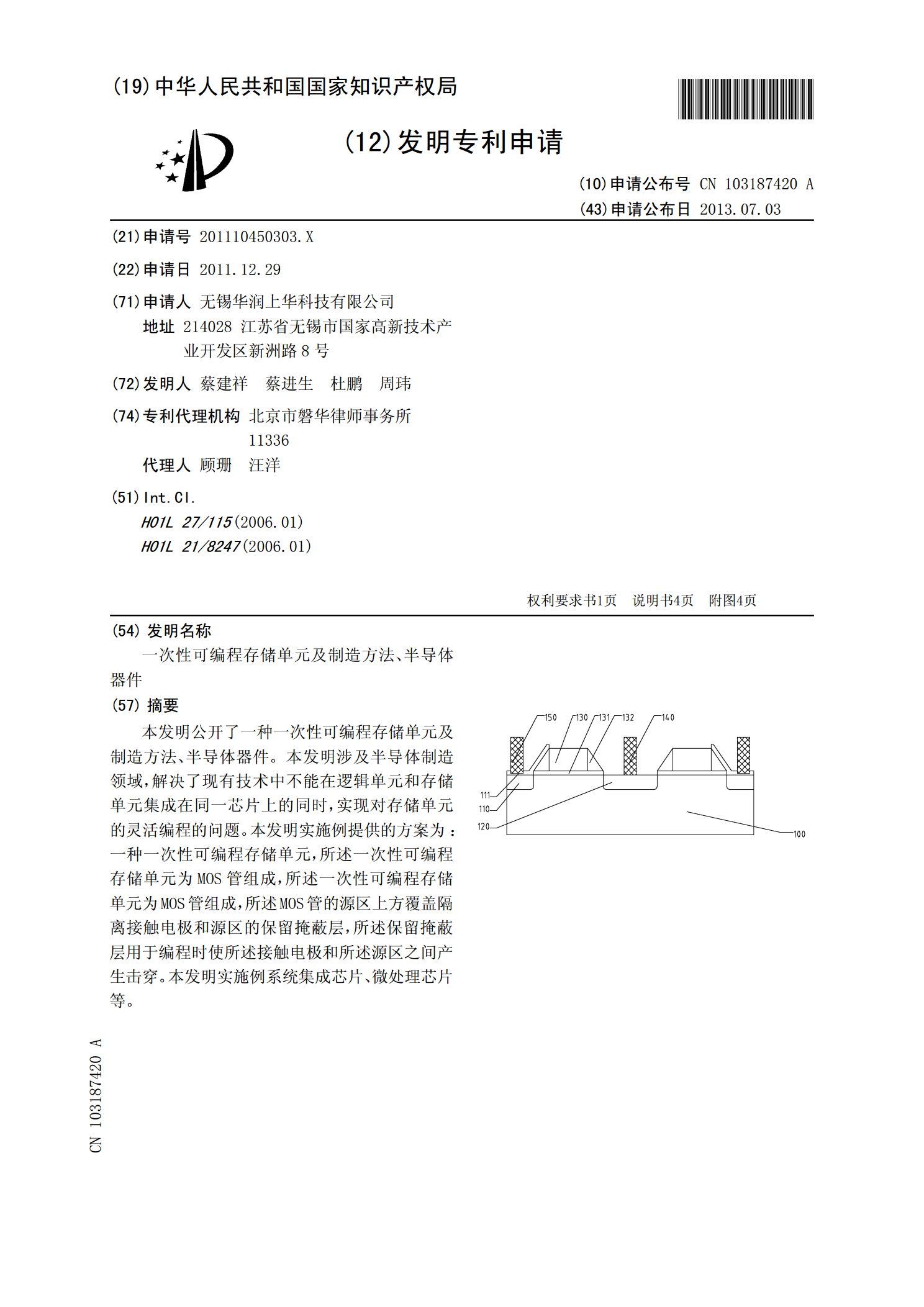

一次性可编程存储单元及制造方法、半导体器件.pdf

本发明公开了一种一次性可编程存储单元及制造方法、半导体器件。本发明涉及半导体制造领域,解决了现有技术中不能在逻辑单元和存储单元集成在同一芯片上的同时,实现对存储单元的灵活编程的问题。本发明实施例提供的方案为:一种一次性可编程存储单元,所述一次性可编程存储单元为MOS管组成,所述一次性可编程存储单元为MOS管组成,所述MOS管的源区上方覆盖隔离接触电极和源区的保留掩蔽层,所述保留掩蔽层用于编程时使所述接触电极和所述源区之间产生击穿。本发明实施例系统集成芯片、微处理芯片等。

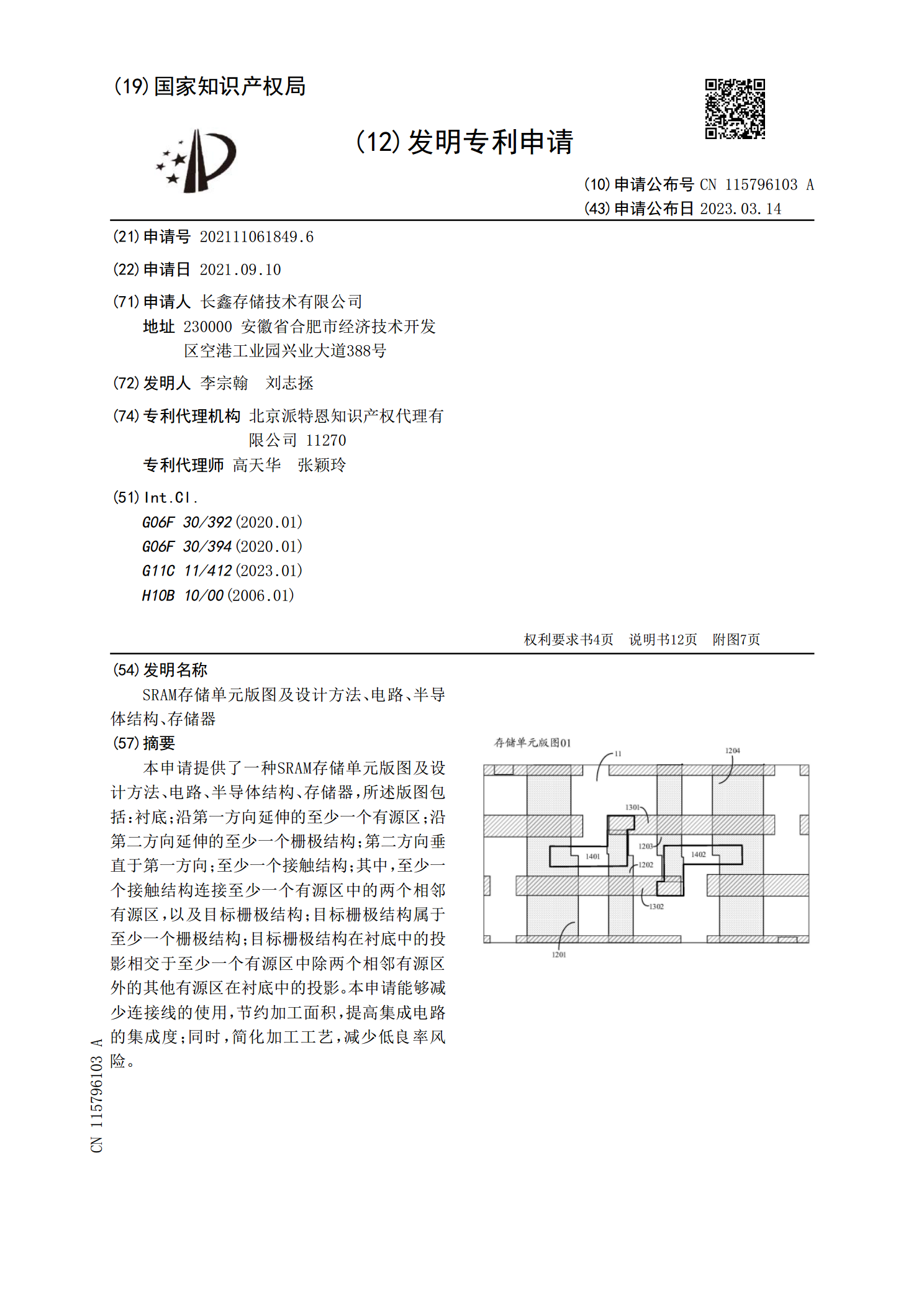

SRAM存储单元版图及设计方法、电路、半导体结构、存储器.pdf

本申请提供了一种SRAM存储单元版图及设计方法、电路、半导体结构、存储器,所述版图包括:衬底;沿第一方向延伸的至少一个有源区;沿第二方向延伸的至少一个栅极结构;第二方向垂直于第一方向;至少一个接触结构;其中,至少一个接触结构连接至少一个有源区中的两个相邻有源区,以及目标栅极结构;目标栅极结构属于至少一个栅极结构;目标栅极结构在衬底中的投影相交于至少一个有源区中除两个相邻有源区外的其他有源区在衬底中的投影。本申请能够减少连接线的使用,节约加工面积,提高集成电路的集成度;同时,简化加工工艺,减少低良率风险。