半导体装置制造方法和半导体装置.pdf

猫巷****觅蓉

亲,该文档总共30页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体装置制造方法和半导体装置.pdf

一种半导体装置制造方法,包括蚀刻通孔通过介电层和蚀刻停止层(ESL)到源极/漏极接点、在源极/漏极接点的顶表面中形成凹陷,使得源极/漏极接点的顶表面是凹的、以及在通孔的侧壁上形成氧化物衬垫。氧化物衬垫捕捉藉由蚀刻通过介电层和蚀刻停止层的通孔所留下的杂质,其中蚀刻步骤、形成凹陷的步骤以及形成氧化物衬垫的步骤在第一腔室中执行。半导体装置制造方法更包括执行移除氧化物衬垫的预清洗和在通孔中沉积金属。

半导体装置的制造方法和半导体装置的制造装置.pdf

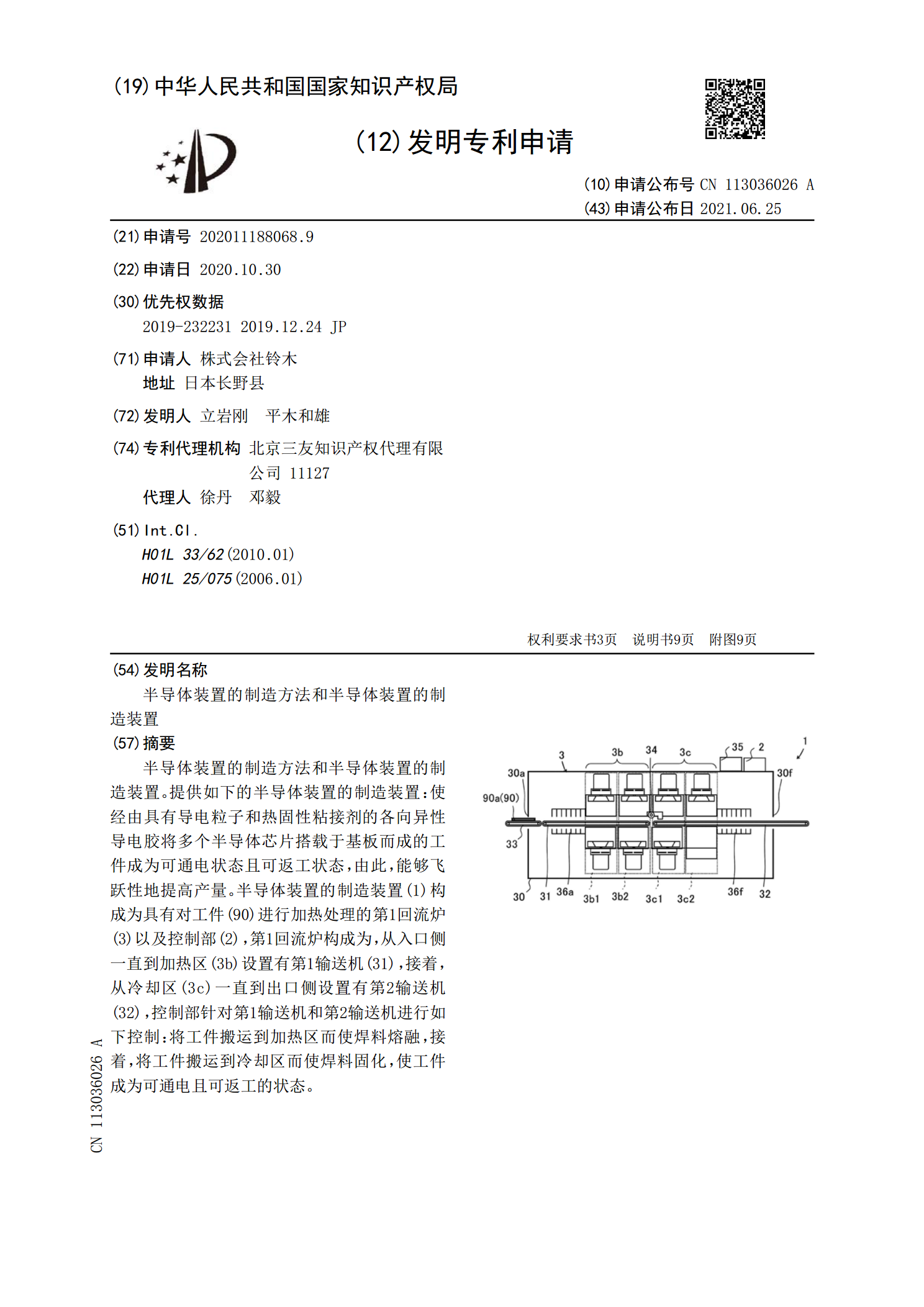

半导体装置的制造方法和半导体装置的制造装置。提供如下的半导体装置的制造装置:使经由具有导电粒子和热固性粘接剂的各向异性导电胶将多个半导体芯片搭载于基板而成的工件成为可通电状态且可返工状态,由此,能够飞跃性地提高产量。半导体装置的制造装置(1)构成为具有对工件(90)进行加热处理的第1回流炉(3)以及控制部(2),第1回流炉构成为,从入口侧一直到加热区(3b)设置有第1输送机(31),接着,从冷却区(3c)一直到出口侧设置有第2输送机(32),控制部针对第1输送机和第2输送机进行如下控制:将工件搬运到加热区

半导体装置和半导体装置的制造方法.pdf

即使当焊盘小型化时,本发明也能提高焊接强度。该半导体装置设置有焊盘、扩散层和熔融层。设置在所述半导体装置中的所述焊盘在其所述表面中包括凹部,并经过焊接。设置在所述半导体装置中的所述扩散层由布置在所述凹部中并当进行焊接时扩散到所述焊料中并保留在所述焊盘的表面上的金属制成。设置在所述半导体装置中的所述熔融层由与所述扩散层相邻布置并当进行焊接时扩散到所述焊料中并熔融的金属制成。

半导体装置和制造半导体装置的方法.pdf

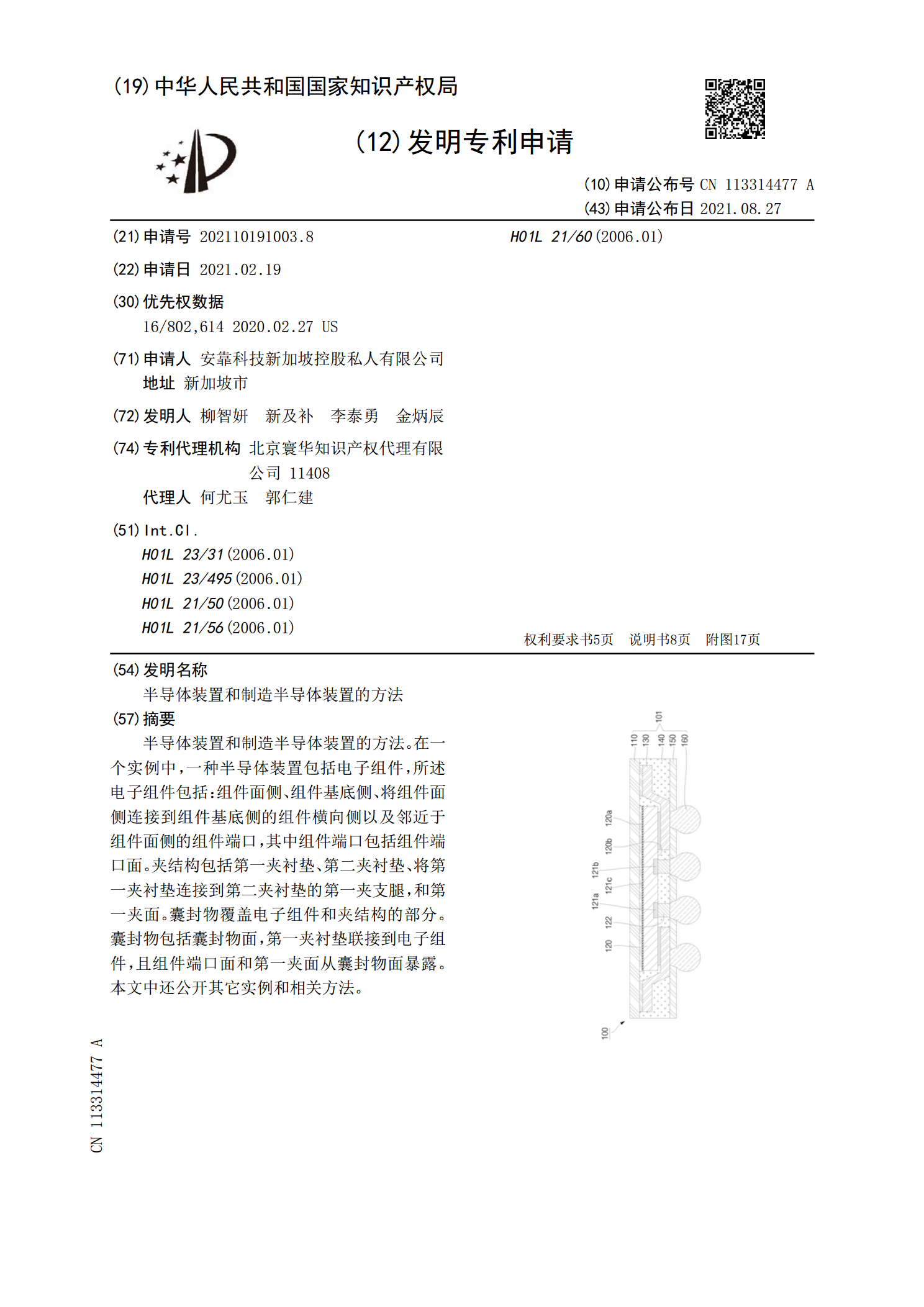

半导体装置和制造半导体装置的方法。在一个实例中,一种半导体装置包括电子组件,所述电子组件包括:组件面侧、组件基底侧、将组件面侧连接到组件基底侧的组件横向侧以及邻近于组件面侧的组件端口,其中组件端口包括组件端口面。夹结构包括第一夹衬垫、第二夹衬垫、将第一夹衬垫连接到第二夹衬垫的第一夹支腿,和第一夹面。囊封物覆盖电子组件和夹结构的部分。囊封物包括囊封物面,第一夹衬垫联接到电子组件,且组件端口面和第一夹面从囊封物面暴露。本文中还公开其它实例和相关方法。

半导体装置和半导体装置的制造方法.pdf

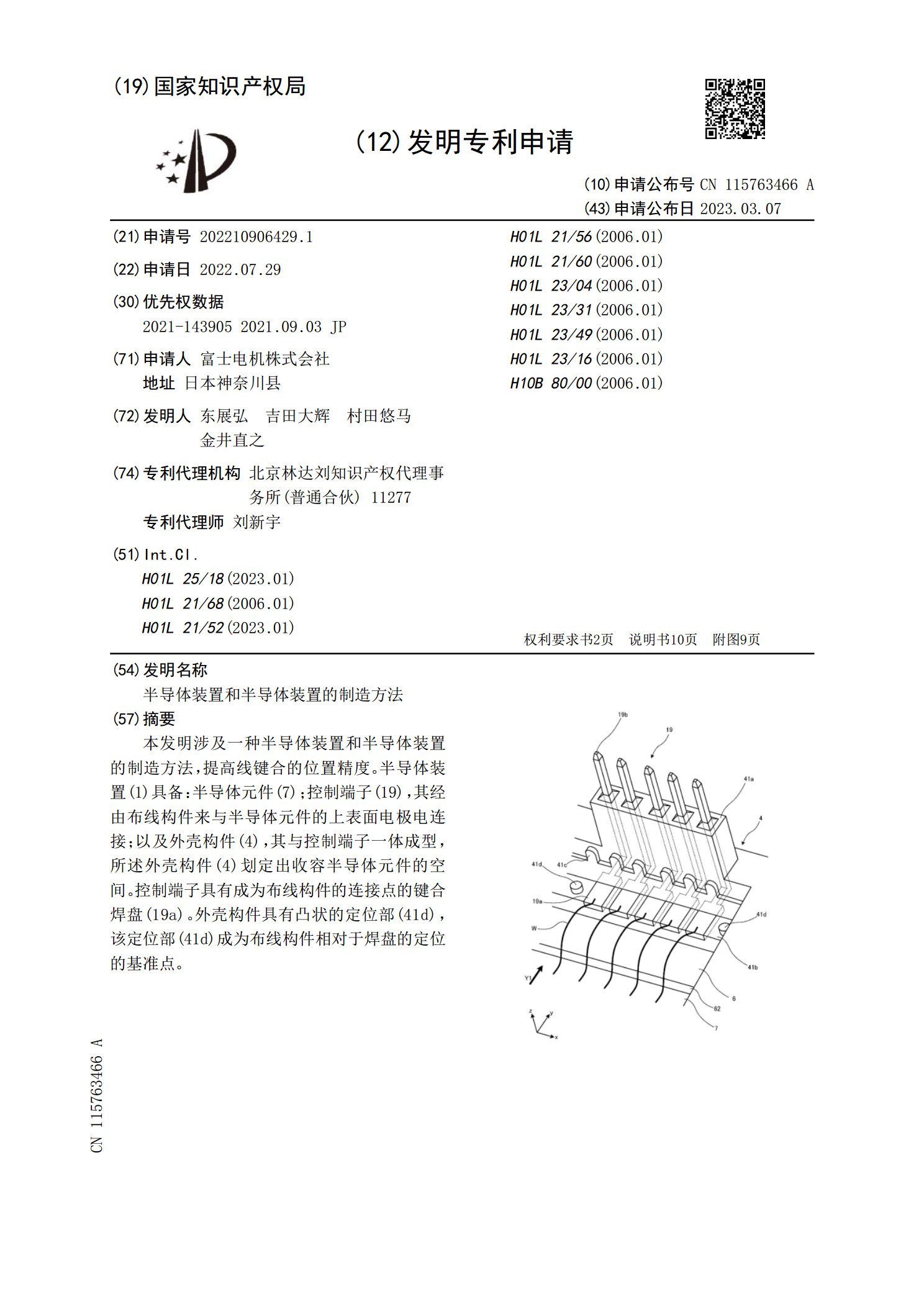

本发明涉及一种半导体装置和半导体装置的制造方法,提高线键合的位置精度。半导体装置(1)具备:半导体元件(7);控制端子(19),其经由布线构件来与半导体元件的上表面电极电连接;以及外壳构件(4),其与控制端子一体成型,所述外壳构件(4)划定出收容半导体元件的空间。控制端子具有成为布线构件的连接点的键合焊盘(19a)。外壳构件具有凸状的定位部(41d),该定位部(41d)成为布线构件相对于焊盘的定位的基准点。