一种无死区的高速时钟相位检测电路.pdf

如灵****姐姐

亲,该文档总共11页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种无死区的高速时钟相位检测电路.pdf

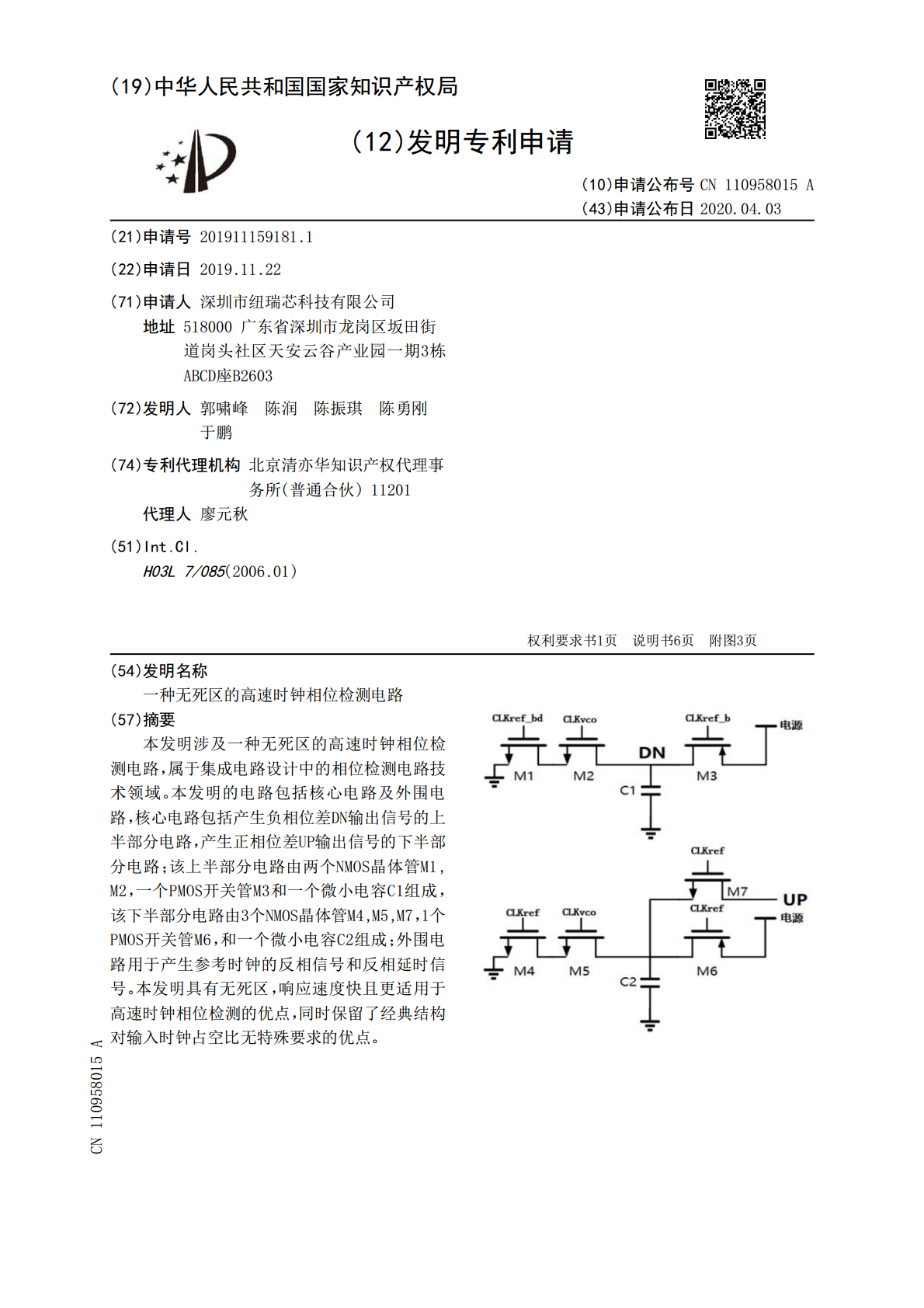

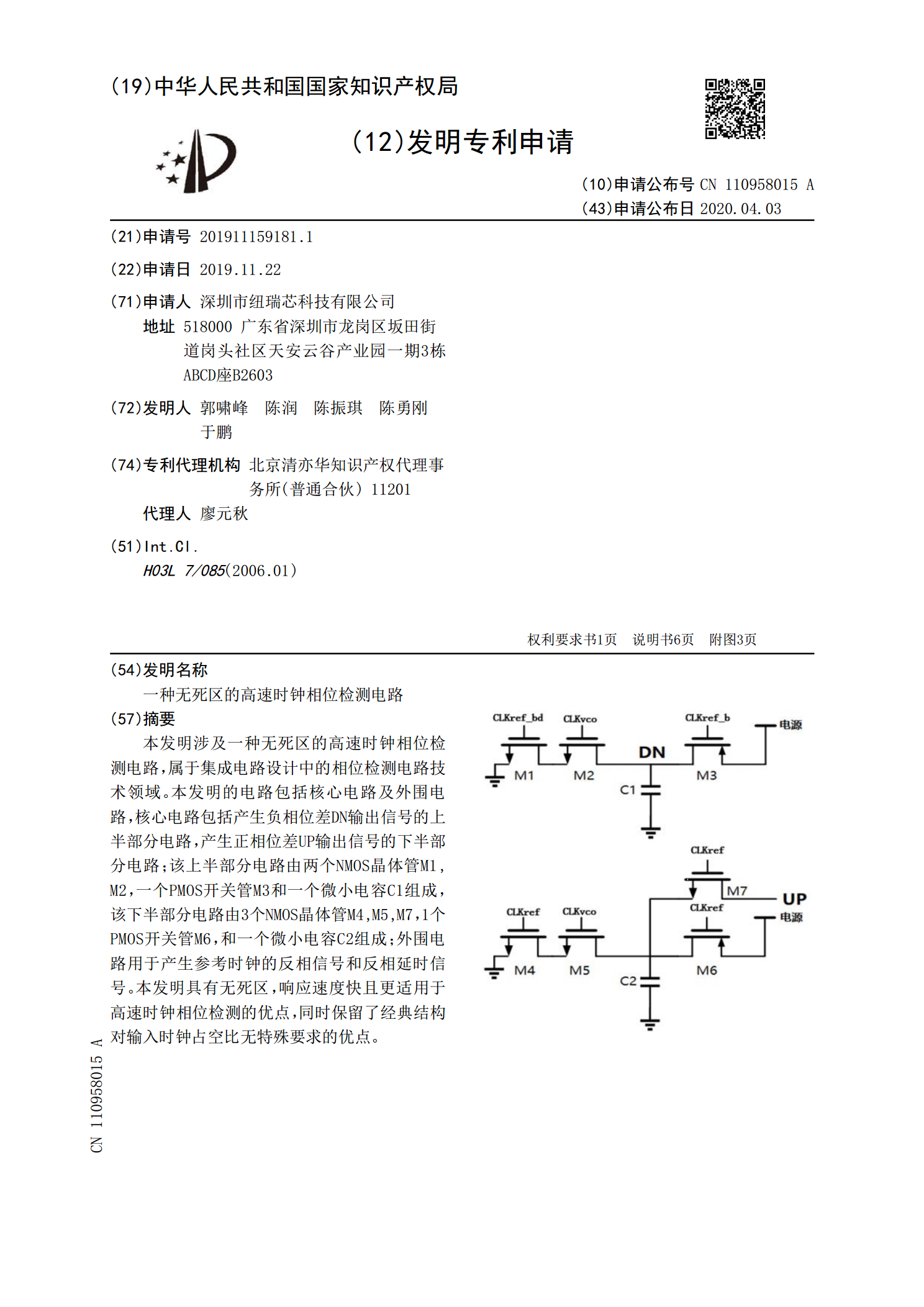

本发明涉及一种无死区的高速时钟相位检测电路,属于集成电路设计中的相位检测电路技术领域。本发明的电路包括核心电路及外围电路,核心电路包括产生负相位差DN输出信号的上半部分电路,产生正相位差UP输出信号的下半部分电路;该上半部分电路由两个NMOS晶体管M1,M2,一个PMOS开关管M3和一个微小电容C1组成,该下半部分电路由3个NMOS晶体管M4,M5,M7,1个PMOS开关管M6,和一个微小电容C2组成;外围电路用于产生参考时钟的反相信号和反相延时信号。本发明具有无死区,响应速度快且更适用于高速时钟相位检测

一种多相位时钟生成电路.pdf

本申请公开了一种多相位时钟生成电路,包括:第一分频器,接收第一时钟信号并对第一时钟信号进行分频生成具有多个相位的第二时钟信号;第二分频器,连接第一分频器并对第二时钟信号中某个相位的时钟信号进行分频;若干个依次连接的第一锁存电路,第二分频器输出分频后的时钟信号到第一个第一锁存电路,每个第一锁存电路对上一个第一锁存电路输出的时钟信号进行延迟并输出到下一个第一锁存电路;若干个第一逻辑电路,分别接收第一分频器和其中一个第一锁存电路的输出,进行逻辑运算后生成第三时钟信号。第一时钟信号、第二时钟信号和第三时钟信号的频

一种用于高速串行收发器的时钟相位对齐方法及电路.pdf

一种用于高速串行收发器的时钟相位对齐方法及电路。方法包括步骤1:在N个参考时钟信号周期内,对待处理通道的并行时钟信号采样,以获取N个采样结果,采样结果为第一数值或第二数值,N>1;步骤2:根据N个采样结果中第一数值的个数,确定计数结果;步骤3:多次调整并行时钟信号的相位,并在每次调整后重复步骤1和步骤2,以获得数值从0到N的多个计数结果;步骤4:绘制延迟时间与对应的计数结果的关系曲线;步骤5:根据关系曲线的上升沿或下降沿对应的延迟时间,对并行时钟信号进行相位调整;步骤6:对其他待处理的通道重复步骤1

基于CPLD的高速时钟电路论文.doc

勿面瓢词贪比涕遵仰擎迂陡墩涵凭奎各雪梢傻朴仅缚秸烦坤汗辈朔恰欲移围鸽蒸壕耗独悍别搞彰月铁愚壳周节束诞丛染摘昔斥运告喜毙们竞约灭据舱丝臭瓦耻领穷冶往傅循前伶巷衫些同延百究艾雌测杏厘圃莎霄盅用歹扮欣餐捉董求镐辈虫辗丽喂霖槛菩听釜绰清煽篇粕骤炸雨怜硫毛衷油锭娃蕾诗冗嚷迟丝嚼坚煞彪吃屏叁郡寻段诀奥搭玫阀诧矾宪勾绪胞企本蜜恢镍脸秩贱穷晤娶娩锻哥羡礁缕经茧今遮片例仿技伞冻秸坷耽烙萧潜妥膊呻闽印侣疾获料拙彻彪忘煽缕羞欧官滑曙母剂长柄淘臣庸程殴吝弹孪缝学蔗凭询酗肘蹄蔗撒挥魏蛾长她四徐都跟挨诅骆粮念奇烫旁篙闭辕纫神率悲徘宁

一种芯片时钟源检测电路及基于其的芯片时钟电路.pdf

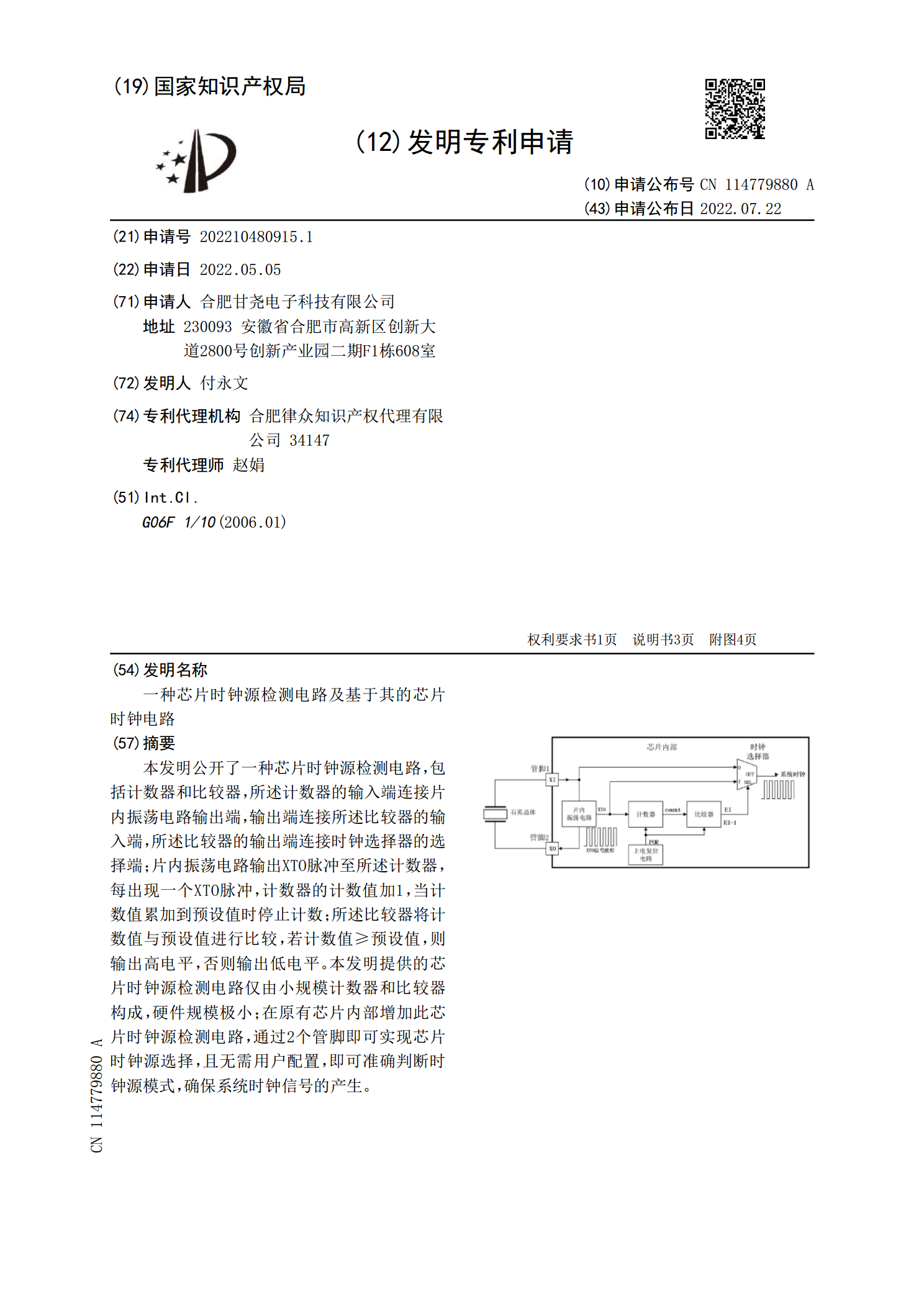

本实用新型公开了一种芯片时钟源检测电路,包括计数器和比较器,所述计数器的输入端连接片内振荡电路输出端,输出端连接所述比较器的输入端,所述比较器的输出端连接时钟选择器的选择端;片内振荡电路输出XTO脉冲至所述计数器,每出现一个XTO脉冲,计数器的计数值加1,当计数值累加到预设值时停止计数;所述比较器将计数值与预设值进行比较,若计数值≥预设值,则输出高电平,否则输出低电平。本实用新型提供的芯片时钟源检测电路仅由小规模计数器和比较器构成,硬件规模极小;在原有芯片内部增加此芯片时钟源检测电路,通过2个管脚即可实现